NAND會出錯

糾錯能力是一個SSD質量的重要指標。最開始的NAND 每個存儲單元只放一個bit,叫SLC,后來又有了MLC,現在的主流的是TLC。存儲密度不斷增加的同時,器件尺寸變小,存儲單元電氣耦合性變得很復雜。比如氧化層變得很薄,比如讀取單個bit需要的讀電壓控制能力更精密等,總的來說,NAND flash更容易出錯了,或者說NAND 上的噪聲增加了。

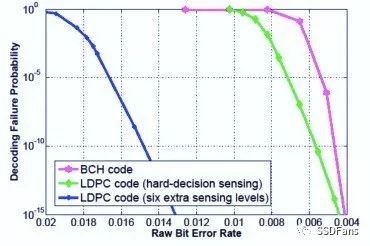

RBER (Raw Bit Error Rate)是衡量NAND質量的重要參數。給定RBER,可以比較各種糾錯算法的有效性。

圖1 曲線從右到左依次是BCH,LDPC 硬判決算法,LDPC 軟判決法,縱軸表示糾錯失敗的概率,橫軸表示RBER

可以看到,LDPC 軟判決算法由于有更多的信道信息,相對于BCH 和硬判決LDPC 算法更有優勢。所以目前主流的SSD 控制器都采用LDPC 作為糾錯算法。

NAND糾錯模型

NAND的基本特性,請參閱第三章。我們存儲進NAND的信息通過電子儲存起來,讀的時候通過探測器件儲存的電子多少來恢復數據。

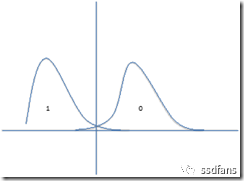

信息0和1在NAND 上的電子分布圖(示意圖)如下圖所示為,以slc 為例。這個分布可以通過大量數據探測出來的。豎直的線,表示此時讀取NAND的閾值電壓。可見,對于1的概率分布在閾值電壓右側的將會被NAND硬判決成0,從而導致bit翻轉。

圖2 Slc 兩種狀態的概率分布示意圖,橫坐標對應閾值電壓。

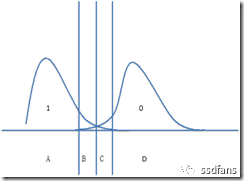

通過調節不同的閾值電壓來對NAND 進行多次讀取,可以獲得額外的信息(得到閾值電壓在哪個區間),如下圖所示。利用概率論的知識,可以建立統計模型。

圖3 多次調整讀取電壓

假設寫入的信息為X,X取值{0,1},其閾值電壓為Y, 調節讀取電壓后將閾值電壓分成了4個區間A, B, C,D

已知條件概率密度函數p(Y|X) = f(Y,X)如上圖所示。左右分別為p(Y|X=1)和 p(Y|X=0)的曲線。根據之前BP算法章節的介紹,我們感興趣的是:

P(X|A), P(X|B), P(X|C), 和 P(X|D)。知道這幾個概率后,BP 這樣的LDPC 的軟判決算法就可以工作了。根據前面對條件概率和貝葉斯公式的復習,求解個問題應該不難,交給讀者研究。

LDPC糾錯流程

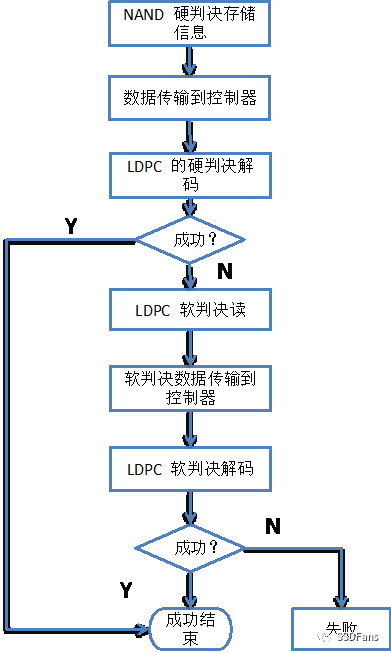

LDPC在SSD中的糾錯流程如下圖所示,值得注意的是,NAND硬判決,數據傳輸到控制器,以及硬判決解碼這幾個過程的速度都很快。軟判決要讀很多次,傳輸數據很多次,所以對SSD的性能產生不好的影響。

圖4 LDPC 糾錯流程

為了提高性能,一種普遍的優化是,把LDPC的軟判決的分辨率變成動態可調,這樣只有最壞的情況下,才需要最高的分辨率去讀。這樣在大部分情況下,軟判決讀和軟判決傳輸數據的時間開銷大大變小。

-

LDPC

+關注

關注

1文章

66瀏覽量

31204 -

SSD

+關注

關注

21文章

2863瀏覽量

117472

原文標題:LDPC 在SSD中的應用

文章出處:【微信號:SSDFans,微信公眾號:SSDFans】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

PCB加工流程詳解大全

一種通用的低成本QC-LDPC碼譯碼結構

怎樣設計基于CMMB系統的LDPC譯碼器?

LDPC原理與應用

符合中國數字電視地面廣播標準的前向糾錯碼編碼器設計

規則LDPC碼的密度進化方法及其高斯近似

LDPC碼在無線局域網中的應用分析

Xilinx宣布推出LDPC糾錯IP基礎,為云端和數據中心存儲市場實現新一代閃存應用

向量子密鑰分發的自適應LDPC雙碼并行機制

基于二分圖構造LDPC碼的校驗矩陣算法及性能分析

基于衛星通信的多元域LDPC碼研究

LDPC在SSD中的糾錯流程詳解

LDPC在SSD中的糾錯流程詳解

評論