高速數據傳輸系統在通信系統、測試儀器等電子系統中有著廣泛應用,人們對數據傳輸的處理速度、可靠性及實時性的要求越來越高,數據傳輸速度越來越快,對數據的抗干擾性的要求也越來越高。

01

USB3.0簡介

USB3.0的最高理論速度達到了5Gbit/s,向需要更大電力支持的設備提供更好的支持和電力供應,它在USB2.0的基礎上增加了新的電源管理功能,采用全雙工數據通信,提供更快的傳輸速度,并且向下兼容USB2.0和USB1.1設備。USB體系主要包括三個部分:主機,設備和物理連接。主機通常是PC或者主機控制器;設備是指常用的U盤、帶USB的攝像頭、相機等設備;物理連接就是通常用的傳輸線,在USB3.0系統中,采用了對偶單純形四線制差分信號線,因此可以支持雙向并發數據流傳輸,這也是USB3.0相比于USB2.0設備速度提升的關鍵因素。

02

系統硬件設計

2.1 USB3.0高速傳輸模塊

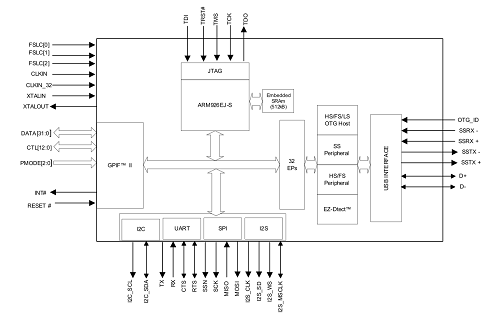

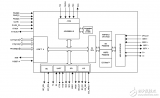

本設計采用的賽普拉斯EZ-USB FX3 CYUSB3014是新一代的USB 3.0外設控制器,其數據傳輸速率可達320MBps,具有高度集成的靈活特性,滿足本設計的高速數據傳輸要求。其USB3.0模塊功能框圖如下圖1所示。

圖_1_USB3_0模塊功能框圖

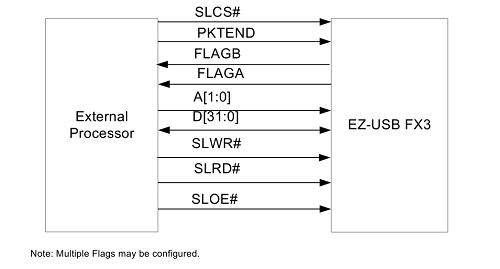

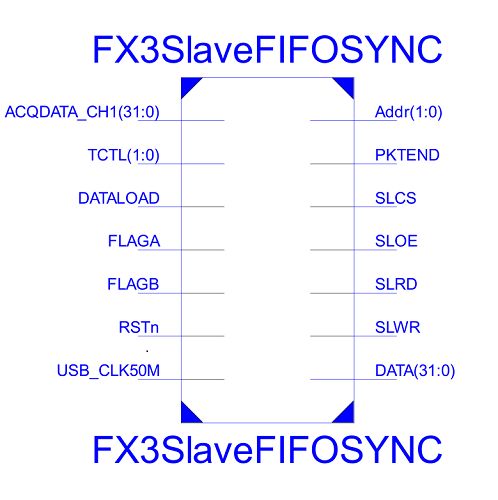

本設計中,將USB3.0模塊作為從器件,從器件FIFO接口如圖2所示。該接口允許外部處理器直接訪問多達4個EZ-USB FX3內部緩沖區。USB3.0的控制交由FPGA,數據輸出到PC機進行接收。

圖_2_USB3_0從器件FIFO接口

2.2 FPGA主控模塊

本設計的主控模塊采用Xilinx公司的Spartan6系列FPGA,型號為XC6SLX9-2FTG256C,256個引腳的FBGA封裝。開發板配置兩路標準的AX擴展口,一共有34*2=68個IO口,用于外接其他模塊。

將USB3.0模塊的控制及數據引腳,使用杜邦線與FPGA的擴展口相連,通過對FPGA進行Verilog程序配置,來控制USB3.0的工作。實物連接如下圖3所示。

圖_3_FPGA+USB3.0模塊實物連接圖

03

系統程序設計

3.1 USB3.0模塊程序設計

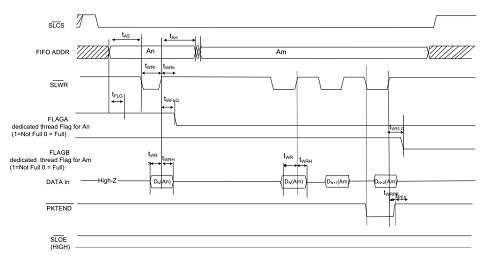

本設計以FPGA為主控模塊,通過Verilog程序配置USB3.0模塊的工作模式。設計中將廠商提供的固件寫入到該模塊,將其配置為異步、32位并行高速讀寫方式。在下位機采用異步從器件FIFO寫入模式,其時序圖如下圖4所示。

圖_4_異步從器件FIFO寫入模式

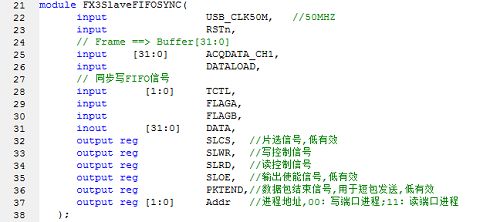

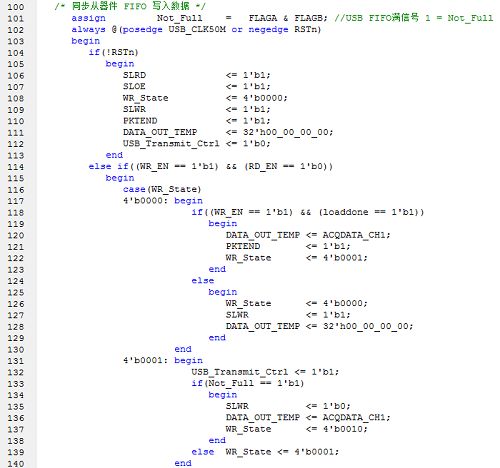

對USB3.0模塊進行Verilog程序設計,其核心關鍵代碼如下。USB3.0模塊接口程序如圖5所示。

圖_5_USB3_0模塊接口程序

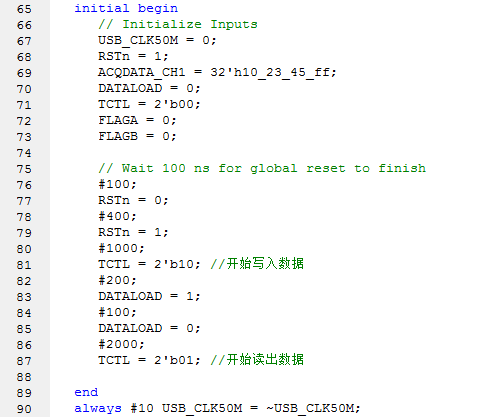

USB3.0模塊寫入數據程序如下圖6所示。

圖_6_USB3_0模塊寫入數據程序1

通過理解USB3.0相關手冊,完成程序設計后,綜合該模塊,得到頂層RTL原理圖,如下圖7所示。

圖_7_USB3_0綜合頂層模塊原理圖

3.2 程序仿真驗證

設計好上述程序后,繼續編寫仿真激勵文件,對該模塊進行仿真測試。測試核心代碼如下圖8所示。

圖_8_USB3_0仿真測試源代碼

仿真驗證結果如下圖9所示,可見輸入數據正確控制,寫入到該模塊的FIFO中。

圖_9_USB3_0仿真驗證結果

3.3 系統實物測試

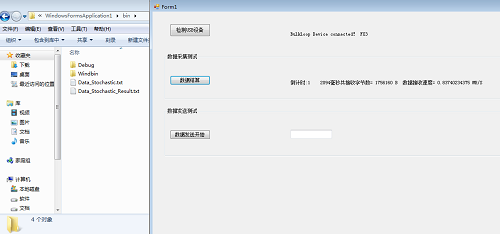

完成對程序的仿真驗證后,將USB3.0的數據輸出端口連接到PC機,使用接收軟件進行數據接收。軟件運行測試過程如下圖10所示,首先與USB3.0建立連接,然后再啟動數據接收。

圖_10_上位機數據接收測試

04

總結

本設計的傳輸系統有很多優點,通過USB3.0接口的超高速傳輸特性,可有效地解決高速數據采集中的數據傳輸和存儲問題,測量結果誤差小,可信度高,有利于實現數據的實時處理。采用Cypress公司的USB3.0專用接口芯CYUSB3014與FPGA連接完成了采樣數據的高速傳輸測試,經過多次測試,USB3.0接口的準確、超高速、實時等性能得到了充分的體現。

-

控制器

+關注

關注

112文章

16332瀏覽量

177806 -

電源管理

+關注

關注

115文章

6177瀏覽量

144443 -

usb

+關注

關注

60文章

7936瀏覽量

264474

原文標題:基于FPGA的USB3.0接口設計

文章出處:【微信號:gh_873435264fd4,微信公眾號:FPGA技術聯盟】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

新一代的USB 3.0外設控制器

新一代的USB 3.0外設控制器

評論