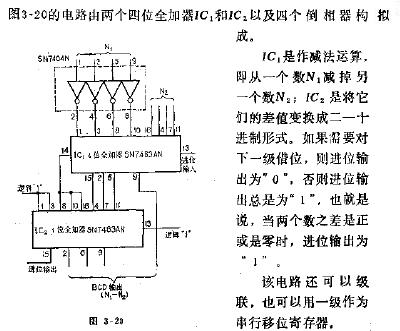

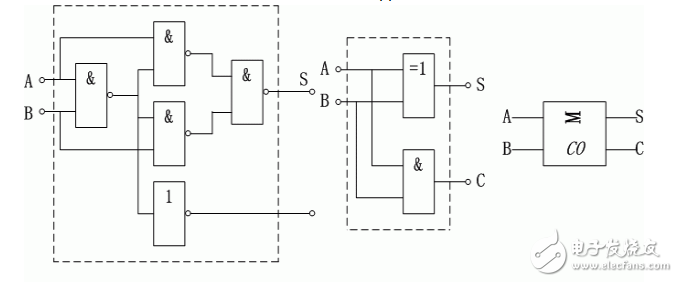

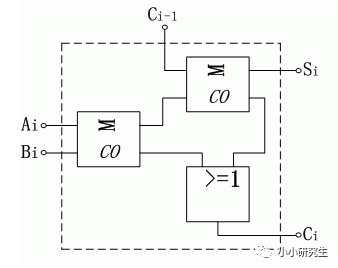

兩個半加器組成全加器的做法

用門電路實現兩個二進數相加并求出和的組合線路,稱為一個全加器。

全加器是能夠計算低位進位的二進制加法電路

一位全加器(FA)的邏輯表達式為:

S=A⊕B⊕Cin

Co=AB+BCin+ACin

其中A,B為要相加的數,Cin為進位輸入;S為和,Co是進位輸出;

如果要實現多位加法可以進行級聯,就是串起來使用;比如32位+32位,就需要32個全加器;這種級聯就是串行結構速度慢,如果要并行快速相加可以用超前進位加法。

全加器和半加器的應用

應用原理

計算機最基本的任務之一是進行算數,在機器中四則運算——加、減、乘、除——都是分解成加法運算進行的,因此加法器便成為計算機中最基本的運算單元。

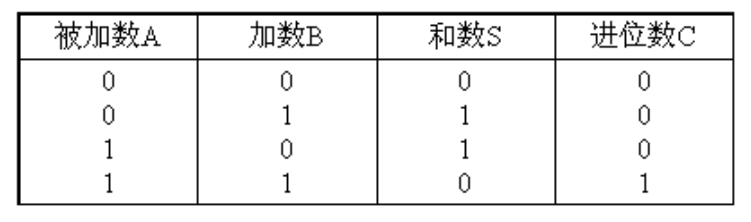

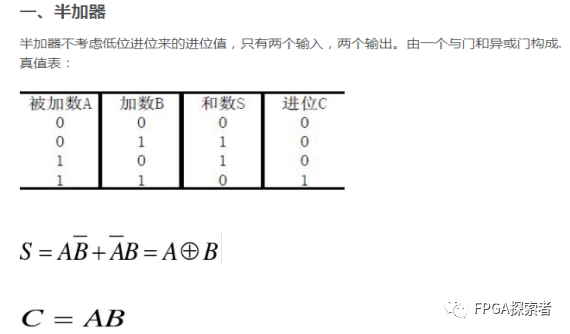

半加器原理?

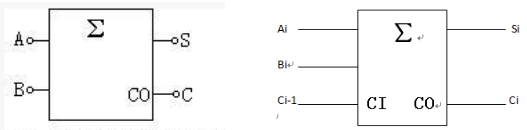

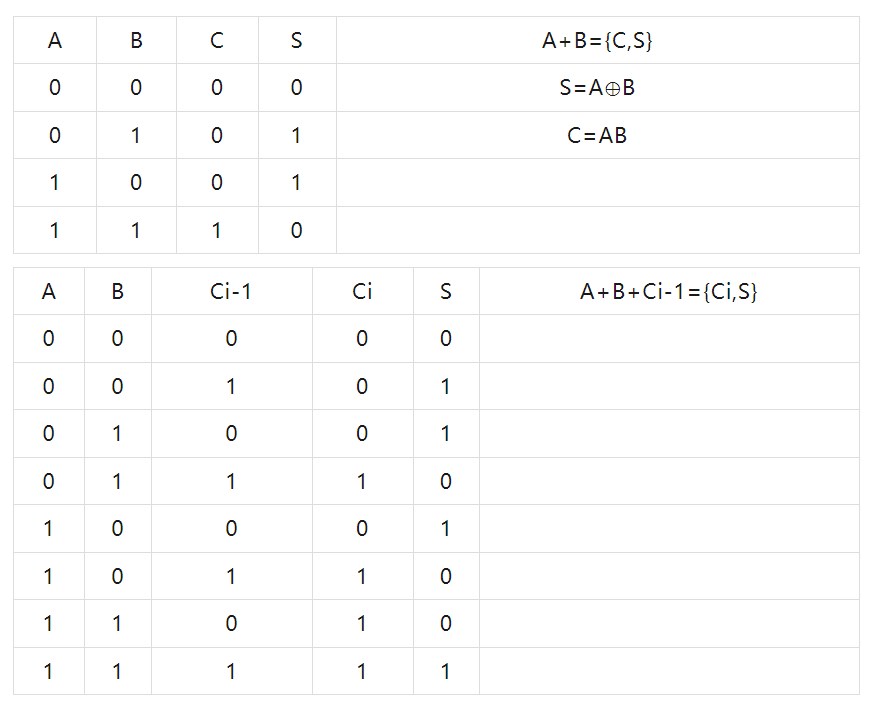

兩個二進制數相加,叫做半加,實現半加操作的電路,稱為半加器。表2.6.1是半加器的真值表,圖a為半加器的符號,A表示被加數,B表示加數,S表示半加和,C表示向高位的進位。?

從二進制數加法的角度看,真值表中只考慮了兩個加數本身,沒有考慮低位來得進位,這就是半加器的由來。由真值表可得半加器邏輯表達式

(a)半加器符號 (b)全加器符號

全加器原理?

全加器能進行加數、被加數和低位來的進位信號相加,并根據求和的結果給出該位的進位信號。圖b為全加器的符號,如果用Ai,Bi表示A,B兩個數的第i位,Ci-1表示為相鄰低來的進位數,Si表示為本位和數(成為全加和),Ci表示為相鄰高位的進位數。可以很容易的求出S、C的簡化函數表達式。表2.6.2是全加器的真值表?

用一位全加器可以構成多位加法電路。由于每一位加法的結果必須等到低一位的進位產生后才能產生(這種結構稱為串行進位加法器),因而運算速度很慢。為了提高運算速度,制成了超前進位那加法器。這種電路各進位信號的產生只需經歷一級與非門和一級或非門的延遲時間,比串行進位的全加器大大縮短了時間。

1.實現半加/半減器

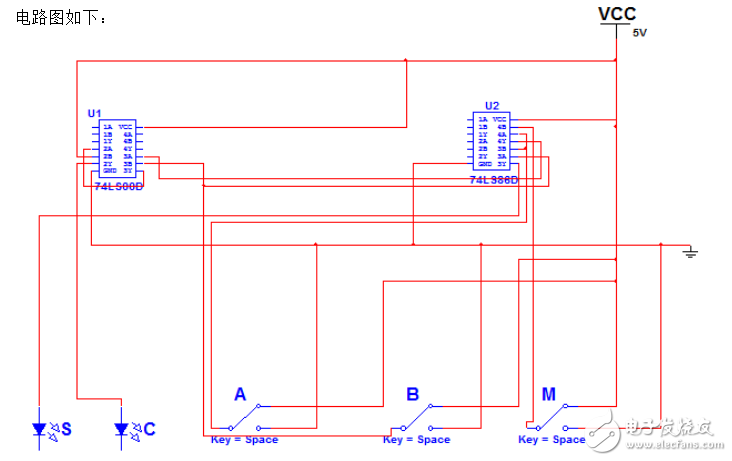

用異或門74LS86和與非門74LS00組成半加%2F半減器,當控制信號M%3D0時實現半加器功能,當控制信號M%3D1時實現半減器功能。

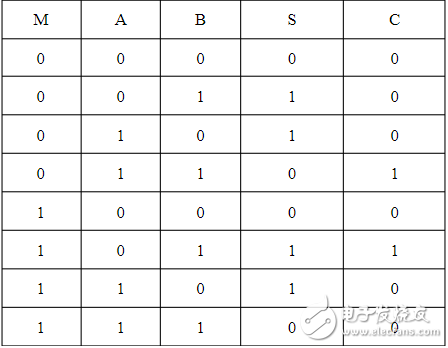

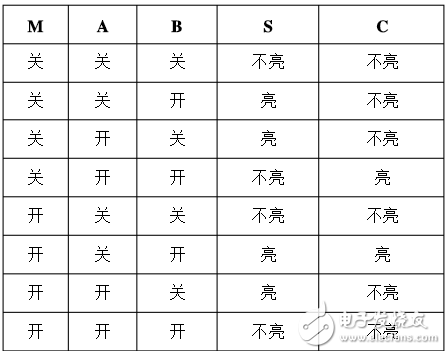

半加/半減器真值表

結果:

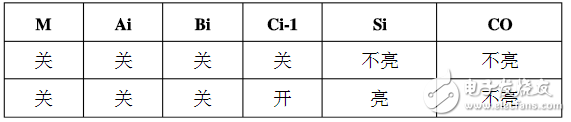

注意:開關開表示輸入1,關表示輸入0。燈亮表示輸出1,不亮表示0。

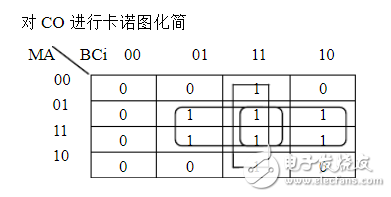

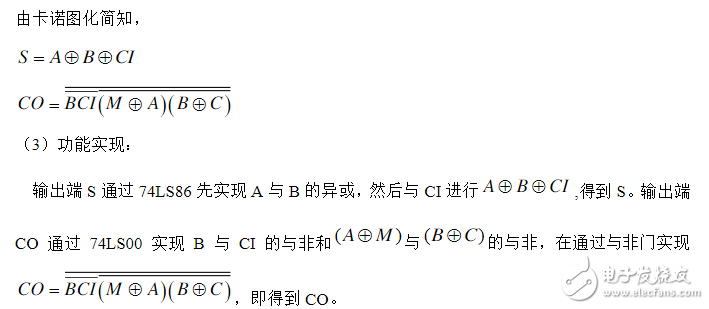

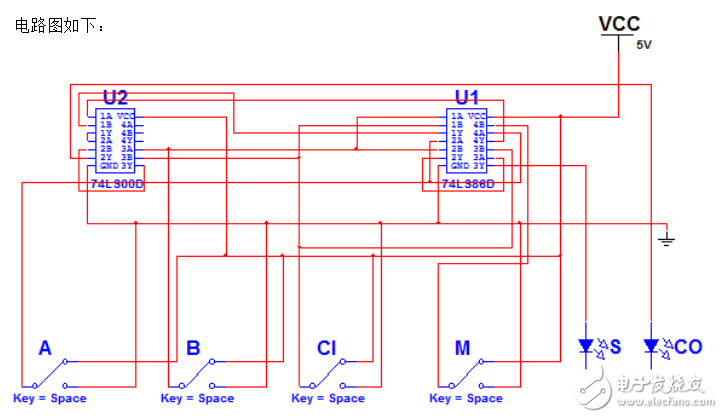

2.實現全加/全減器

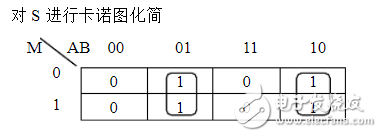

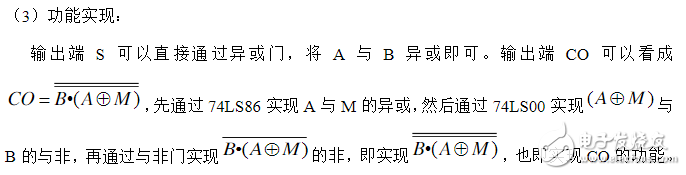

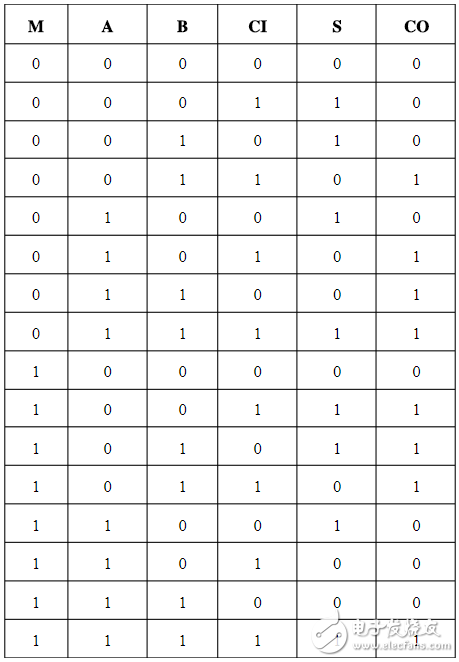

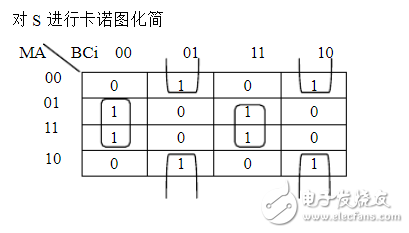

用74LS86和若干與非門組成全加%2F全減器,當控制信號M%3D0時實現全加器功能,當控制信號M%3D1時實現全減器功能。要求設計的邏輯電路門數量最少。

全加/全減器真值表

結果:

結論:通過開關控制輸入,觀察輸出信號燈的亮與滅符合真值表。

-

全加器

+關注

關注

10文章

62瀏覽量

28847 -

半加器

+關注

關注

1文章

29瀏覽量

8983

發布評論請先 登錄

評論