全加器

全加器英語名稱為full-adder,是用門電路實現兩個二進制數相加并求出和的組合線路,稱為一位全加器。一位全加器可以處理低位進位,并輸出本位加法進位。多個一位全加器進行級聯可以得到多位全加器。常用二進制四位全加器74LS283。

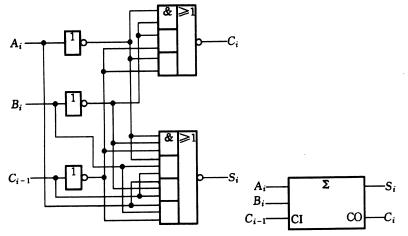

全加器是組合邏輯電路中最常見也最實用的一種,考慮低位進位的加法運算就是全加運算,實現全加運算的電路稱為全加器。而其功能設計可以根據組合邏輯電路的設計方法來完成。通過邏輯門、74LS138譯碼器、74LS153D數據選擇器來實現一位全加器的電路設計,并且實現擴展的兩位全加器電路。并且Multisim是一個專門用于電路設計與仿真的工具軟件。它以界面形象直觀、操作方便、分析功能強大、易學易用等突出優點,迅速被推廣應用。

全加器工作原理

全加器是能夠計算低位進位的二進制加法電路。與半加器相比,全加器不只考慮本位計算結果是否有進位,也考慮上一位對本位的進位,可以把多個一位全加器級聯后做成多位全加器.

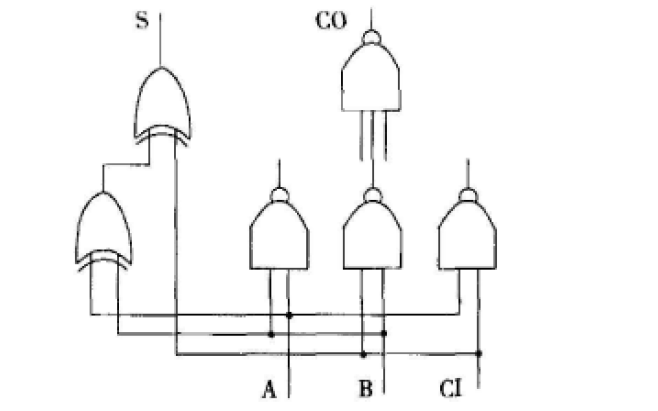

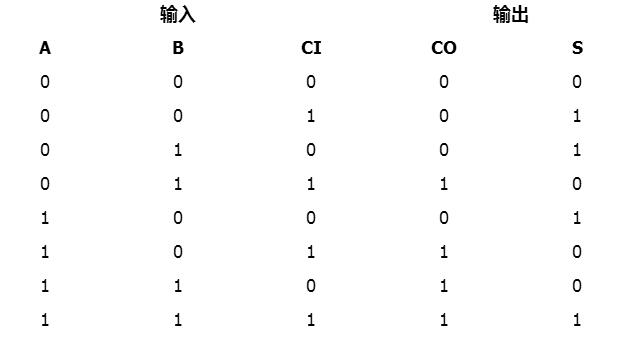

一位全加器的真值表如下圖,其中Ai為被加數,Bi為加數,相鄰低位來的進位數為Ci-1,輸出本位和為Si。向相鄰高位進位數為Ci

描述+一位全加器的表達式如下:

Si=Ai⊕Bi⊕Ci-1

第二個表達式也可用一個異或門來代替或門對其中兩個輸入信號進行求和:

-

邏輯電路

+關注

關注

13文章

494瀏覽量

42610 -

全加器

+關注

關注

10文章

62瀏覽量

28496

發布評論請先 登錄

相關推薦

FPGA入門——1位全加器設計 精選資料分享

什么是8位全加器和8為帶超前進位的全加器?

全加器譯碼器及顯示電路實驗

全加器是什么?全加器和半加器的區別?

高性能CMOS全加器設計的詳細資料說明

全加器的真值表

Verilog數字系統設計——復雜組合邏輯實驗2(8位全加器和8為帶超前進位的全加器)

什么是全加器 全加器工作原理

什么是全加器 全加器工作原理

評論