DARPA今年會議聚焦于集成線路設計,為美國半導體產業在摩爾定律走向極限后做未雨綢繆。

美國DARPA(Defense Advanced Research Projects Agency)的今年會議剛結束,與去年不同的是今年的議題高度集中于線路設計,預計要在5年內投入15億美元的研發預算,目標是2025至2030年有機會可以開展的技術。

DARPA是一個聚焦大學、企業、國家實驗室研究方向的機構,雖然它帶有濃厚的國防戰略色彩,但是對于民用科技也多次產生深遠的影響,譬如已成現代文明基石的Internet,就是由其發展出的ARPANET與IBM的Bitnet所整合出的架構。

在集成線路設計方面的題目大致有下列幾個:芯片架構(architecture)的變更、新設計流程、機器學習的自動化電路設計(EDA)、開源硬件IP以及3D單片堆疊(monolithic stacking)。

芯片架構的變更包括過去已開始著手的基礎層次變更,譬如記憶體存取型態的更新,還有軟件定義的硬件(software-defined hardware)。軟件定義的硬件是指硬件可以預知要處理數據的種類,因而可以重新配置(reconfigure)線路,變成該數據的有效率處理器。另外還有特定領域系統芯片(domain specific system-on-chip),目的在于在建立基礎架構讓一已配備特定資源的芯片能被更廣泛的使用。

新設計流程的目的是要讓用極精簡的人力就能設計以前大團隊才能設計的芯片,用的方法是使用抽象化和自動化的高階程式設計系統芯片。除了大幅降低設計人力資源門檻外,還很容易變更設計,并且能在不同制程平臺上搬動。Synopsis、Cadence、Mentor均參加此一計劃。

機器學習的自動化電路設計是另一項可以精簡人力資源或者是提高生產力的計劃。當設計工程師以自動化電路設計工具設計集成線路時,機器學習也跟著學習設計。初步探討的結果,此一概念可行。由于機器學習需要大數據,云的布建是基礎工程。

硬件IP的建立是半導體行之有年的做法,但是開源的硬件IP則是另一回事。在半導體制程與設計日益復雜的環境下,硬件IP有可能步上軟件的后塵、走向開源,節省產業對于驗證個別硬件IP所需下的工夫,集中精力于線路與功能的創新。

3D單片堆疊比3D封裝在性能上更勝一籌,用不是太先進的制程的3D單片堆疊芯片也有機會能在性能和成本上和用最先進的制程設計生產的芯片比肩齊步,對于老舊晶圓廠相當有幫助。

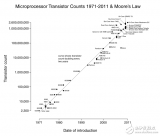

DARPA的這些計劃基本上都是對美國半導體產業在摩爾定律長日將盡時分的未雨綢繆。如果制程微縮不能再創造經濟價值,何以為繼?這些計劃就是嘗試方向。另一個更明白的議程是競爭,畢竟DARPA是Sputnik衛星發射后的回應,其議程就不言而喻了。

-

摩爾定律

+關注

關注

4文章

634瀏覽量

78999 -

DARPA

+關注

關注

4文章

72瀏覽量

27826

原文標題:【名家專欄】后摩爾定律的線路設計創新

文章出處:【微信號:DIGITIMES,微信公眾號:DIGITIMES】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

摩爾定律也適用于EPON芯片商用之路?

半導體行業的里程碑“摩爾定律”竟是這樣來的

摩爾定律推動了整個半導體行業的變革

IC芯片的密度和計算機的速度能夠一直按照摩爾定律前行嗎?

摩爾定律,摩爾定律是什么意思

摩爾定律的歷程

盤點DARPA對摩爾定律長日將盡時分的未雨綢繆

盤點DARPA對摩爾定律長日將盡時分的未雨綢繆

評論