JTAG有10pin的、14pin的和20pin的,盡管引腳數(shù)和引腳的排列順序不同,但是其中有一些引腳是一樣的,各個(gè)引腳的定義如下。

一、引腳定義

Test Clock Input (TCK) -----強(qiáng)制要求1

TCK在IEEE1149.1標(biāo)準(zhǔn)里是強(qiáng)制要求的。TCK為TAP的操作提供了一個(gè)獨(dú)立的、基本的時(shí)鐘信號(hào),TAP的所有操作都是通過(guò)這個(gè)時(shí)鐘信號(hào)來(lái)驅(qū)動(dòng)的。

Test Mode Selection Input (TMS) -----強(qiáng)制要求2

TMS信號(hào)在TCK的上升沿有效。TMS在IEEE1149.1標(biāo)準(zhǔn)里是強(qiáng)制要求的。TMS信號(hào)用來(lái)控制TAP狀態(tài)機(jī)的轉(zhuǎn)換。通過(guò)TMS信號(hào),可以控制TAP在不同的狀態(tài)間相互轉(zhuǎn)換。

Test Data Input (TDI) -----強(qiáng)制要求3

TDI在IEEE1149.1標(biāo)準(zhǔn)里是強(qiáng)制要求的。TDI是數(shù)據(jù)輸入的接口。所有要輸入到特定寄存器的數(shù)據(jù)都是通過(guò)TDI接口一位一位串行輸入的(由TCK驅(qū)動(dòng))。

Test Data Output (TDO) -----強(qiáng)制要求4

TDO在IEEE1149.1標(biāo)準(zhǔn)里是強(qiáng)制要求的。TDO是數(shù)據(jù)輸出的接口。所有要從特定的寄存器中輸出的數(shù)據(jù)都是通過(guò)TDO接口一位一位串行輸出的(由TCK驅(qū)動(dòng))。

Test Reset Input (TRST) ----可選項(xiàng)1

這個(gè)信號(hào)接口在IEEE 1149.1標(biāo)準(zhǔn)里是可選的,并不是強(qiáng)制要求的。TRST可以用來(lái)對(duì)TAPController進(jìn)行復(fù)位(初始化)。因?yàn)橥ㄟ^(guò)TMS也可以對(duì)TAP Controll進(jìn)行復(fù)位(初始化)。所以有四線JTAG與五線JTAG之分。

(VTREF) -----強(qiáng)制要求5

接口信號(hào)電平參考電壓一般直接連接Vsupply。這個(gè)可以用來(lái)確定ARM的JTAG接口使用的邏輯電平(比如3.3V還是5.0V?)

Return Test Clock ( RTCK) ----可選項(xiàng)2

可選項(xiàng),由目標(biāo)端反饋給仿真器的時(shí)鐘信號(hào),用來(lái)同步TCK信號(hào)的產(chǎn)生,不使用時(shí)直接接地。

System Reset ( nSRST)----可選項(xiàng)3

可選項(xiàng),與目標(biāo)板上的系統(tǒng)復(fù)位信號(hào)相連,可以直接對(duì)目標(biāo)系統(tǒng)復(fù)位。同時(shí)可以檢測(cè)目標(biāo)系統(tǒng)的復(fù)位情況,為了防止誤觸發(fā)應(yīng)在目標(biāo)端加上適當(dāng)?shù)纳侠?a target="_blank">電阻。

USER IN

用戶自定義輸入。可以接到一個(gè)IO上,用來(lái)接受上位機(jī)的控制。

USER OUT

用戶自定義輸出。可以接到一個(gè)IO上,用來(lái)向上位機(jī)的反饋一個(gè)狀態(tài)

由于JTAG經(jīng)常使用排線連接,為了增強(qiáng)抗干擾能力,在每條信號(hào)線間加上地線就出現(xiàn)了這種20針的接口。但事實(shí)上,RTCK、USER IN、USER OUT一般都不使用,于是還有一種14針的接口。對(duì)于實(shí)際開(kāi)發(fā)應(yīng)用來(lái)說(shuō),由于實(shí)驗(yàn)室電源穩(wěn)定,電磁環(huán)境較好,干擾不大。

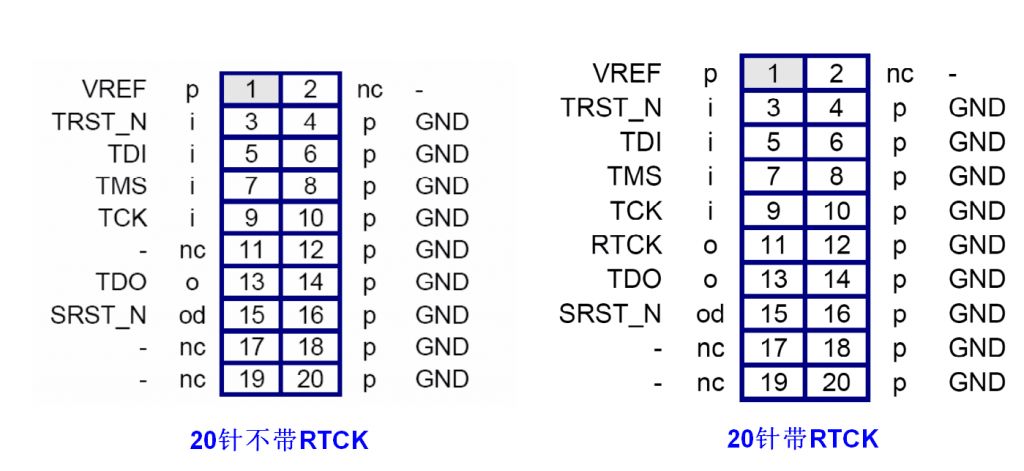

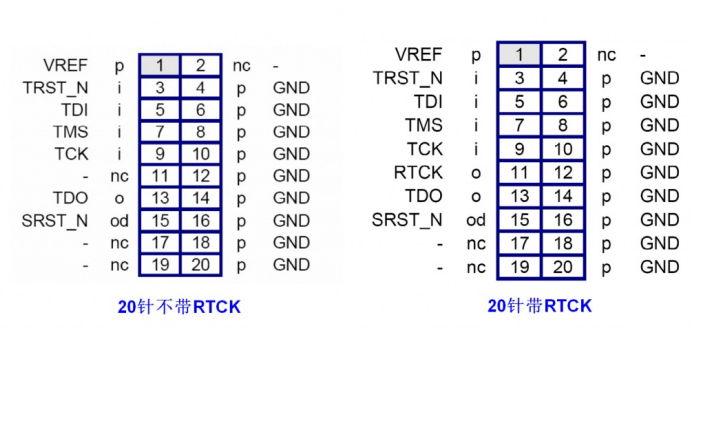

二、20、14、10pin JTAG的引腳名稱與序號(hào)對(duì)應(yīng)關(guān)系

值得注意的是,不同的IC公司會(huì)自己定義自家產(chǎn)品專屬的Jtag頭,來(lái)下載或調(diào)試程序。嵌入式系統(tǒng)中常用的20、14、10pin JTAG的信號(hào)排列如下:

需要說(shuō)明的是,上述Jtag頭的管腳名稱是對(duì)IC而言的。例如TDI腳,表示該腳應(yīng)該與IC上的TDI腳相連,而不是表示數(shù)據(jù)從該腳進(jìn)入download cable。

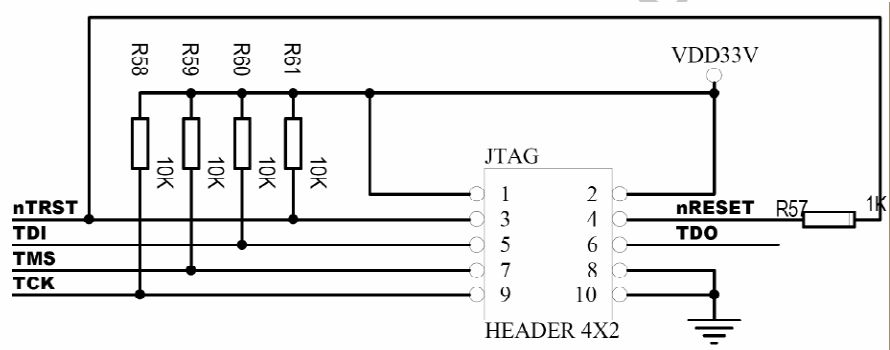

實(shí)際上10針的只需要接4根線,4號(hào)是自連回路,不需要接,1,2接的都是1管腳,而8,10接的是GND,也可以不接。

附轉(zhuǎn)接板電路:

-

寄存器

+關(guān)注

關(guān)注

31文章

5336瀏覽量

120232 -

JTAG

+關(guān)注

關(guān)注

6文章

399瀏覽量

71673 -

引腳

+關(guān)注

關(guān)注

16文章

1193瀏覽量

50412

原文標(biāo)題:干貨!JTAG各類接口針腳定義及含義

文章出處:【微信號(hào):gh_c472c2199c88,微信公眾號(hào):嵌入式微處理器】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

如何只顯示運(yùn)放的引腳序號(hào),不顯示運(yùn)放引腳的名稱

轉(zhuǎn):TI公司14-Pin JTAG規(guī)范以及參考原理圖

ADI-ADSP的JTAG菊花鏈,找仿真定義的時(shí)候?qū)W習(xí)了一下。

JTAG/ICSP是否有一個(gè)標(biāo)準(zhǔn)的或通用的引腳連接器

AD630仿真模型只有16pin與實(shí)物的20pin的對(duì)應(yīng)關(guān)系是什么?

ESP32-CAM PIN與GPIO引腳對(duì)應(yīng)關(guān)系

請(qǐng)問(wèn)ESP32-CAM PIN與GPIO引腳對(duì)應(yīng)關(guān)系是什么?

AD630的Pspice仿真模型只有16pin,與實(shí)物的20pin的對(duì)應(yīng)關(guān)系是什么?

JTAG各類接口針腳定義和含義是怎么樣的

20、14、10pin JTAG的引腳名稱與序號(hào)對(duì)應(yīng)關(guān)系

20、14、10pin JTAG的引腳名稱與序號(hào)對(duì)應(yīng)關(guān)系

評(píng)論