隨著物聯(lián)網(wǎng)(IoT)的快速發(fā)展,未來(lái)將會(huì)存在海量的數(shù)據(jù)。“大數(shù)據(jù)”時(shí)代,對(duì)數(shù)據(jù)的處理提出更高的需求。高性能處理器及集群能完成數(shù)據(jù)的實(shí)時(shí)處理。而在處理器與外設(shè)或處理器之間傳輸?shù)拇罅繑?shù)據(jù),對(duì)接口(Interface)技術(shù)也提出了更高的要求。就像一個(gè)人雖然有著聰明的頭腦,但神經(jīng)卻比較“長(zhǎng)”,就看起來(lái)就會(huì)很“呆笨”。目前主流并行接口技術(shù)就面臨著這樣的局面,越來(lái)越成為了瓶頸。

回顧接口技術(shù)發(fā)展歷史,其實(shí)數(shù)據(jù)的傳輸最開(kāi)始是低速的串行接口(Serial Interface,簡(jiǎn)稱串口),為了提高數(shù)據(jù)的總帶寬,首先想到的是增加數(shù)據(jù)傳輸位寬,再進(jìn)一步提升速率。也就是并行接口(Parallel Interface,簡(jiǎn)稱并口)的方式,并逐漸取代傳統(tǒng)低速串口成為主流。但隨著并口的發(fā)展,其限制也也越來(lái)越明顯。而高速串行(High Speed Serial,HSS)接口技術(shù)具有的優(yōu)勢(shì)使其有取代目前并口的趨勢(shì)。表現(xiàn)為接口總帶寬的顯著提升。其歷史就像圖1所示,從山間小道升級(jí)為鄉(xiāng)村公路,再到高速公路(網(wǎng)),能夠提供更高的通行量。

圖1

目前并口發(fā)展遇到的限制主要為,一方面芯片封裝面臨著IO數(shù)量緊張的問(wèn)題,另一方面是,并口的數(shù)據(jù)速率提升過(guò)程中面臨的串?dāng)_(Crosstalk)和噪聲(SSN)問(wèn)題,使得數(shù)據(jù)的同步變得很困難。這個(gè)問(wèn)題可以理解為,就像閱兵方陣,正步走起來(lái)英姿颯爽,這都需要很長(zhǎng)時(shí)間的訓(xùn)練。如果要求齊步跑起來(lái),也要橫豎成線(數(shù)據(jù)對(duì)齊同步),可真是難倒人啦。

圖2

串口和并口的交替發(fā)展演進(jìn),真可謂“三十年河?xùn)|,三十年河西”,技術(shù)并沒(méi)有對(duì)錯(cuò),“時(shí)勢(shì)造英雄”。

串口的典型代表就是在消費(fèi)電子和其他各領(lǐng)域中普遍使用的通用串行總線(Universal Serial Bus,USB);并口也有很多,比如DDR DRAM內(nèi)存接口,也就是人們常說(shuō)的DDR。

對(duì)于串口和并口那個(gè)速度快的問(wèn)題,這就要看怎么描述這個(gè)問(wèn)題了。

從線速率(linerate)來(lái)看,比如DDR3-1600的最大線速率為1600Mbps(也就是1.6Gbps)。那再看看目前主流的SerDes的線速率能達(dá)到多少那,Xilinx的16nm Ultrascale+FPGA提供的SerDes能夠達(dá)到32Gbps的速度。而最近Credo演示的雙模SerDes芯片,有112Gbps PAM4/56Gbps NRZ的性能表現(xiàn)。所以通常理解的高速串口比并口快,主要是從線速率的角度比較。

當(dāng)然從總數(shù)據(jù)帶寬的角度看,比如64bit DDR3-1600的最大數(shù)據(jù)帶寬也超過(guò)了100Gbps(64*1.6Gbps)。也能提供不俗的總帶寬表現(xiàn)。其實(shí)SerDes也可以多通道并行使用,比如像PCIe協(xié)議的x4、x8、x16模式。盡管也存在多通道的對(duì)齊問(wèn)題。但呈現(xiàn)的總帶寬相對(duì)來(lái)說(shuō)會(huì)更大些。高速串口技術(shù)的發(fā)展未來(lái)仍是提升單通道速度和多通道并行使用相結(jié)合。所以,串并口的概念可能會(huì)進(jìn)一步模糊。整體結(jié)果是提供不斷改進(jìn)升級(jí)的數(shù)據(jù)總帶寬。

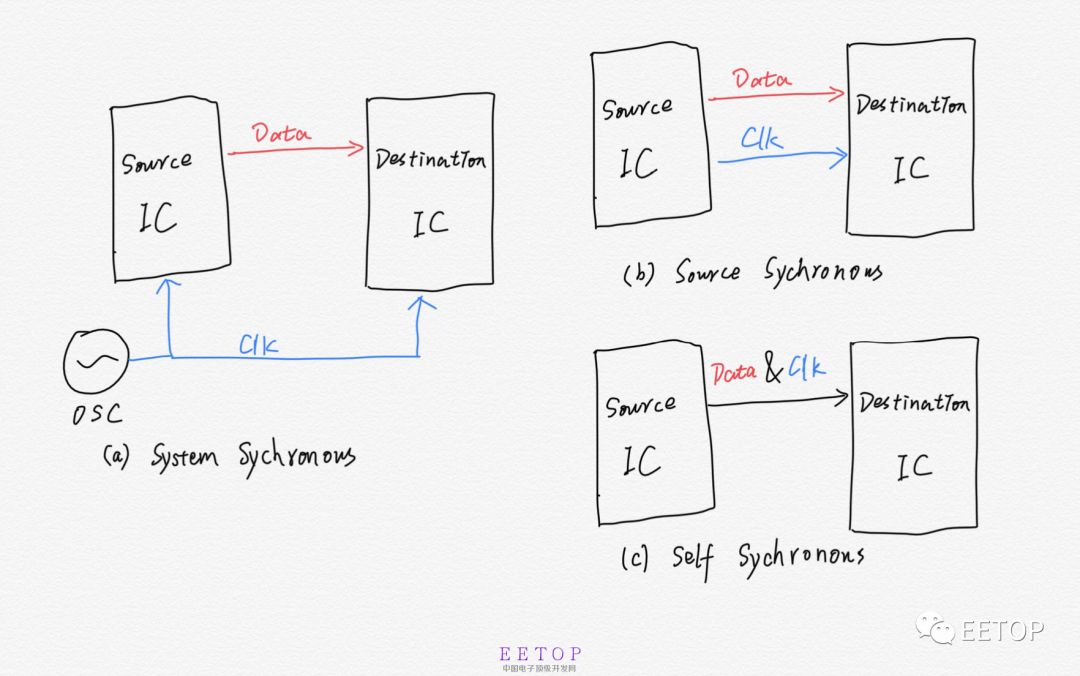

還需要了解下不同芯片間通過(guò)同步接口通信的3種基本時(shí)序模型。如圖3中(a/b/c),分別是系統(tǒng)同步,源同步和自同步的方式,圖中省略了板級(jí)和芯片內(nèi)部的布線延遲。最初接口速率較低時(shí),使用系統(tǒng)同步的方式就能滿足要求,隨著接口速度的提升,嚴(yán)格的時(shí)序要求會(huì)使用數(shù)據(jù)和時(shí)鐘同步發(fā)送的方式,比如像DDR的數(shù)據(jù)要同步dqs時(shí)鐘線那樣。

圖3

自同步其實(shí)就是目前SerDes中采用的方式,接口傳送的數(shù)據(jù)中包含了時(shí)鐘的信息,通過(guò)接收端(Rx)的時(shí)鐘數(shù)據(jù)恢復(fù)(Clock Data Recovery,CDR)電路完成對(duì)接收數(shù)據(jù)的時(shí)鐘抽取和數(shù)據(jù)再采樣。最終恢復(fù)出正確的數(shù)據(jù)。

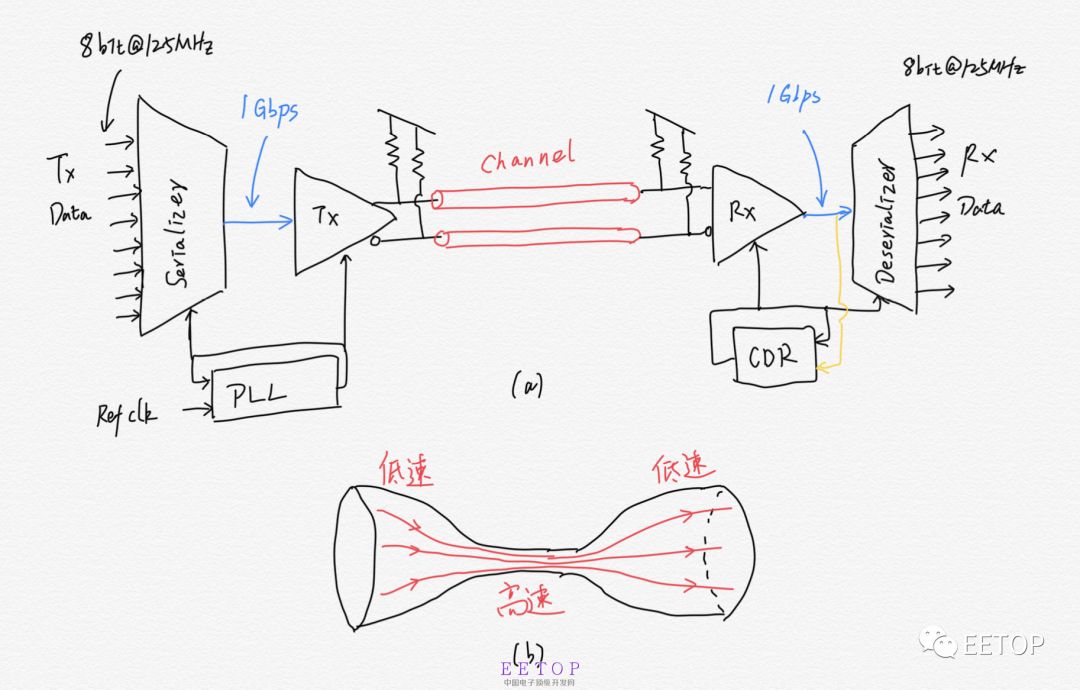

對(duì)于高速串行鏈路(High Speed Serial Link)使用的SerDes技術(shù),其中SerDes是串化器(Serializer)和解串器(Deserializer)的簡(jiǎn)寫(xiě),也基本說(shuō)明了SerDes的原理。就是要完成并串和串并轉(zhuǎn)換。SerDes是典型的數(shù)模混合系統(tǒng),需要比較多的背景知識(shí),數(shù)字電路和模擬電路、信號(hào)與系統(tǒng)、通信原理、微波和射頻電路、電磁場(chǎng)、信號(hào)和電源完整性等,綜合要求比較高,算是目前點(diǎn)到點(diǎn)(point-to-point)有線(wireline)通信的技術(shù)熱點(diǎn)。

SerDes接口簡(jiǎn)單示意圖如圖4,并給出了不同位置的數(shù)據(jù)速率的例子。圖(a)中時(shí)鐘速率為125MHz的8bit并行數(shù)據(jù)(一個(gè)時(shí)鐘周期8ns,共8bit數(shù)據(jù)),經(jīng)過(guò)串化,轉(zhuǎn)化為1Gbps的1bit串行數(shù)據(jù)(一個(gè)UI為1ns,包含1bit數(shù)據(jù)),經(jīng)過(guò)發(fā)送器和通道到接收器,經(jīng)過(guò)接收器處理后仍為1Gbps,解串后恢復(fù)為125MHz時(shí)鐘速率的8bit并行數(shù)據(jù)。這個(gè)過(guò)程可以形象理解為圖(b)的低速的拉瓦爾噴管,氣流從截面逐漸減小的椎體到截面逐漸增大的椎體,“截面大處流速小,截面小處流速大”。

圖4

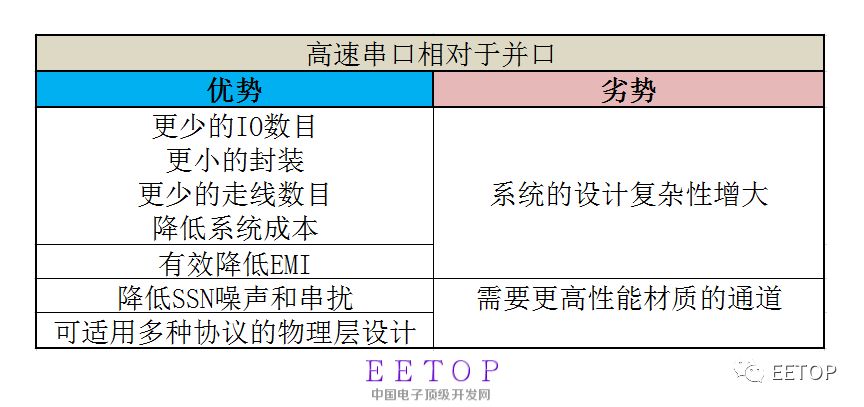

圖4(a)為SerDes只是“單工”形式,可以看到,通過(guò)串化可以將IO數(shù)量從8個(gè)減少到2個(gè)(信號(hào)傳輸多數(shù)采用差分形式)。可以有效緩解芯片IO數(shù)目緊張的問(wèn)題,同時(shí)減小PCB走線的復(fù)雜性。從經(jīng)濟(jì)性的角度,更小的封裝和更少的PCB走線,線纜和連接器等,會(huì)整體降低系統(tǒng)成本。高速串口技術(shù)相對(duì)于并口的主要優(yōu)劣勢(shì)總結(jié)如圖5中表格。

圖5

從圖4(a)也可初窺SerDes的技術(shù),主要體現(xiàn)在幾個(gè)方面。

第一,高頻低抖動(dòng)時(shí)鐘的生成。比如對(duì)于10Gpbs數(shù)據(jù)率,內(nèi)部需要產(chǎn)生至少10GHz的時(shí)鐘(Single Date Rate,SDR)或5GHz的時(shí)鐘(Double Date Rate, DDR)。隨著SerDes的發(fā)展,內(nèi)部PLL的時(shí)鐘頻率的不斷提高,Ring PLL和LC tank PLL都是不可缺少的,時(shí)鐘的抖動(dòng)和各種各樣的Jitter等對(duì)誤碼率(BER)的影響都需要充分分析。高性能時(shí)鐘是整個(gè)SerDes系統(tǒng)設(shè)計(jì)的一個(gè)技術(shù)重點(diǎn)。

第二,信號(hào)完整性考慮。在傳輸線內(nèi)容中我們初步了解到傳輸線的非理性特性,隨著信號(hào)的數(shù)據(jù)率提高和通道長(zhǎng)度的增加,發(fā)送器(Tx)發(fā)送的數(shù)據(jù)經(jīng)過(guò)信道(channel)后衰減和碼間干擾(ISI)的存在使得接收器(Rx)端的信號(hào)已經(jīng)沒(méi)了模樣。為了把數(shù)據(jù)正確恢復(fù)出來(lái),需要通過(guò)均衡器(Equalizer)均衡信道的衰減和數(shù)據(jù)的碼間干擾。比如常見(jiàn)的有Tx的前饋均衡(FFE),Rx端的連續(xù)時(shí)間線性均衡(CTLE)和判決前饋均衡(DFE)等手段。

第三,自適應(yīng)算法。Rx端的均衡通常需要滿足不同材質(zhì)和長(zhǎng)度信道的特性,并對(duì)信號(hào)不同頻率成分的衰減進(jìn)行補(bǔ)償。CTLE和DFE通常都會(huì)使用自適應(yīng)算法(Self-Adaptive Algorithm)實(shí)時(shí)動(dòng)態(tài)調(diào)整來(lái)應(yīng)對(duì)信道的特性變化。如果不了解算法實(shí)現(xiàn),就不能準(zhǔn)確的理解DFE的本質(zhì)。

關(guān)于自適應(yīng)算法有很多的教材,比如Simon Haykin著的《自適應(yīng)濾波器原理》,最近翻看,真的是頭大。哎,后悔當(dāng)初數(shù)學(xué)沒(méi)有好好學(xué),現(xiàn)在還在慢慢啃。只能說(shuō)很難理解。

圖6

第四,CDR環(huán)路。Rx端的另一個(gè)難點(diǎn)是CDR環(huán)路,CDR的實(shí)現(xiàn)有不同的實(shí)現(xiàn)方式。CDR的環(huán)路通常會(huì)包含了大量數(shù)字實(shí)現(xiàn),準(zhǔn)確的理解也很關(guān)鍵,對(duì)這部分的理解還在學(xué)習(xí)中,有機(jī)會(huì)再和大家分享。

第五,時(shí)序約束限制。當(dāng)數(shù)據(jù)率升高時(shí),對(duì)于DFE的判決反饋回路的時(shí)序設(shè)計(jì)提出了更高的要求。比如說(shuō)對(duì)于50Gbps的SerDes,一個(gè)UI的時(shí)間為20ps,幾乎和邏輯門(mén)的延遲相當(dāng),這就要求DFE的反饋回路的邏輯設(shè)計(jì)必須盡可能的簡(jiǎn)單。單獨(dú)時(shí)鐘速率會(huì)遇到困難,而采用PAM-4或PAM-8等信號(hào)方式就會(huì)顯得很有前景。

SerDes是一個(gè)復(fù)雜數(shù)模混合系統(tǒng),內(nèi)部還包含了大量數(shù)字實(shí)現(xiàn)內(nèi)容。8B/10B等編解碼實(shí)現(xiàn),PRBS生成和檢查,環(huán)回測(cè)試、自適應(yīng)算法實(shí)現(xiàn),系統(tǒng)狀態(tài)控制數(shù)字實(shí)現(xiàn)等等。

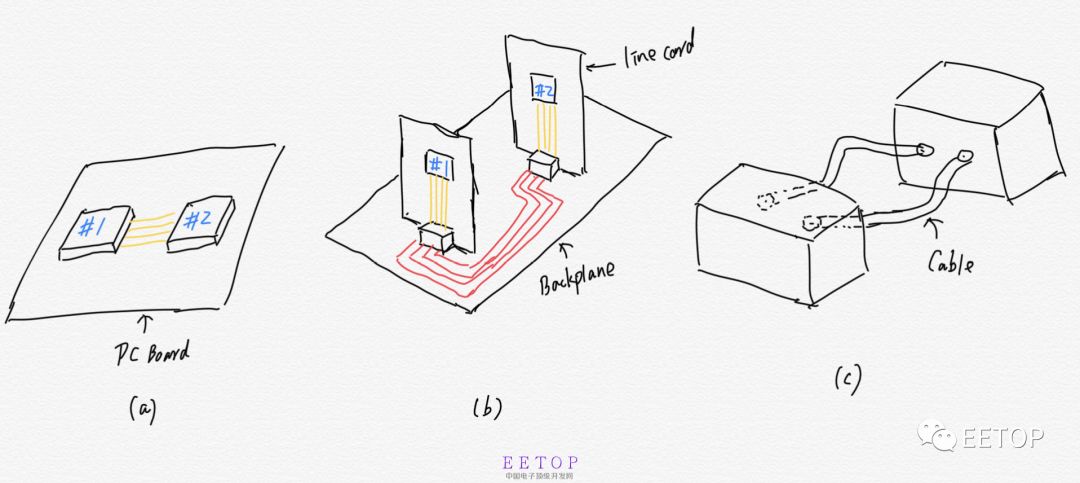

目前SerDes的應(yīng)用,主要有Chip-to-Chip,Board-to-Board, Box-to-Box等形式,如圖7(a/b/c)示意圖。并在大型數(shù)據(jù)中心,通信骨干網(wǎng)絡(luò),消費(fèi)電子等場(chǎng)景下都有應(yīng)用。

圖7

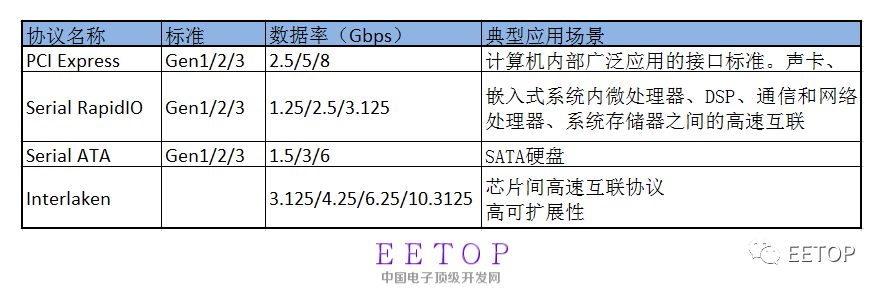

不同的應(yīng)用場(chǎng)合也催生了不同的協(xié)議標(biāo)準(zhǔn)。如PCI Express,Serial ATA,Ethernet,Serial RapidIO和Aurora等。不同協(xié)議標(biāo)準(zhǔn)有著不同的速率,并且在不斷的演進(jìn)中。圖8列出了幾種協(xié)議的數(shù)據(jù)率,目前單通道的線速率主要是集中在Gbps以上。

圖8

從協(xié)議的角度看,不同的協(xié)議通常會(huì)有不同的分層定義。我們關(guān)注的SerDes硬件實(shí)現(xiàn)大多集中在物理層。當(dāng)然對(duì)協(xié)議更高層的了解能夠幫助更好的理解底層硬件實(shí)現(xiàn)。

另附文中縮寫(xiě)術(shù)語(yǔ)全稱:

NRZ Non-Return to Zero

PAM-4 Pluse Amplitude Modulation - 4 level

SerDes Serializer/Deseiralizer

Gbps Gigabit per second

CTLE Continuous Time Linear Equalization

DFE Desicion Feedback Equalization

FFE Feed Forward Equalization

ISI Inter-Symbol Interference

PRBS Pseudo-Random Binary Sequence

-

接口技術(shù)

+關(guān)注

關(guān)注

1文章

274瀏覽量

41361 -

SerDes

+關(guān)注

關(guān)注

6文章

198瀏覽量

34906

原文標(biāo)題:SerDes概述

文章出處:【微信號(hào):eetop-1,微信公眾號(hào):EETOP】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

微機(jī)接口技術(shù)課件

WCDMA無(wú)線接口技術(shù)

FPGA技術(shù)的發(fā)展歷史和動(dòng)向

李全利-[單片機(jī)原理及接口技術(shù)]

微機(jī)原理與接口技術(shù)

封裝天線技術(shù)發(fā)展歷程回顧分析

微機(jī)控制與接口技術(shù)實(shí)驗(yàn)教學(xué)的研究與探討

微機(jī)接口技術(shù)嘗試

微機(jī)原理與接口技術(shù)

淺析單片機(jī)原理及接口技術(shù)

微機(jī)接口技術(shù)實(shí)用教程

深度解析腦機(jī)接口技術(shù)

回顧接口技術(shù)發(fā)展歷史

回顧接口技術(shù)發(fā)展歷史

評(píng)論