前面的文章提到過,PCI總線中定義兩個邊帶信號(PERR#和SERR#)來處理總線錯誤。其中PERR#主要對應的是普通數據奇偶校檢錯誤(Parity Error),而SERR#主要對應的是系統錯誤(System Error)。具體如下:

· 普通的數據奇偶校檢錯誤——通過PERR#報告

· 在多任務事務(Multi-task Transaction,又稱為Special Cycles)時的奇偶校檢錯誤——通過SERR#報告

· 地址和命令的奇偶校檢錯誤——通過SERR#報告

· 其他錯誤——通過SERR#報告

一個簡單的例子如下圖所示:

PCIe作為一種高速串行總線,取消了PCI總線中的這兩個邊帶信號,采用錯誤消息的方式來實現錯誤報告。但是,在軟件層面上,PCIe仍是兼容PCI總線的,具體后面會詳細描述。

在PCIe總線的錯誤報告機制中,有如下四個比較重要的概念:

· 錯誤檢測(Error Detection):指的是檢測某個錯誤是否存在的過程。

· 錯誤登記(Error Logging):指的是將相關寄存器(配置空間中的)的對應為置位,以等待軟件中的相關錯誤處理程序來處理該錯誤。

· 錯誤報告(Error Reporting):通知系統某個(或多個)錯誤發生了。在PCIe總線中,發生錯誤的設備會通過錯誤消息(Error Message)逐級將錯誤信息發送至Root,Root接收到錯誤消息后,會產生對應的中斷通知系統。

· 錯誤發送(Error Signaling):指的是通過發送錯誤消息(或者帶有UR,CA的Completion和Poisoned TLP)來傳遞錯誤信息的過程。

注:“帶有UR,CA的Completion”在前面的文章中介紹過,不熟悉的可以回顧一下。“Poisoned TLP”是PCIe總線錯誤報告機制中的Error Forwarding的方式,具體會在后面詳細介紹。

PCIe總線Spec定義了兩個錯誤報告等級。第一個為基本的(Baseline Capability),是所有PCIe設備都需要支持的功能。第二個是可選的,稱之為高級錯誤報告(Advanced Error Reporting Capability)。

在基本的錯誤報告機制中,有兩組相關的配置寄存器(配置空間中),分別為:

· 兼容PCI總線的寄存器(PCI-compatible Registers)

· PCIe總線中新增的寄存器(PCI Express Capability Registers)

高級錯誤報告機制(AER)中,又使用了一組專用的配置寄存器(配置空間中)。借助AER可以獲得更多的錯誤信息,有助于軟件定位錯誤源和分析錯誤原因。

PCIe總線的錯誤可以分為(Correctable Errors)和不可校正錯誤(Uncorrectable Errors)。其中,可校正錯誤可以自動地被硬件識別并被自動的校正或恢復。而不可校正錯誤又被分為非致命的(Non-Fatal)和致命的(Fatal)。非致命的錯誤一般有設備驅動軟件(Device Specific Software)直接處理,且鏈路(Link)可恢復,甚至鏈路上的數據有可能得到恢復(不丟失數據)。致命的錯誤只能由系統軟件(System Software)處理,且一般需要進行復位等操作,因此鏈路上的數據必然會丟失。

-

寄存器

+關注

關注

31文章

5357瀏覽量

120632 -

總線

+關注

關注

10文章

2891瀏覽量

88165 -

PCIe

+關注

關注

15文章

1243瀏覽量

82766

原文標題:【博文連載】PCIe掃盲——PCIe錯誤定義與分類

文章出處:【微信號:ChinaAET,微信公眾號:電子技術應用ChinaAET】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

PCB設計中如何進行統一批量檢測并生成錯誤報告

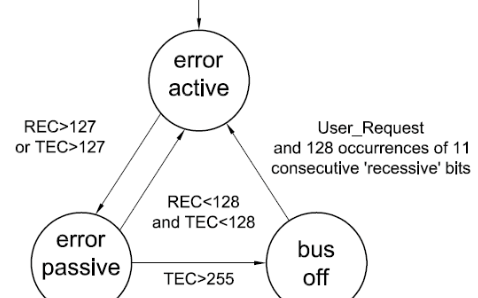

CAN控制器總線錯誤分析之CAN節點BusOff恢復過程分析與測試

Win8系統操作不當彈出錯誤報告

關于Quartus II 錯誤報告Error (171173): Node from partition Top cannot preserve previous placement at PIN_P8 and honor the location assigment to PIN_F8

MPLAB X IDE v3.20編譯器使用錯誤的行號引用報告錯誤

為什么我設計的TMS320VC5402板子在調試軟件時總會出現存儲器錯誤報告?

基于軟件錯誤報告數據集成的改進貝葉斯算法

PCIe總線的三種錯誤報告方式

PCIe總線的錯誤報告機制中四個比較重要的概念

PCIe總線的錯誤報告機制中四個比較重要的概念

評論