高性能數(shù)據(jù)轉(zhuǎn)換器是第五代移動通信基站系統(tǒng)的核心器件,其采樣速率不低于3 GS/s、分辨率高于12 bit,因此高速串行接口取代傳統(tǒng)接口電路成為必然趨勢。基于JESD204B協(xié)議設(shè)計了一種應(yīng)用于3 GS/s 12 bit ADCs的高速串行接口控制層電路。在保證高速傳輸?shù)那疤嵯拢壑锌紤]功耗和資源,該電路在傳輸層采用預(yù)分頻技術(shù)完成組幀;在數(shù)據(jù)鏈路層采用極性信息簡化編碼技術(shù)實現(xiàn)8 B/10 B編碼。在Vivado 16.1環(huán)境下,采用Xilinx公司的ZC706 FPGA中PHY IP和JESD204B Receiver IP完成控制層接口電路的驗證。實驗結(jié)果表明數(shù)據(jù)傳輸正確,且串化后的傳輸速度達(dá)到7.5 Gb/s,相較于同類型的接口設(shè)計,其傳輸速度提高了50%。

0 引言

在第五代移動通信中,高性能A/D、D/A轉(zhuǎn)換器是其發(fā)展的核心器件。因此,隨著轉(zhuǎn)換器分辨率和采樣速率的提高,多路并行數(shù)據(jù)傳輸不僅增加芯片的引腳設(shè)計,還增加板級布線和系統(tǒng)互聯(lián)的硬件開銷,直接增加系統(tǒng)成本。而且當(dāng)數(shù)據(jù)速率超過1 Gb/s時,低電壓差分信號(Low-Voltage Differential Signaling,LVDS)技術(shù)難以滿足轉(zhuǎn)換器帶寬的需要。因此,用于數(shù)據(jù)轉(zhuǎn)換器的高速串行接口正在形成一種趨勢,以支持更高速轉(zhuǎn)換器、靈活的時鐘以及確定性延遲等日漸嚴(yán)苛的要求[1]。

JESD204B針對高速數(shù)據(jù)轉(zhuǎn)換器的串行數(shù)據(jù)接口,不僅可以克服LVDS并行數(shù)據(jù)傳輸帶來的性能下降,同時最高可支持12.5 Gb/s,比LVDS吞吐量提高10倍,降低I/O需求及封裝尺寸,降低靜態(tài)功耗和節(jié)省系統(tǒng)成本。

目前,主流的高速高精度數(shù)據(jù)轉(zhuǎn)換器芯片均采用JESD204B接口,如ADI近期發(fā)布的14 bit 2.6 GS/s雙通道模數(shù)轉(zhuǎn)換器AD9689和TI推出的12 bit 8 GS/s射頻模數(shù)采樣芯片ADC12J4000[2]等。國內(nèi)相關(guān)技術(shù)雖然落后于國外,但各高校和科研機(jī)構(gòu)針對不同的應(yīng)用均做了相關(guān)研究,并取得了一定的進(jìn)展。本文根據(jù)JESD204B標(biāo)準(zhǔn)設(shè)計了高速串行接口發(fā)送端控制層電路,主要包括傳輸層、數(shù)據(jù)鏈路層。通過搭建的硬件仿真平臺,驗證了控制層電路的正確性,并且其性能也很理想。

1 JESD204B標(biāo)準(zhǔn)概述

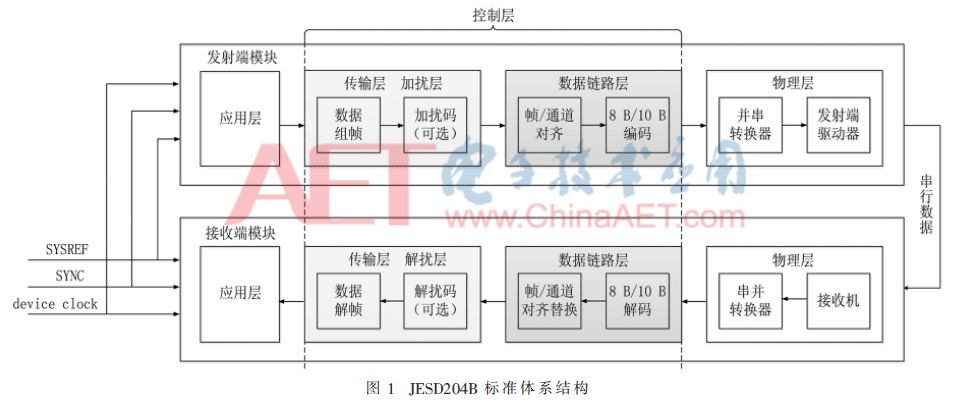

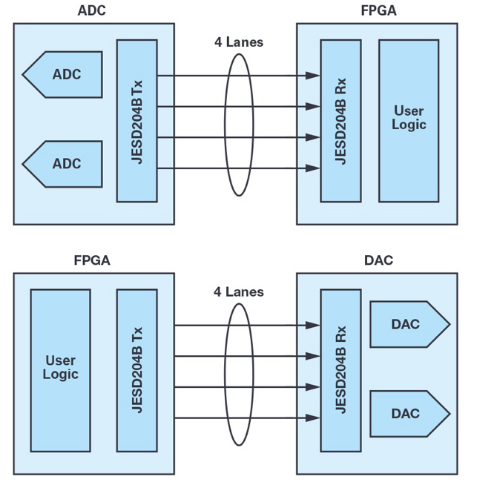

JESD204B是一種數(shù)模轉(zhuǎn)換器通過串行接口鏈路連接后端數(shù)字信號處理設(shè)備的標(biāo)準(zhǔn)。該標(biāo)準(zhǔn)的體系結(jié)構(gòu)可分為應(yīng)用層、傳輸層、鏈路層和物理層,在功能上可將接收接口作為發(fā)送接口的逆過程。應(yīng)用層是負(fù)責(zé)JESD204B鏈路配置和數(shù)據(jù)映射。傳輸層主要是用戶根據(jù)數(shù)據(jù)格式的配置來對數(shù)據(jù)結(jié)構(gòu)重新打包,以便映射為8位字節(jié)。加擾層為可選擇模塊,主要通過對8位字節(jié)的加解擾來擴(kuò)展頻譜,從而減少電磁干擾效應(yīng)。數(shù)據(jù)鏈路層主要實現(xiàn)同步字符的產(chǎn)生、多幀同步、鏈路對齊、鏈路同步等用于通道對準(zhǔn)監(jiān)控和維護(hù)的操作,以及8 B/10 B編解碼。物理層用于支持高速串行數(shù)據(jù)的發(fā)送與接收、串行與并行之間的轉(zhuǎn)換。其結(jié)構(gòu)如圖1所示。

2 發(fā)送端控制層電路的設(shè)計與實現(xiàn)

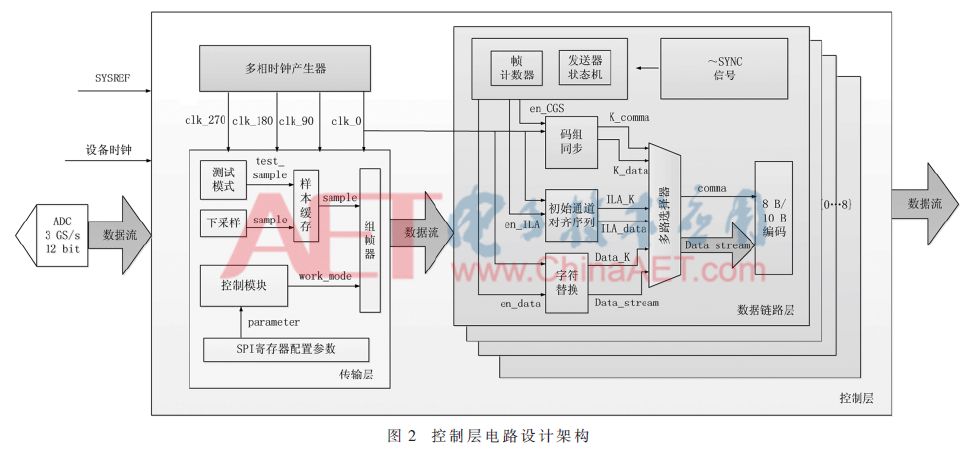

根據(jù)3 GS/s 12 bit高速高精度A/D轉(zhuǎn)換器以及JESD204B標(biāo)準(zhǔn)中子類1工作模式的要求,搭建了一個完整的發(fā)送端控制層電路框架,如圖2所示。本文設(shè)計的電路主要包括3個模塊:傳輸層模塊、數(shù)據(jù)鏈路層模塊和8 B/10 B編碼器模塊。首先根據(jù)轉(zhuǎn)換器數(shù)量M=4和樣本數(shù)S=4,將ADC過來的3 GS/s 12 bit數(shù)據(jù)送入傳輸層,然后對其降頻后通過讀取串行外設(shè)接口(Serial Parallel Interface,SPI)發(fā)送過來的配置信息來添加控制字符和尾字符的方式把數(shù)據(jù)打包成通道數(shù)L=8的并行數(shù)組;之后把每個通道的32 bit數(shù)據(jù)送入數(shù)據(jù)鏈路層,通過碼組同步(Code Group Synchronization,CGS)、初始通道對齊序列(Initial Lane Alignment Sequence,ILAS)階段和字符替換來實現(xiàn)同步字符的產(chǎn)生、多幀同步、鏈路對齊與同步等操作;最后把數(shù)據(jù)送入8 B/10 B編碼模塊來完成控制層接口的數(shù)據(jù)傳輸。

2.1 傳輸層模塊設(shè)計

傳輸層對于發(fā)送端控制層接口來說,是整個電路模塊設(shè)計的開始,它主要通過添加控制字符和尾字符把接收的3 GS/s 12 bit ADC數(shù)據(jù)打包成8位并行數(shù)組。由于從ADC過來的數(shù)據(jù)速率很高,并且考慮在FPGA板上可實現(xiàn)的最高頻率問題,因此在傳輸層的第一級將其轉(zhuǎn)換為4路并行的750 MS/s 12 bit的ADCs,并利用多相時鐘產(chǎn)生器對每一路數(shù)據(jù)進(jìn)行下采樣,產(chǎn)生4相、相位間隔90°的187.5 MHz的采樣時鐘。然后根據(jù)SPI寄存器配置參數(shù)來進(jìn)行合理的數(shù)據(jù)映射,即把多位樣本數(shù)據(jù)轉(zhuǎn)換成一系列非擾碼的8位字節(jié)。因此傳輸層總體電路結(jié)構(gòu)可分為5個模塊:下采樣模塊、樣本緩存模塊、SPI寄存器配置參數(shù)讀取模塊、模式控制模塊和組幀器模塊。

下采樣模塊是對數(shù)據(jù)進(jìn)行S取4的采樣,進(jìn)而達(dá)到對整個系統(tǒng)降頻的目的。樣本緩存模塊是對前面下采樣模塊的樣本數(shù)據(jù)按由低到高依次先暫存在樣本緩存器中,緩存空間大小定義為256 bit。圖3為下采樣模塊送入樣本緩存模塊的數(shù)據(jù)組合格式,這樣的組合也有益于組幀時數(shù)據(jù)的讀取。SPI寄存器配置參數(shù)模塊主要是讀取SPI發(fā)送過來的配置信息,根據(jù)配置寄存器中定義的10 bit存儲參數(shù)值,為模式控制模塊提供組幀判斷信息。模式控制模塊是根據(jù)不同的配置參數(shù)組合對當(dāng)前的工作模式進(jìn)行判斷。表1是根據(jù)項目需求提出的6種工作模式以及所支持的映射組幀參數(shù)。組幀器模塊主要是根據(jù)模式控制模塊的組幀模式信息,按照J(rèn)ESD204B標(biāo)準(zhǔn)的數(shù)據(jù)映射方法完成對樣本緩存模塊采樣數(shù)據(jù)的組幀。這種映射方式有利于降低電路功耗,節(jié)省電路資源和減小電路面積。

2.2 數(shù)據(jù)鏈路層設(shè)計

數(shù)據(jù)鏈路層是整個發(fā)送端的關(guān)鍵組成部分。在數(shù)據(jù)鏈路層中,需要對傳輸層傳輸過來的數(shù)據(jù)進(jìn)行初始化幀同步、初始化通道同步和字節(jié)產(chǎn)生替換來建立正確的傳輸通道,然后采用8 B/10 B方式對數(shù)據(jù)進(jìn)行編碼,并生成特殊控制符來實現(xiàn)通道對準(zhǔn)監(jiān)控和維護(hù)。同時,在設(shè)計該模塊電路時要兼顧速度、面積和功耗等資源。所以,將數(shù)據(jù)鏈路層分為鏈路控制模塊、CGS模塊、ILAS模塊、字符替換模塊以及多路數(shù)據(jù)選擇器模塊。

2.2.1 鏈路控制模塊

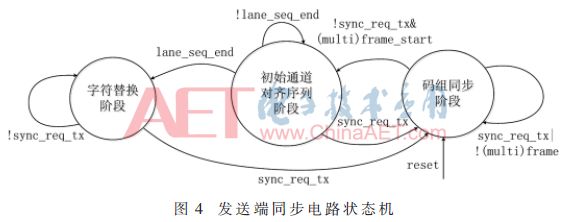

鏈路控制模塊是對整個數(shù)據(jù)鏈路層的控制,主要負(fù)責(zé)在鏈路層初始化過程、同步維持過程和重同步過程中發(fā)送對應(yīng)的數(shù)據(jù)和控制信號,方便其余模塊根據(jù)其反饋信息進(jìn)行調(diào)整,從而完成鏈路初始化到正常數(shù)據(jù)發(fā)送操作的過程,如圖4所示的跳轉(zhuǎn)機(jī)制。

首先,鏈路在復(fù)位結(jié)束或收到再同步請求時,進(jìn)入到CGS階段,不斷發(fā)送規(guī)定的碼組同步字符。若發(fā)現(xiàn)同步請求信號取消,狀態(tài)機(jī)就會轉(zhuǎn)移到ILAS階段。ILAS階段會將4個多幀序列發(fā)送完,然后發(fā)送相應(yīng)的指示信號給狀態(tài)機(jī),表明已完成該序列并請求狀態(tài)轉(zhuǎn)移。控制模塊接收到該信號有效后,將狀態(tài)機(jī)轉(zhuǎn)換到正常的數(shù)據(jù)發(fā)送階段,并選擇字符替換模塊輸出數(shù)據(jù)。

2.2.2 CGS模塊

CGS階段是鏈路層進(jìn)行初始化操作的第一步。主要通過Comma碼進(jìn)行字符邊界的檢測,使得接收端在連續(xù)的串行數(shù)據(jù)流中檢測出字符的邊界。

具體實現(xiàn)過程是,當(dāng)鏈路系統(tǒng)發(fā)生復(fù)位或者重同步時,接收端SYNC同步信號拉低置0,由此進(jìn)入CGS階段。在CGS階段期間,發(fā)送端發(fā)射一系列連續(xù)的標(biāo)志符/K28.5/(不少于F+9個/K28.5/字節(jié),F(xiàn)為每幀的字節(jié)數(shù)目),接收端在收到至少4個連續(xù)/K28.5/字符,并對無序比特流定邊界后就解除對發(fā)送端同步請求信號。發(fā)送端檢測到同步請求解除后,在下一個本地多幀時鐘上升沿停止發(fā)送/K28.5/字符,然后進(jìn)入ILAS階段。

2.2.3 ILAS模塊

當(dāng)系統(tǒng)完成CGS階段之后,發(fā)送端緊接著就進(jìn)入ILAS階段。在ILAS階段,一方面是為了發(fā)送鏈路配置數(shù)據(jù),另一方面是完成幀以及多幀初始化同步。ILAS由4個多幀組成,這4個多幀均以/R/=/K28.0/控制字符開頭,以/A/=/K28.3/控制字符結(jié)尾,中間為正常數(shù)據(jù)。這樣可以讓接收端通過/A/字符來完成多幀末尾的對齊。除此之外,第二個多幀的第二個8位字節(jié)是/Q/=/K28.4/控制字符,它標(biāo)示著鏈路配置數(shù)據(jù)傳輸?shù)拈_始,其中配置數(shù)據(jù)有14個字節(jié)。

2.2.4 字符替換模塊

在JESD204B協(xié)議中,用碼組同步和初始通道對齊序列來完成字節(jié)邊界同步和多通道對齊。當(dāng)系統(tǒng)完成了上述兩個階段后,在非擾碼模式下傳輸層將用戶數(shù)據(jù)直接發(fā)送到數(shù)據(jù)鏈路層的用戶數(shù)據(jù)階段。此時,要對數(shù)據(jù)進(jìn)行同步字符替換,達(dá)到監(jiān)控、校正和通道對準(zhǔn),從而建立在發(fā)送端與接收端正確的傳輸通道,提高傳輸?shù)臏?zhǔn)確性。DATA字符替換模塊遵循如下規(guī)則:

(1)當(dāng)前幀的最后一個字節(jié)與多幀的最后一個字節(jié)不一致時,如果當(dāng)前幀的最后一個字節(jié)和前一幀的最后一個字節(jié)相同時,發(fā)送端應(yīng)該把當(dāng)前幀的最后一個字節(jié)用控制字符/F/=/K28.7/進(jìn)行替換。但如果前一幀的最后一個字節(jié)已經(jīng)是特殊控制字符,則當(dāng)前幀的最后一個字節(jié)不對其進(jìn)行替換,保持原始數(shù)據(jù)的正常傳輸。

(2)當(dāng)前幀的最后一個字節(jié)與多幀的最后一個字節(jié)一致時,如果當(dāng)前幀的最后一個字節(jié)和前一幀的最后一個字節(jié)相同時,發(fā)送端應(yīng)該把當(dāng)前幀的最后一個字節(jié)用控制字符/A/=/K28.3/進(jìn)行替換。與規(guī)則1不同的是,即使前一幀已經(jīng)用特殊控制字符替換過了,也應(yīng)該對原始數(shù)據(jù)進(jìn)行替換。

2.2.5 8 B/10 B編碼模塊

8 B/10 B編解碼最早由IBM公司提出,早期的查表法雖然實現(xiàn)起來較簡單,但其速率、面積和功耗等資源方面受到了很大的限制。為了滿足JESD204B協(xié)議接口,本文采用極性信息簡化編碼表對8 B/10 B編碼進(jìn)行實現(xiàn)。

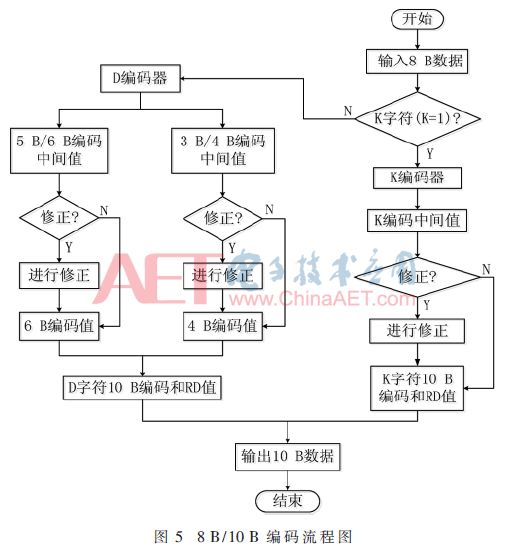

對于新型8 B/10 B編碼來說,它主要是在保證DC平衡和轉(zhuǎn)換密度的情況下,利用3 B/4 B和5 B/6 B并行編碼來提升電路工作頻率。同時還采用一些特殊控制符來進(jìn)行誤碼監(jiān)測。本文就是基于這樣的設(shè)計將編碼電路分為K字符編碼器模塊和D字符編碼器模塊,其中K字符編碼器模塊采用直接編碼的方法,而D字符編碼器模塊分為5 B/6 B編碼和3 B/4 B編碼。首先進(jìn)行K字符編碼和D字符編碼的選擇,并且進(jìn)行對應(yīng)的初步編碼;然后對所對應(yīng)的編碼進(jìn)行修正,最后進(jìn)行選擇性輸出。其相關(guān)的主要編碼流程如圖5所示。

3 仿真與驗證

3.1 驗證方法

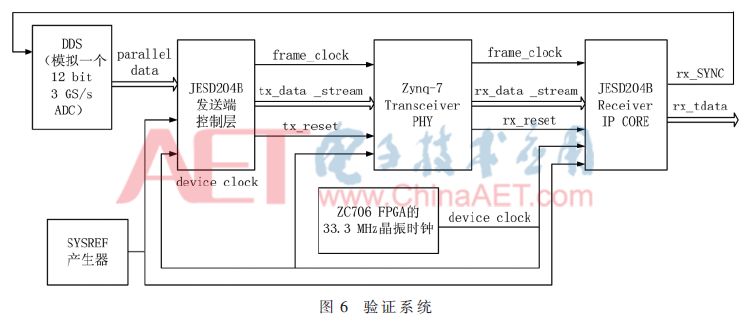

本文采用Modelsim 10.1軟件完成了JESD204B發(fā)送端控制層電路的前端仿真驗證。采用Vivado 16.1軟件和Zynq-7000系列芯片XC7Z045FFG900-2 FPGA中的JESD204B PHY IP和Receiver IP[11]搭建硬件仿真驗證平臺,把控制層輸出的并行數(shù)據(jù)發(fā)送給PHY IP,經(jīng)過串化等一系列操作送給JESD204B Receiver IP,最后通過用ILA核抓取數(shù)據(jù)傳輸?shù)膶崟r波形圖和對比發(fā)送、接收的數(shù)據(jù),來實現(xiàn)硬件仿真驗證,如圖6所示。

3.2 驗證結(jié)果

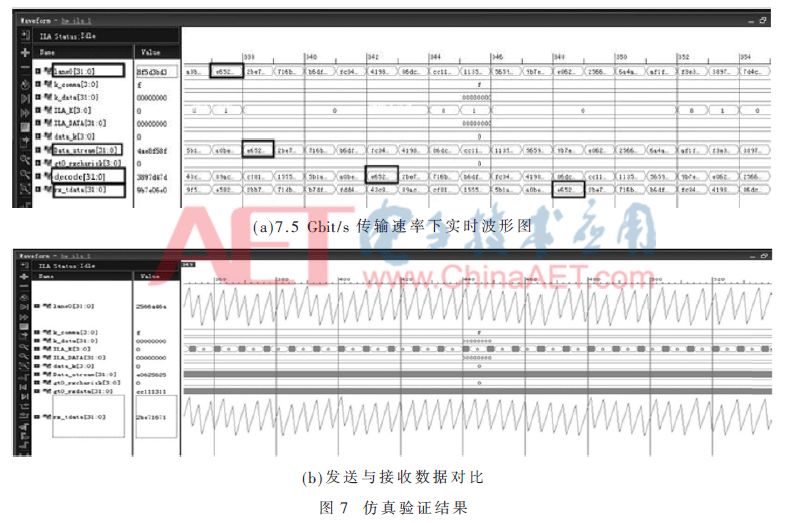

用Vivado16.1將功能仿真正確的RTL級代碼綜合后的電路燒寫到ZC706開發(fā)板上,并使用ILA核抓取信號的實時波形進(jìn)行分析。圖7(a)和圖7(b)是鏈路建立后用戶數(shù)據(jù)傳輸?shù)膶崟r波形截圖,在經(jīng)過傳輸層輸出32 bit數(shù)據(jù)、鏈路層用戶數(shù)據(jù)、8 B/10 B編解碼和JESD204B Receiver IP輸出的32 bit數(shù)據(jù)后,對比發(fā)現(xiàn)發(fā)送和接收的數(shù)據(jù)無錯碼,即驗證了發(fā)送端控制層電路數(shù)據(jù)傳輸?shù)恼_性。

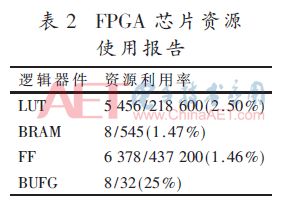

本文設(shè)計電路占用的FPGA資源如表2所示。除此之外,整個發(fā)送端控制層電路的功耗為0.467 W,建立時間的slack為0.235 ns,保持時間的slack為0.068 ns,并且經(jīng)過IP串化后的位速率達(dá)到7.5 Gb/s。

4 結(jié)論

隨著轉(zhuǎn)換器分辨率和速度不斷提高,JESD204B串行接口電路成為高速高精度數(shù)據(jù)轉(zhuǎn)換器的標(biāo)準(zhǔn)接口。本文根據(jù)JESD204B標(biāo)準(zhǔn)設(shè)計了應(yīng)用于3 GS/s 12 bit ADC發(fā)送端控制層接口,在滿足速率的前提下,采用預(yù)分頻技術(shù)和極性信息簡化編碼技術(shù)實現(xiàn)功耗和資源優(yōu)化,并采用Xilinx公司的Zynq-7000系列芯片XC7Z045FFG900-2 FPGA驗證系統(tǒng),完成了硬件仿真驗證,串化后的位速率可以達(dá)到7.5 Gb/s,相較于同類型的接口設(shè)計,其傳輸速度提高了50%。

-

電路

+關(guān)注

關(guān)注

172文章

5901瀏覽量

172135 -

串行接口

+關(guān)注

關(guān)注

3文章

327瀏覽量

42603 -

數(shù)模轉(zhuǎn)換器

+關(guān)注

關(guān)注

14文章

1011瀏覽量

83166

原文標(biāo)題:【學(xué)術(shù)論文】基于3 GS/s 12 bit ADCs的 高速串行接口控制層電路的設(shè)計與實現(xiàn)

文章出處:【微信號:ChinaAET,微信公眾號:電子技術(shù)應(yīng)用ChinaAET】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

相關(guān)推薦

寬帶數(shù)據(jù)轉(zhuǎn)換器應(yīng)用的JESD204B與串行LVDS接口考量

JESD204B接口標(biāo)準(zhǔn)信息理解

JESD204B的系統(tǒng)級優(yōu)勢

在Xilinx FPGA上快速實現(xiàn)JESD204B

基于高速串行數(shù)字技術(shù)的JESD204B鏈路延時設(shè)計

串行LVDS和JESD204B的對比

JESD204B串行接口時鐘的優(yōu)勢

FPGA高速數(shù)據(jù)采集設(shè)計之JESD204B接口應(yīng)用場景

FPGA高速數(shù)據(jù)采集設(shè)計之JESD204B接口應(yīng)用場景

如何讓JESD204B在FPGA上工作?FPGA對于JESD204B需要多少速度?

JESD204B協(xié)議介紹

JESD204B的優(yōu)勢

JESD204B標(biāo)準(zhǔn)及演進(jìn)歷程

針對高速數(shù)據(jù)轉(zhuǎn)換器的最新高速JESD204B標(biāo)準(zhǔn)帶來了驗證挑戰(zhàn)

根據(jù)JESD204B標(biāo)準(zhǔn)設(shè)計了高速串行接口發(fā)送端控制層電路

根據(jù)JESD204B標(biāo)準(zhǔn)設(shè)計了高速串行接口發(fā)送端控制層電路

評論