在了解了ESD的基本概念及其與用于板載ESD保護的工具和組件后,Qorvo將全面介紹靜電放電和移動設備ESD系統設計建模技術和RF前端(RFFE)設計的考慮因素。

綜合各種因素

通常,系統設計人員使用反復試驗的方法來添加ESD保護。那是否存在負面影響呢?僅使用組件級ESD規范不足以實現穩健的系統設計。我們的目標是預測最終手機設計的ESD性能,以創建一個提供ESD保護的萬無一失、一次性過關的系統設計。

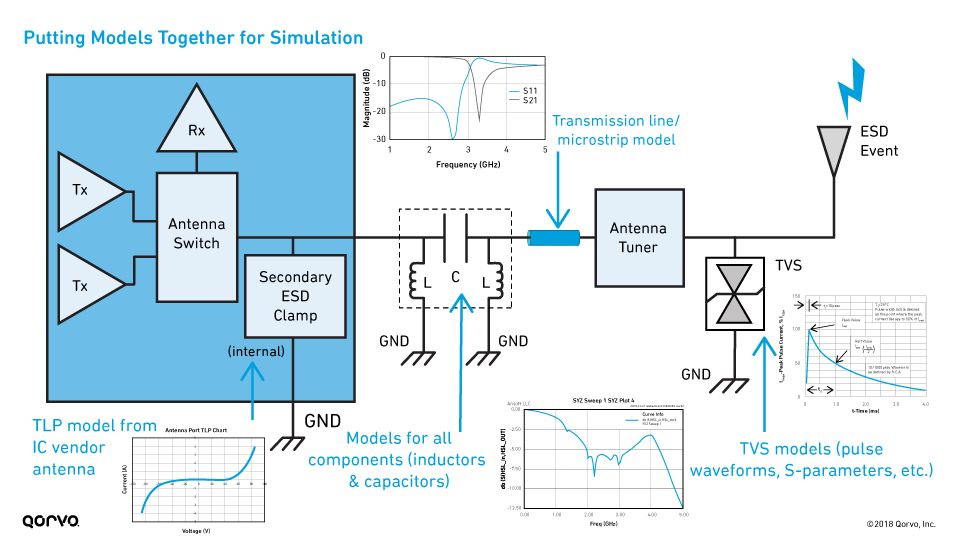

最佳方法之一是使用模型來仿真IEC 61000-4-2接觸放電脈沖,這樣您就可以在確定ESD性能之后才投入時間和成本,用于實際的原型設計。

為此,我們采用系統高效ESD設計(SEED)方法。SEED是一種板載和片上ESD保護的協同設計方法,它有助于分析和實現系統級ESD穩健性能。該方法要求對ESD應力事件期間的外部ESD脈沖之間的相互作用、完整的系統級板設計以及設備引腳特性有一個全面的了解。

SEED建模和仿真的主要步驟

SEED方法需要對系統的各種組件和軌跡進行建模和仿真。總體來說,使用SEED方法的建模和仿真步驟包括:

第1步:收集系統信息,例如:

PC板Gerber文件,包括PC板材料規格(堆疊文件、傳輸線規格等)

瞬態電壓抑制器(TVS)、電感和電容的器件型號(S?參數、I-V特性、ESD額定值、IV-TLP特性等)

RF前端模塊I/O引腳的片上ESD保護模型(IV-TLP測量、S?參數、ESD額定值等)

第2步:運行瞬態和RF仿真,對ESD保護器件在系統級ESD應力和正常工作期間的行為進行建模。

具體步驟:如何進行SEED仿真

讓我們通過一個簡單的示例來說明如何使用SEED方法來設計ESD保護。首先,您需要確定系統中所需的隔離阻抗,以確保IC引腳的峰值ESD電流和電壓在片上(次級鉗位)保護能力的范圍內。這通過利用IEC應力模型和板載TVS組件的傳輸線脈沖(TLP)數據(初級鉗位)和IC接口引腳(次級鉗位)創建仿真來完成。

最終,您的目標是確認實現系統ESD保護所需的組件。為此,需完成以下步驟:

1. 創建ESD脈沖。

2. 加載Gerber文件。

3. 將所有其他組件加載到建模軟件中。

4. 運行仿真以確定RFFE引腳處的IEC應力水平。

5. 確定實現板載ESD保護所需的組件。

6. 將組件添加到模型中。

7. 重新運行仿真以驗證添加的組件是否有效。

8. 通過ESD測試后,進行最終的PC板布局。

1、使用IEC61000-4-2規范值來創建ESD脈沖

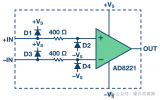

將如下所示的RLC(電阻-電感-電容)電路的模型原理圖加載到仿真工具中,并驗證是否得到如下所示的波形。該模型將仿真ESD脈沖。請注意,某些值可能需要調整才能獲得精確的波形。

2、加載Gerber文件

接下來,使用3D Gerber布局文件來評估PC板的走線。將這些文件放入建模軟件中。對布局軌跡進行建模,例如微帶線的尺寸。

3、將所有其他組件加載到建模軟件中

這些組件包括:

TLP I/O器件引腳數據

匹配組件

傳輸線組件

4、運行仿真

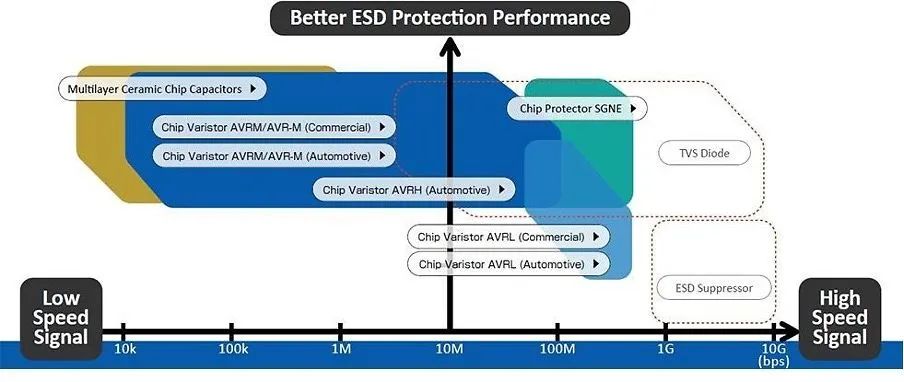

加載完所有組件后,您希望查看結果如何。此時,您要確定RFFE引腳的IEC應力水平。如果該水平值超出內部IC保護的能力,那么您將需要添加板載ESD保護,例如隔直電容、TVS二極管等。

5、確定實現板載ESD保護所需的組件

比較可用的各個保護組件,以確定最適合您設計的組件。例如,假設仿真顯示您的系統需要額外的板載保護。下圖顯示了通過比較TLP模型的數據查看的幾個組件。橙色線是采用Qorvo RFFE模塊端口的TLP模型。其他三個TLP模型是正在評估的TVS組件。根據以下TLP數據,組件1和組件2是兩個最佳選擇。它們都符合我們的系統要求;然而,進一步分析了位移回跳區域后,我們選擇組件1,因為它的觸發電壓更低。觸發電壓更低意味著TVS不太可能通過削弱系統信號性能影響我們的設計。

我們選擇了TVS組件后,將其放置在正確的板載位置也非常重要。如下圖所示,將TVS移近ESD入口點可以最大限度地降低ESD能量。PC板的走線可根據TVS位置增加和減少第一個峰值電流的幅度。

6、將組件添加到模型中

一旦選擇了ESD保護元件(在我們的示例中為TVS二極管),您需要將它們添加到仿真中,如下所示。

7、重新運行仿真以驗證添加的板載ESD組件是否有效

現在所有數據都加載到您的仿真中,您可以運行瞬態模擬,分析RF路徑的電流/電壓曲線,并調整內部引腳(例如模塊引腳)上的最小殘留值以及系統性能。

注意:緊湊型仿真器支持使用S參數數據進行瞬態模擬。S參數數據也可以在需要時轉換為集總模型。

最終目標是您的系統設計能通過IEC應力測試。不同的應用將需要不同的組件或戰略,而在設計階段初期對它們進行建模將有助于提高通過IEC認證的可能性。

8、進行最終的PC板布局

一旦您的設計通過了仿真,您就可以進行最終的系統PC板布局。使用SEED的不同之處在于,您直到完成板載ESD保護仿真與建模之后才進行系統PC板布局——而不是在設計階段的初期。

使用SEED提高通過ESD認證的可能性

SEED能夠更好地理解系統性能和IC ESD設計功能。IV-TLP曲線提供有關片上、模塊內和板載ESD功能的所需信息。將瞬態模擬添加到曲線圖上,即可評估片上和板載ESD保護器件的整體行為,以及它們在系統級ESD應力下的協同表現。這樣,從硬件開發的初始階段就能夠放心地構建最佳協同設計——最終可提高效率并降低總體設計成本。

-

ESD

+關注

關注

48文章

2029瀏覽量

172931 -

靜電放電

+關注

關注

3文章

286瀏覽量

44640 -

RF

+關注

關注

65文章

3050瀏覽量

166965

原文標題:干貨請Mark!用于優化 ESD RF 前端設計的 SEED 方法詳解

文章出處:【微信號:Qorvo_Inc,微信公眾號:Qorvo半導體】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

TPA2013D1功率是如何計算出來的,和哪些因素有關?

機房托管費用貴嗎?機房托管要考慮哪些因素?

mos管的選型主要考慮哪些因素

企業在選擇大帶寬服務器時需要考慮哪些其他因素?

選擇美國vps云主機時應該考慮哪些因素

ESD對電子元件的影響 如何選擇ESD保護元件?

TDK | 如何選擇ESD保護元件?

選擇ITX主板時要考慮的因素

晶振-振蕩模式如何選擇?涉及哪些因素?

在ModuStoolBox環境之外開發應用程序時應該考慮哪些因素?

電源模塊怎么選擇,考慮哪些因素 輸入輸出電壓尺寸保護BOSHIDA

高壓放大器的考慮因素有哪些

優化ESD RF前端設計要考慮哪些因素?

優化ESD RF前端設計要考慮哪些因素?

評論