引言

在當前光電子學系統中,以PC104 作為伺服控制分系統,體積龐大,不便于系統管理。 開發具有伺服控制能力的處理卡,用一塊板卡替代原來的系統,能簡化系統結構,提高系統 的集成度,使電子學系統最終成為一個高度集成的控制平臺。

CPCI(CompactPCI)總線在PCI 總線基礎之上,采用了歐洲卡結構,拋棄金手指式互 連方式,改用2mm 密度的針孔連接器,并具有可熱插拔性,使其具有了更高的可靠性和開放 性,并且能適應惡劣的工作環境,在工業控制、航空航天等領域得到廣泛應用。自行開發的 伺服控制卡基于CPCI 總線,以DSP 作為卡上控制CPU,與FPGA 結合實現控制。本論文以該 伺服控制卡為依托,在概述其硬件平臺結構的基礎上,介紹了在Windows 2000 下CPCI 設備 驅動程序的設計與開發,重點闡述了橋接芯片PCI9054 的DMA 數據傳輸實現及中斷處理機制。

1.伺服控制卡的系統結構與硬件實現方案

伺服控制卡以 TI 公司的TMS320F2812 DSP 作為核心處理器,與FPGA 結合來實現整 個板卡的控制功能,通過CPCI 總線完成與上位PC 機的通信,其系統功能框圖如圖1 所示:

圖 1 伺服控制卡硬件結構圖

FPGA 選用Altera 公司的EPF10K30A,它內嵌1536Byte 的RAM,此RAM 為主機與DSP 共享,用于上位機與DSP 之間的高速數據緩沖,FPGA 負責接收上位機傳遞的命令和參數 等數據,經處理后發送給DSP 進行相應的控制操作,同時反饋信息給上位機。 TMS32F2812 的主要任務就是完成復雜的伺服控制算法,特別是位置控制和速度控制。

FPGA 通過2812 的外部中斷XINT1 和XINT2 來觸發2812 接收控制命令和參數,2812 接收 到命令后,根據自身定義的工作協議進入相應的工作狀態。

系統設計中采用 PLX 公司的PCI9054 作為總線接口芯片,實現CPCI 局部總線與FPGA 的通信。PCI9054 采用C 模式,在該模式下,PCI 的數據線與地址線是非復用的,設計時只 需關注9054 的本地端總線。

2.WDM 驅動程序設計

在Windows 環境下,位于用戶態的應用程序不能之間訪問硬件資源,而要通過執行核 心態的驅動程序來間接完成對硬件資源的訪問,因此,對于上位機上的應用程序,要對伺服 控制卡進行訪問,必須要為其開發驅動程序。

WDM 驅動程序是一種Pnp 驅動程序,它能夠實現Windows 98 與Windows 2000 、 Windows XP 之間的源代碼級兼容。Windows 2000 性能穩定,在調試自行開發的板卡時,仍 然是首選的操作系統。在Windows 2000 中,所有對驅動程序的I/O 請求都轉化為I/O 請求 包(IRP)來表示,IRP 是I/O 管理器在響應I/O 請求時從非分頁系統內存中分配的一個可變 大小的數據結構,I/O 管理器負責產生代表一次I/O 操作的IRP,并將IRP 傳至正確的設備 驅動程序,并通過分層的驅動程序傳遞給物理設備。設備驅動程序則接收IRP,執行相應的 操作,完成后再將IRP 傳送回I/O 管理器,表示I/O 操作的完成或者通過I/O 管理器將其傳 遞給其他的驅動程序進行進一步的處理。

3.伺服控制卡的WDM 驅動程序設計與實現

驅動程序的開發環境常用的有微軟的DDK、Jungo 的WinDriver 和Numega 的Driver Studio。Driver Studio 把DDK 封裝成類,包含完善的代碼生成和調試工具,并且提供對WDM 驅動的完全支持,利用它開發的核心態驅動程序運行效率也很高。本系統在VC 環境下利用 Driver Studio 開發驅動程序。

接口芯片 PCI9054 支持主模式、從模式和DMA 模式三種數據傳輸方式。DMA 傳輸不 通過處理器,直接進行數據交換,可以節省CPU 資源;并且DMA 模式還支持CPCI 總線與本 地總線之間的高效突發。

3.1 DMA 數據傳輸實現

PCI9054 集成了兩個互相獨立的DMA 通道,每一個通道由一個DMA 控制器和一個專 用雙向FIFO 組成,都支持塊DMA 和分散/集中DMA 操作,這里選用DMA 通道0,采用塊 DMA 方式實現傳輸。在Driver Works 中提供了三個類來實現DMA傳輸,分別是KDmaAdapter 類、KDmaTransfer 類和KCommonDmaBuffer 類。

3.1.1.DMA 適配器

對于DMA 傳輸,驅動程序需要創建一個DMA 適配器,來表明一個DMA 通道的特性 和提供串行化訪問的服務。KDmaAdapter 類實現對DMA 適配器的操作。在它的初始化函數 Initialize(PDEVICE_DESCRIPTION pDesc,PDEVICE_OBJECT pPdo)中第一個參數是一個 DEVICE_DESCRIPTION 結構的指針,這個參數用于對DMA 通道的屬性進行設置。

3.1.2. DMA 控制器

采用 DMA 方式時,CPU 要放棄對系統總線的使用權,主存儲器和外部設備是被控制的對 象,它們之間沒有相互控制的能力,需要利用DMA 控制器來代替CPU 完成控制功能。

在用DriverWorks 開發驅動時, KDmaTransfer 類用于控制DMA 的傳輸;它可以啟動一個DMA 傳 輸,指定DMA 傳輸的方向,DMA 傳輸數據緩沖區的物理地址和要傳輸的字節數。 KDmaTransfer 類的Initiate()函數用于初始化一個KDmaTransfer 對象;在成功初始化 一個KDmaTransfer 類對象后,將會調用DMA 準備就緒回調例程OnDmaReady,在該例程中獲 取要傳輸的內存的地址和字節數,并調用StartDMA 例程開始DMA 傳輸。

與中斷結合的DMA 傳輸在一次傳輸結束后會再次調用 KDmaTransfer 類的Continue()函數發起下一次的DMA 傳輸操作,直到傳輸完成。

3.1.3. DMA 公共緩沖區

在DriverWorks 中KCommonDmaBuffer 類實現對公用緩沖區的操作。在實際使用時,聲 明一個KCommonDmaBuffer 類對象并初始化。在傳輸結束后,釋放公共緩沖區,以防止內存 丟失。

3.1.4. 寄存器設置

PCI9054 在DMA 模式下傳輸,驅動程序要通過I/O 指令設置DMA 控制器內部的寄存器 以實現兩總線間的數據傳送,需要設置的內部寄存器及其具體功能如下表1 所示:

3.2 驅動開發中的中斷處理機制及實現

本系統的驅動程序采用塊DMA 與中斷結合的方式來實現主機與伺服控制卡之間的數 據傳輸。以讀操作為例,每次DMA 傳輸完后,都會產生一個DMA 中斷,中斷處理程序應 答中斷,并獲取公共緩沖區中的數據,通知主機端有數據到達;可以看出,高效的DMA 處 理依賴于高效的中斷處理過程。

中斷處理完成 CPU 與I/O 設備之間的信息交換,在為硬件板卡開發驅動程序時需要為 中斷配置相應的驅動處理。在處理中斷之前要對中斷資源進行配置,首先定義并初始化一個 中斷對象,在初始化階段,提取IRP 資源中的中斷級別、中斷模式、中斷向量、共享模式 等信息。利用上面獲得的參數來連接中斷,連接中斷操作的主要目的是注冊設備驅動的中斷 服務例程(ISR),以便在中斷發生后中斷服務例程能夠被調用。在DriverWorks 中用KInterrupt 類實現對硬件中斷的處理。

status = m_Irq.InitializeAndConnect(pResListTranslated, LinkTo(Isr_Irq), this)

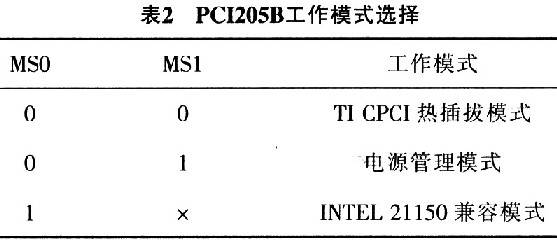

當硬件發生中斷時,硬件抽象層(HAL)把中斷級別(IRQL)提升到合適的中斷級別, 然后調用中斷服務例程(ISR)。CPCI 總線是中斷共享的,因此,ISR 首先確定是哪一個設 備發生了中斷, 如果不是當前設備的中斷,立即返回FALSE ,以便HAL 把中斷發送給其 他設備的驅動程序。如果是當前設備的中斷,則在清除該中斷,并做相應的處理。中斷處理 的整個過程如下圖2 所示:

ISR 執行在高于DISPATCH_LEVEL 的IRQL 上,它凍結了其CPU 上所有低于或等于該 IRQL 上的其他活動,為了提高系統性能,ISR 例程應該盡可能快的完成;此外,ISR 中使 用的所有代碼和數據必須存在于非分頁內存中,能調用的內核模式函數也十分有限。

圖2:中斷處理流程圖

Windows 2000 提供了延遲過程調用(DPC)機制來解決這個問題,ISR 決定當前請求的 完成并請求一個DPC,之后,內核在DISPATCH_LEVEL 級上調用這個DPC 例程。當有當 前設備的中斷到來時,把一個DPC 插入到DPC 隊列中。實現代碼如下:

m_DpcFor_Irq.Setup(LinkTo(DpcFor_Irq), this);//創建一個DPC m_DpcFor_Irq.Request(NULL, NULL)// 把一個DPC 插入到DPC 隊列等待執行

4. 應用程序與驅動程序的通信

4.1 通信的實現策略

應用程序采用Win32 事件通知的方式與驅動程序進行通信:應用程序調用API 函數 CreatFile 打開設備,調用CreateEvent 創建事件句柄hEvent 并置為無信號態,把hEvent 作為 函數DeviceIoControl 的參數傳遞給驅動程序,同時調用CreateThread 創建等待線程;WDM 驅動程序接收事件句柄hEven,初始化KEvent 類對象m_hEvent,當中斷發生時,在DPC 中 執行m_hEvent-》Set(),將事件設置為信號態,喚醒應用程序中的等待線程,然后調用 DeviceIoControl 完成數據傳輸。

4.2 數據傳輸速率測量

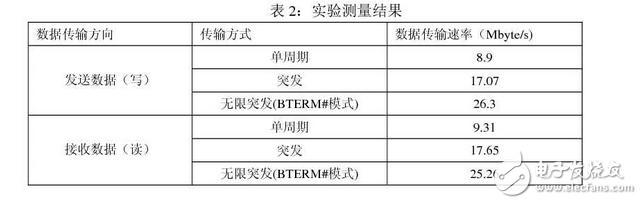

在實際測量時,采用了硬件測量法,應用程序不斷向DSP 處理卡發送數據/接收數據, 利用示波器來觀測BLAST#和ADS#信號的變化周期,得出每組數據的傳輸時間。該DSP 卡本地端總線為8 位,在DMA 模式下,測得的發送/接收時的測量結果如下表2 所示:

從以上結果可以看出,無限突發 DMA 模式傳輸速率最高,可達26.3Mbyte/s,若本地端總線 為32 位,則數據傳輸速率可以達到26.3*4=105.2Mbyte/s ,接近32 位PCI 總線的極限傳輸速率133Mbyte/s,能夠滿足大部分高速數據傳輸要求。

結束語

自行開發的伺服控制卡,基于高速的CPCI 總線,以DSP 作為卡上處理器,以FPGA 實現邏輯處理,能夠作為一個獨立的單元替代原來的工控機子系統,大大簡化了當前光電子 學系統結構;利用Driver Studio 為其開發的底層驅動程序,能使板卡在Windows2000 下穩 定地工作,在與中斷結合的DMA 數據傳輸模式下,數據傳輸速率能夠滿足伺服控制卡的精 度和實時性要求。

-

WDM

+關注

關注

1文章

109瀏覽量

20991 -

CPCI

+關注

關注

6文章

70瀏覽量

32829 -

伺服卡

+關注

關注

0文章

2瀏覽量

7448

發布評論請先 登錄

相關推薦

TFF型WDM器件技術原理

WINDOWS下PCI接口卡WDM驅動程序的DMA編程技術

基于CPCI的伺服卡的DMA和中斷研究

Windows環境下開發PCI接口卡DMA應用的WDM編程技

基于CPCI總線的伺服控制卡的設計和實現

WDM/DWDM技術,什么是WDM/DWDM技術

基于CPCI總線的多網口卡設計

Windows 2000下WDM驅動程序的研究與開發

CPCI轉PCI載板轉接卡 PCI2CPCI

CPCI技術下對伺服卡WDM設計與研究

CPCI技術下對伺服卡WDM設計與研究

評論