時脈是許多系統如PC、打印機、視訊轉換器、高階工件站及各種通訊產品的必要組件。CY22150是一款具有立即編程能力的全新可編程時脈發生器,可為各種電信、高容量儲存及多媒體應用系統等領域,提供高頻寬、低雜訊與高精準度的輸出信號,具備高度完整的客制化功能,支持6組可設定輸出,輸出頻率范圍大。本文就CY22150實際應用展開討論,介紹了一種實際可行的接口電路。

1 CY22150器件簡介

1.1 主要特點和引腳功能

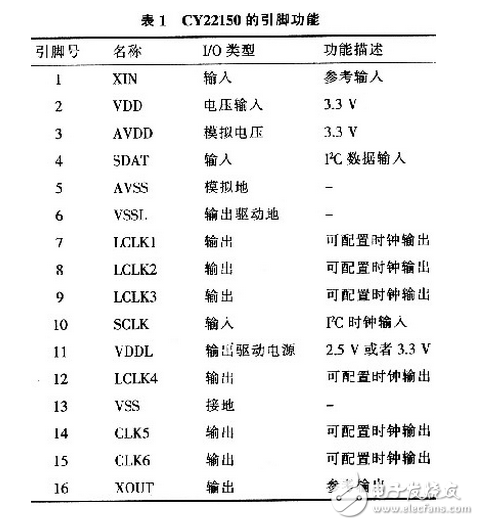

CY22150系列器件有CY225IOFC和CY2251OFI兩款,它們的引腳排列如圖1所示,采用16引腳的TSSOP封裝。表l所列是其引腳功能。

CY22150的主要特點為:內部集成一個鎖相環,能夠產生低偏移、低抖動、高精確度的輸出;輸出頻率的最大值是200 MHz,參考輸入頻率可以由外部晶振產生,也可由外部時鐘驅動源產生;為易變、系統級、用戶化的特定頻率和選擇提供工業標準接口;串行接口、可再次編程允許設計的快速更改和產品性能的快速提高;適用于商業、工業、網絡、通信等一般性應用,常見于標準和低電壓的系統;I2C串行接口工作在100 kHz或者400 kHz。

1.2 輸出頻率計算及寄存器設置

1.2.1 頻率計算

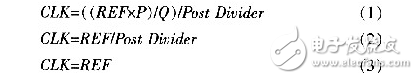

CY22150是一個非常靈活的時鐘發生器,由4個基本變量決定最終的輸出頻率,分別是輸入參考頻率(REF),內部分頻器P和Q,以及靈活計算頻率值的Post Divider。以下是3個可用的決定最后輸出頻率的公式:

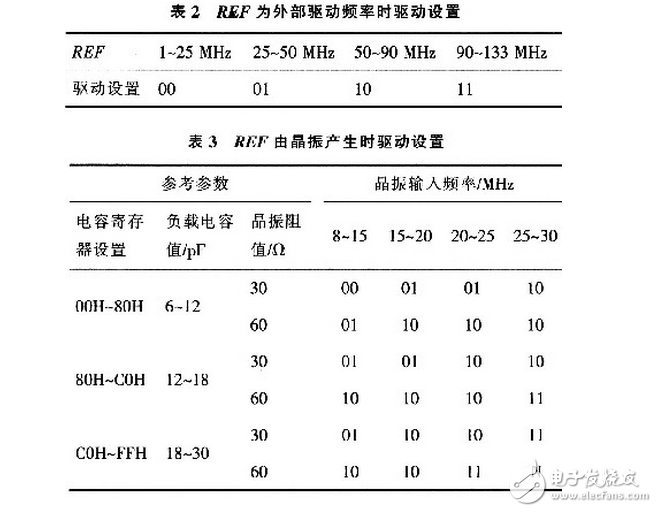

CY22150PLL基本模塊表如圖2所示。CY22150的6個輸出時鐘中的每一個都有7種可用的選擇。6個分頻器分別為/2,/3,/4,/DIV1N,/DIV2N,其中DIV1N和DIV2N是根據實際輸出需要進行設定的。這些分頻器的值(Post Divider)可以直接應用于式(1)和式(2),計算最后的時鐘頻率。第7種情況是直接輸出參考輸入頻率,即常說的bypass通路。

1.2.2 寄存器設置

使用CY22150時,可以使用缺省的輸出,用戶也可以根據自己的實際需要設定寄存器的值。缺省狀態下,所有的Bit位都設置為0,所有的輸出都是三態,且晶振電路是活躍的。

CY22150作為服務器件使用時,其地址是69H(1101001),內部所有寄存器的地址和寄存器的值都是8 Bit。CY22150內部有11個可控制的寄存器,其使用主要是這些寄存器的配置。寄存器設置參見文獻。它們分別是時鐘使能寄存器(09H),Bank1分頻控制寄存器(0CH),輸入晶振控制寄存器(12H),輸入負載電容控制寄存器(13H),電荷泵及PB計數器寄存器(40H,41H),P0、Q計數器寄存器(42H),交叉點開關矩陣控制寄存器(44H,45H,46H),Bank2分頻控制寄存器(47H)。

以下結合式(1)說明CY22150使用中比較重要的寄存器的配置:

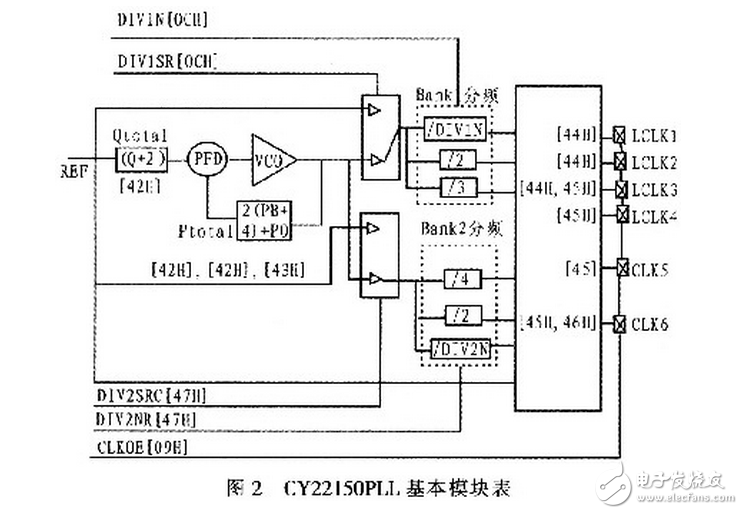

1)參考頻率(REF) REF可以是晶振產生的,也可以是外部驅動頻率。若由晶體產生,REF的范圍是8~30 MHz,若為外部驅動頻率,REF的范圍是1~133 MHz。與REF的設定相關的Bit是輸入晶振控制寄存器(12H)的4、5位,其具體設定與REF的范圍及晶振屬性有關,具體如表2和表3所示。

2)Q計數器 Q計數器的值是由PO、Q計數器寄存器(42H)的低7位確定的,Qtotal的計算由式(4)決定,其范圍是2~129。

在具體的使用中,為了保證CY22150穩定工作,REE/Qtotal的值不可高于250 kHz。

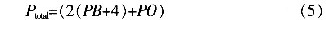

3)P計數器 PLL的輸出頻率是由Q和P共同決定的,Ptptal由PB和PO這2個內部變量決定,計算由式(5)決定。

PB是一個10 Bit的變量,由寄存器40H的低2位和41H的全8位決定;PO是一個1 Bit的變量,由寄存器42H的最高位決定,它的引入確保了PB是整數,當Ptotal是奇數時,PO為1,Ptotal是偶數時,PO為0。

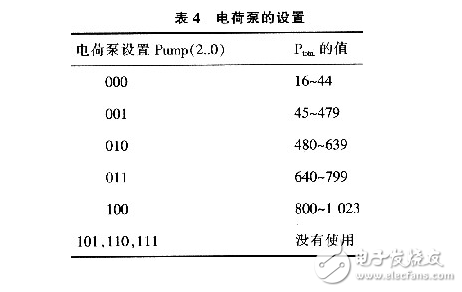

Ptotal的可用范圍是8~2 055,為了確保CY22150穩定的工作,(Ptotal(REE/Qtotal))應該在100~400 MHz之間。為了使PLL穩定工作,Ptotal的范圍規定為16~1 023,在具體的應用時Ptotal不同,寄存器40H的4..2設置不同,其設置與Ptotal的值有關,如表4所示。

4)時鐘輸出的設置 VC0的輸出被接到兩個多控開關,最后的時鐘輸出由兩個分頻板決定。分頻的選擇共有以下幾種:/2,/3,/4,/DIVxN,其中DIVxN是可變的。兩個多控開關(DIVlSRC和DIV2SRC)決定最后的輸出時鐘是由哪個分頻板得到的,DIV1SRC的控制位置為0是表示選通了Bank1,DIV2SRC的控制位置為0是表示選通了Bank2。每一個時鐘輸出都可以是7種頻率源之一,CLKSRC(2..0)交叉開關矩陣的設置決定最后的時鐘輸出,相應的控制位在交叉點開關矩陣控制寄存器(44H,45H,46H)中設定。時鐘輸出由時鐘使能寄存器(09H)的低6位決定,控制位為1,表示該輸出被選定。

2 典型應用

2.1 硬件電路

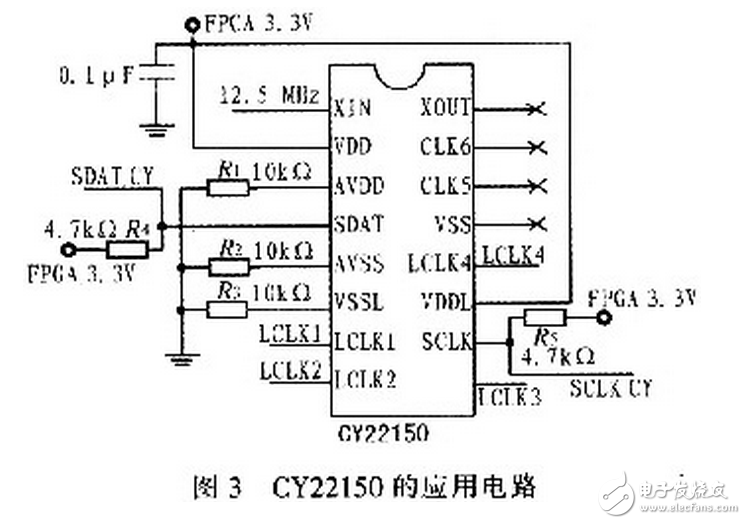

CY22150的應用電路如圖3所示(機頂盒電路的一部分)。該電路為XC3S1400AFG676型低成本的Spartan_3AFPGA器件,提供時鐘信號,根據FPGA工作的需要提供不同頻率的時鐘。CY22150輸入信號是12.5 MHz(引腳1),輸出時鐘是LCLK1(引腳7)、LCLK2(引腳8)、LCLK3(引腳9)、LC LK4(引腳12)分別接XC3Sl400AFG676的IO_L28P_2/GCLK2(52引腳)、IO_L28N_2/GCLK3(51引腳)、IO_L27P_2/GCLKO(50引腳)、IO_L27N_2/G CLK1(49引腳),這8個引腳的連接保證CY22150為XC3S1400AFG676提供工作時鐘。CY22150的I2C數據輸入(引腳4)接XC3S1400AFG676的IO_L29N_ 2(53引腳),CY22150 I2C時鐘輸入(引腳15)接XC3S1400AFG676的IO_L29P_2(54引腳),這4個引腳的連接保證電路控制數據、工作時序的一致。圖3中“×”表示該引腳沒有連接。

在該電路中,XC3S1400AFG676需用4個時鐘接口,CY22150有7個可用的時鐘輸出。采用CY22150,一個時脈發生器可提供電路需要的4個時鐘(如果采用ICD2053,只有1個時鐘輸出的時脈發生器),這樣降低了開發成本,縮小產品的體積,對一個時脈發生器控制就可同時產生電路所需的4種不同頻率,操作簡單。在電路的設計中,保證電路穩定工作,在接地和接電源處要接不同電容值的電容或者不同阻值的電阻來減小干擾。

2.2 軟件設計

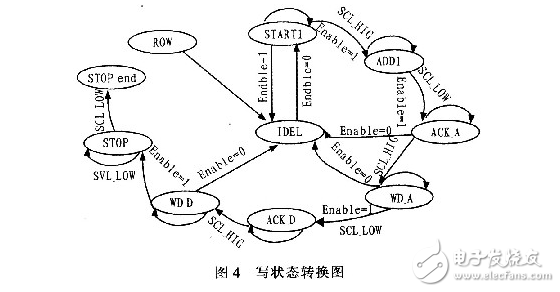

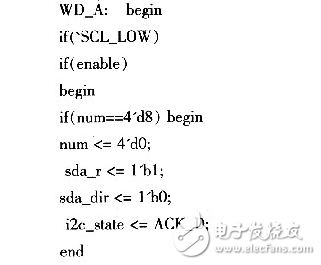

在該應用中,主要實現對CY22150的寫控制。寫控制的主要過程描述如下:產生開始信號,寫器件地址及寫控制位,ACK響應,寫寄存器地址,ACK響應,寫寄存器的值,ACK響應,產生停止信號。其狀態轉換圖如圖4所示。整個過程中,關鍵是實現相應寄存器的寫,以下程序實現的是某一寄存器的寫,其他寄存器的寫過程與之相似。

其相關程序代碼:

2.3 寄存器設置舉例

電路中輸入頻率是12.5 MHz,某工作條件下CY22150輸出的頻率148.5 MHz,REF選用外部驅動時鐘,各寄存器的設定過程如下:

1)REF是12.5 MHz的外部驅動時鐘,所以地址為12H的寄存器的值為0010~0000。

2)采用的輸入是外部時鐘源,所以CapLoad使用默認值0,地址為13H的寄存器的值為0000~0000。

3)根據以上對P、Q計算的說明,設置為:Qtotal=30,REF/30》250 KHz,Q=28,=713,PO=l,PB=352 (采用2分頻輸出)。地址為40H的寄存器的值為1100~1101;地址為41H的寄存器的值為0110~0000;地址為42H的寄存器的值為1001~1100。

4)最后4個時鐘都有輸出,所以地址為09H的寄存器的值為0000~1111。

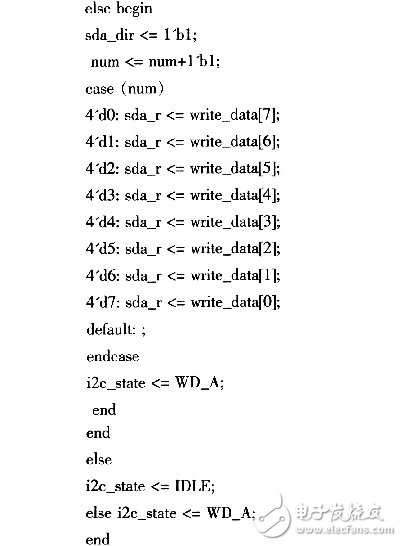

選用Bank2,2分頻,相關的寄存器的設置如表5所示。其仿真結果如圖5所示。

結論

本文提供的硬件電路及寄存器配置值已經在實際應用中得到驗證,是完全正確的。需要注意的是,為保證電路時序的一致,完成一個寄存器的寫需要產生3個STOP信號才可跳轉到下一個寄存器的寫控制。CY22150是程式化的時脈發生器,適合用來支持需高精準度與高穩定度的多埠時脈應用。

-

寄存器

+關注

關注

31文章

5356瀏覽量

120564 -

分頻器

+關注

關注

43文章

447瀏覽量

49969 -

時脈發生器

+關注

關注

0文章

2瀏覽量

5777

發布評論請先 登錄

相關推薦

時脈發生器CY22150器件介紹及應用

時脈發生器CY22150器件介紹及應用

評論