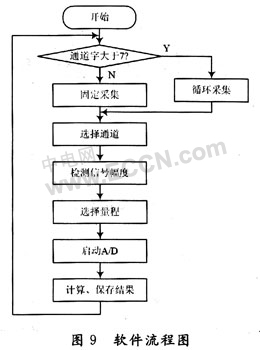

繼電保護(hù)或者測控裝置都需要同步采集多路的電壓或者電流信號(hào),現(xiàn)在一般的實(shí)現(xiàn)方式都是用多路逐次逼近型ADC(譬如AD7656或者ADS8-556)實(shí)現(xiàn)多路同步數(shù)據(jù)的采集,這種方案采樣速度高、控制簡單,但是每一通道都需要基于運(yùn)算放大器的抗混疊濾波器,所以實(shí)現(xiàn)起來成本高、占用PCB面積大。本文提出一種使用CS5451A模數(shù)轉(zhuǎn)換芯片實(shí)現(xiàn)多路同步數(shù)據(jù)采集的實(shí)現(xiàn)方案,這種實(shí)現(xiàn)方式電路簡單、成本低。在本方案中,處理器選用的是飛思卡爾MPC8313處理器,主頻333 MHz。CS5451A如果用CPU直接控制,由于CS5451A芯片輸出數(shù)據(jù)速率低,處理器與ADC速度嚴(yán)重失配會(huì)大大占用CPU的開銷,本文提出一種利用XILINX可編程邏輯芯片FPGA實(shí)現(xiàn)異步FIFO和串并轉(zhuǎn)換模塊來實(shí)現(xiàn)采樣數(shù)據(jù)的接收的方法,串并轉(zhuǎn)換模塊只需要接收一幀數(shù)據(jù),存到異步FIFO后,向CPU發(fā)出一個(gè)中斷信號(hào),在中斷服務(wù)子程序中CPU讀走FIFO中的數(shù)據(jù),這樣可以大幅度提高CPU的利用率,系統(tǒng)結(jié)構(gòu)簡單,易于實(shí)現(xiàn)。

1 CS5451A概述以及電路的設(shè)計(jì)

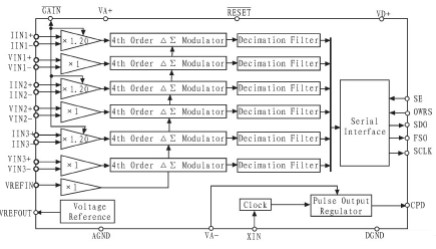

CS5451A是Cirrus Logie公司設(shè)計(jì)的一款高度集成的模數(shù)轉(zhuǎn)換芯片。在一個(gè)硅片上集成了6個(gè)△-∑A/D轉(zhuǎn)換器,6個(gè)數(shù)字濾波器和一個(gè)與微控制器或DSP相聯(lián)接的串行接口。CS5451A包括3個(gè)電壓測量通道、3個(gè)電流測量通道,它們的主要區(qū)別是3個(gè)電流測量通道的運(yùn)算放大器的增益是可以更改的,可以設(shè)置成1倍或者20倍,而電壓通道的增益固定為1倍。由于△-∑A/D轉(zhuǎn)換器采用過采樣技術(shù)以及數(shù)字濾波器,所以簡化了ADC前級(jí)的抗混疊濾波器的設(shè)計(jì)。在本設(shè)計(jì)中抗混疊濾波器只設(shè)計(jì)了1階低通濾波器。CS5451A結(jié)構(gòu)框圖如圖1所示。

圖1 CS5451A結(jié)構(gòu)框圖

在本設(shè)計(jì)中CS5451A的配置如下:

1)ADC電流通道增益設(shè)置為1倍增益,這樣,6個(gè)通道增益都為1,電流通道和電壓配置一樣,每一通道不再有區(qū)別,容易做成通用的模擬輸入設(shè)計(jì)。

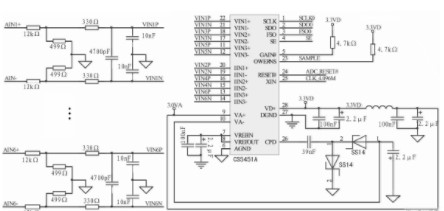

2)最大輸入范圍為+20 V,互感器輸出的電壓信號(hào)通過電阻分壓網(wǎng)絡(luò)產(chǎn)生一個(gè)最大為±800 mV的電壓信號(hào),通過一介低通濾波器進(jìn)入ADC芯片,CS5451A電路設(shè)計(jì)如圖2所示。

圖2 CS5451A電路設(shè)計(jì)

3)使用內(nèi)部1.2 V參考電源。

4)時(shí)鐘輸入為4.096 MHz。

5)數(shù)據(jù)輸出速率4.0 k還是2.0 k由CPU控制。

2 異步FIFO的設(shè)計(jì)

本設(shè)計(jì)中所用的FPGA芯片是XILINX公司的XC3S100E,XC3S100E是XILINX SPARTAN3E系列一款最低容量的FPGA芯片,此系列FPGA利用90 nm工藝實(shí)現(xiàn)低成本高容量的需求,XC3S100E具有以下資源:

1)有2160個(gè)邏輯單元;

2)具有RAM資源87 kB(其中BLOCK RAM 72 kB,分布式RAM 15 kB);

3)具有兩個(gè)DCM;

4)具有4個(gè)乘法器;

5)可以實(shí)現(xiàn)FIFO等多個(gè)IP核。

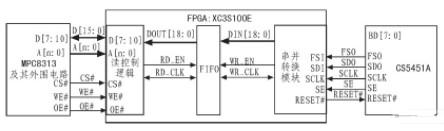

在XILINX ISE10.1集成開發(fā)工具下,很容易利用XININX免費(fèi)IP核實(shí)現(xiàn)一個(gè)異步FIFO。異步FIFO是在兩個(gè)相互獨(dú)立的時(shí)鐘域下,數(shù)據(jù)在一個(gè)時(shí)鐘域?qū)懭隖IFO,而在另外一個(gè)時(shí)鐘域下又從該FIFO中將數(shù)據(jù)讀出。CS5451A控制系統(tǒng)框圖如圖3所示,異步FIFO和串并轉(zhuǎn)換模塊作為CPU和CS5451A之間的橋梁,由串并轉(zhuǎn)換模塊將ADC輸出的串行數(shù)據(jù)轉(zhuǎn)換成19位的并行數(shù)據(jù)(其中16位為數(shù)據(jù),3位為采樣通道號(hào)0~5)寫入異步FIFO,這樣FIFO就成為CPU前端的一個(gè)緩沖器。每接收完成1幀數(shù)據(jù)便向CPU發(fā)出一個(gè)中斷信號(hào),通知CPU讀取FIFO中的數(shù)據(jù)。

圖3 CS5451A控制系統(tǒng)框圖

異步FIFO IP核的參數(shù)指標(biāo)直接影響FIFO的讀出速度,首先,F(xiàn)IFO的讀出速度快能夠減少CPU的開銷,這樣CPU可以有更多的時(shí)間干實(shí)時(shí)性更高的任務(wù)。其次,F(xiàn)IFO的存儲(chǔ)深度要適宜,深度過大造成資源的浪費(fèi),深度過小會(huì)造成控制復(fù)雜,這樣將占用更多的資源。本設(shè)計(jì)中的異步FIFO是利用ISE10.1中的參數(shù)化的IP核在XC3S100E芯片的實(shí)現(xiàn)。由于1個(gè)CS5451A芯片共有6通道ADC,ADC的分辨率為16位,考慮到數(shù)據(jù)的可靠性,每一個(gè)ADC通道的數(shù)據(jù)包括通道號(hào)(占3位),考慮到有的時(shí)候可能CPU不能及時(shí)的讀走數(shù)據(jù),所以在參數(shù)化的FIFO設(shè)計(jì)中選擇FIFO深度為64,寬度為19位。

3 基于FPGA串并轉(zhuǎn)換模塊的設(shè)計(jì)

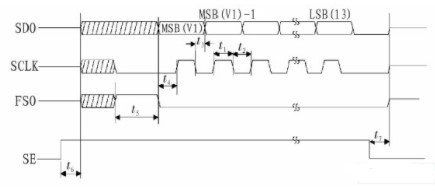

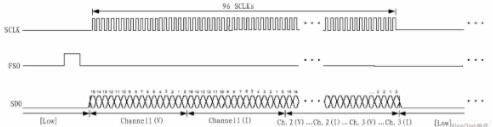

CS5451A通過一個(gè)Master模式的串行接口輸出采樣數(shù)據(jù),輸出數(shù)據(jù)通過SDO輸出,SCLK為輸出串行時(shí)鐘,CS5451A串行輸出時(shí)序圖如圖4所示,F(xiàn)SO是幀同步信號(hào),表示一幀數(shù)據(jù)的開始,如果SE信號(hào)為高電平,這3個(gè)信號(hào)就有效,如果為低電平,3個(gè)信號(hào)都為高阻狀態(tài),在本設(shè)計(jì)中,CPU初始化后把SE設(shè)置成高電平。正常情況下,F(xiàn)SO信號(hào)為低電平,當(dāng)有一幀數(shù)據(jù)要輸出的時(shí)候,F(xiàn)SO信號(hào)變?yōu)楦唠娖剑唠娖綄挾葹?個(gè)SCLK周期。當(dāng)沒有數(shù)據(jù)輸出的時(shí)候,SCLK為低電平,F(xiàn)SO從高電平變?yōu)榈碗娖胶螅琒CLK時(shí)鐘信號(hào)有效,數(shù)據(jù)在上升沿輸出,SCLK共持續(xù)16x6個(gè)周期,數(shù)據(jù)串行輸出時(shí),MSB最先輸出。

圖4 CS5451A串行輸出時(shí)序圖

由于SCLK頻率很低,在用CPU的SPI控制器接收數(shù)據(jù)的時(shí)候,CPU接收一位的時(shí)間為4tXINe=1μs,如圖5所示,一幀數(shù)據(jù)為96位,接收一幀數(shù)據(jù)大約為96μs的時(shí)間,如果用CPU通過異步FIFO讀取數(shù)據(jù),因?yàn)楝F(xiàn)在的控制器總線速度很快,假設(shè)讀一個(gè)字節(jié)數(shù)據(jù)需要100 ns,讀走一幀數(shù)據(jù)大約需要100 ns×12=1.2μs(由于MPC8313總線寬度為16位,不能一次讀取19位數(shù)據(jù),所以在讀取FIFO中數(shù)據(jù)的時(shí)候,把通道號(hào)鎖存到一個(gè)暫存寄存器中,讀取采樣數(shù)據(jù)后再讀取通道號(hào),所以讀取一幀數(shù)據(jù)需要12次)。只有原來的大約1/80的時(shí)間,提高了CPU的利用效率。

圖5 CS5451A一幀數(shù)據(jù)輸出圖

4 中斷服務(wù)子程序的設(shè)計(jì)

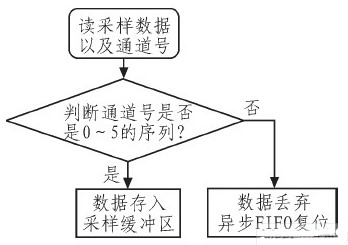

CPU讀采樣數(shù)據(jù)是在中斷服務(wù)子程序中設(shè)計(jì)的,在中斷程序中讀走采樣值數(shù)據(jù),并判斷通道號(hào)是否對應(yīng)。軟件流程如圖6所示。

圖6 軟件流程圖

5 結(jié)論

本文利用CS5451A設(shè)計(jì)一個(gè)通用的多路數(shù)據(jù)采集系統(tǒng),利用XILINX SPARTAN3E系列FPGA芯片實(shí)現(xiàn)異步FIFO和采樣數(shù)據(jù)串并轉(zhuǎn)換模塊的設(shè)計(jì),CPU不用直接用SPI控制器接收CS5451A芯片輸出的串行格式的數(shù)據(jù),只需要把ADC輸出的串行數(shù)據(jù)通過串并轉(zhuǎn)換模塊存入FIFO緩沖區(qū),并產(chǎn)生一個(gè)中斷信號(hào),在CPU的中斷子程序中讀出采樣數(shù)據(jù)。該方案已經(jīng)在低壓繼電保護(hù)裝置中得到了應(yīng)用,通過試驗(yàn)本系統(tǒng)的數(shù)據(jù)采集精度可以達(dá)到0.2級(jí)。調(diào)試中發(fā)現(xiàn),在進(jìn)行PCB設(shè)計(jì)時(shí),要注意以下幾點(diǎn):

1)模擬部分電路(差分輸入以及參考電源部分)和數(shù)字部分(XIN、FSO、SDO、SCLK信號(hào))應(yīng)完全分開在不同的區(qū)域里。

2)良好的去耦對抑制CS5451A產(chǎn)生的噪聲很重要,去耦電容一般為0.1 μF,且放到電源輸入引腳盡可能近的地方,以達(dá)到良好的去耦效果。

3)如果系統(tǒng)要求工作在-40~+85℃的溫度范圍內(nèi),要求采樣精度達(dá)到0.2級(jí),必須使用外部高精度的參考電源。

-

FPGA

+關(guān)注

關(guān)注

1630文章

21766瀏覽量

604582 -

芯片

+關(guān)注

關(guān)注

456文章

51004瀏覽量

425212 -

控制器

+關(guān)注

關(guān)注

112文章

16412瀏覽量

178713

發(fā)布評論請先 登錄

相關(guān)推薦

基于LabVIEW的單片機(jī)多路數(shù)據(jù)采集系統(tǒng)的設(shè)計(jì)

多路數(shù)據(jù)采集系統(tǒng)

如何設(shè)計(jì)多路數(shù)據(jù)采集系統(tǒng)中FIFo?

采用單片機(jī)AT89S52與24位A/D芯片CS5532設(shè)計(jì)的多路數(shù)據(jù)采集系統(tǒng)

設(shè)計(jì)一個(gè)八路數(shù)據(jù)采集系統(tǒng)

基于FPGA的高速多路數(shù)據(jù)采集系統(tǒng)的設(shè)計(jì)

利用CPLD實(shí)現(xiàn)多路數(shù)據(jù)采集

高精度多路數(shù)據(jù)采集系統(tǒng)原理及設(shè)計(jì)

基于CS5451A的多路同步數(shù)據(jù)采集系統(tǒng)

于FPGA的高速多路數(shù)據(jù)采集系統(tǒng)的設(shè)計(jì)

基于ARMCortex_M3的多路數(shù)據(jù)采集系統(tǒng)的設(shè)計(jì)

SPI總線的多路數(shù)據(jù)采集系統(tǒng)的設(shè)計(jì)

多路數(shù)據(jù)采集系統(tǒng)設(shè)計(jì)

基于FPGA的高速多路數(shù)據(jù)采集系統(tǒng)的設(shè)計(jì)方案詳細(xì)資料說明

利用CS5451A實(shí)現(xiàn)通用的多路數(shù)據(jù)采集系統(tǒng)的設(shè)計(jì)

利用CS5451A實(shí)現(xiàn)通用的多路數(shù)據(jù)采集系統(tǒng)的設(shè)計(jì)

評論