高速、寬分頻范圍的可編程頻率分頻器設計一直是射頻頻率綜合器設計中的難點,它的工作速度限制了頻率合成器輸出信號的最高頻率,它的相位噪聲影響頻率合成器的帶內相位噪聲。文中設計的可編程分頻器應用于移動數字電視接收機調諧芯片,該芯片兼容了DVB-H、DAB標準,接收的頻段覆蓋了460~900 MHz,1 400~1 500 MHz這兩個頻段。根據整個芯片的系統方案設計,可編程分頻器的工作頻率為2.4~4.0 GHz,實現的分頻比范圍為240~400,且為連續的。目前高速可編程分頻器主要包括基于雙模預分頻的吞脈沖分頻器和基于基本分頻單元的多模分頻器兩種結構,前者因高速、結構簡單等特點,被廣泛應用在射頻頻率綜合器當中,同時,整個可編程分頻器單元模塊都采用基于源極耦合(SCL)結構的模擬電路實現,相對于在低頻分頻部分采用數字標準單元具有噪聲低、版圖面積小等優點。檢測和置數邏輯時序的設計是可編程分頻器設計的重點,它直接影響到分頻器的工作頻率。本文中提出一種新的檢測和置數邏輯及電路實現,使得整個可編程分頻器的工作頻率提高了1倍。本文首先給出r可編程分頻器設計的整體結構,著重描述了可編程分頻器檢測和置數邏輯電路的改進方案;最后,給出了版圖設計以及電路后仿真結果。

1 可編程分頻器的結構

1.1 整體結構設計

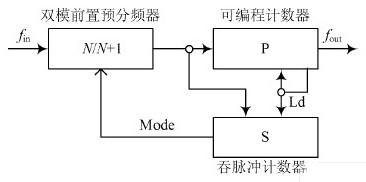

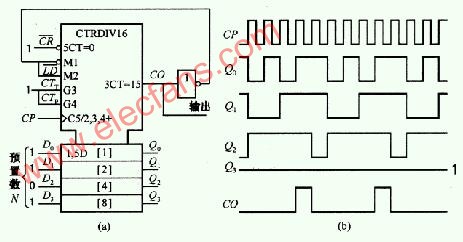

基于雙模預分頻器的可編程分頻器結構如圖1所示,它由3部分構成:N/N+1雙模前置預分頻器、可編程計數器、吞脈沖計數器。

輸入的頻率首先經過預分頻器進行分頻,分頻比由吞脈沖計數器S給出一個信號Mode進行控制。可編程計數器P和吞脈沖計數器S同時開始減計數,當S計數器減計數減為0時,雙模預分頻器分頻比由N+1變為N,S計數器停止計數,P計數器繼續減計數;當P計數器減計數到0時,通過反饋回路使P,S計數器重新置數,開始新一輪的計數。因此在每一次計數過程中首先進行了S次N+1分頻,再進行了P-S次N分頻,故輸出信號為:

分頻比M=PN+S。

根據調諧器芯片系統所需要的頻率合成范圍及精度要求以及采用的TSMC 0.13/μm工藝,該設計將雙模前置分頻器設計為4/5雙模分頻器,P計數器為7位、S計數器為2位。因此該可編程分頻器可實現的最大分頻比為515。

1.2 4/5預分頻器結構

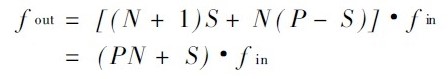

4/5預分頻器采用同步計數結構,其結構如圖2所示,由3個SCL結構的D觸發器和兩個與非門構成。Mode信號為分頻比控制信號,當Mode為“1”時,預分頻器分頻比為5,當Mode為“0”時,預分頻器分頻比為4。由于4/5預分頻器直接工作在VCO的輸出頻率下,是整個可編程分頻器工作頻率最高的部分,因此這部分的電路設計主要偏重于速度,其功耗是最高的。這部分電路采用SCL結構的模擬電路來實現,SCL結構的電路由開關管對尾電流的導通控制來實現邏輯電平的轉換,其工作速度高,滿足設計的要求。D觸發器由時鐘反連的2個D鎖存器構成,同時為了減少門延遲以提高工作速度以及降低功耗,將與非邏輯門集成于D觸發器內,帶有與非邏輯的D觸發器電路如圖3所示。

1.3 可編程計數器和吞脈沖計數器設計

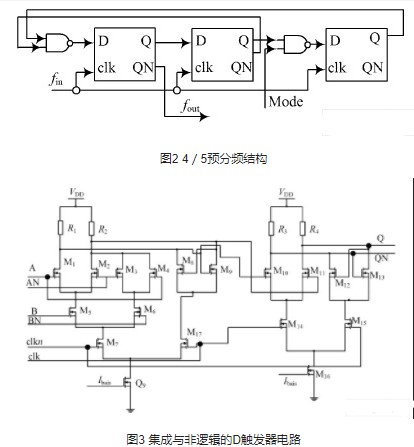

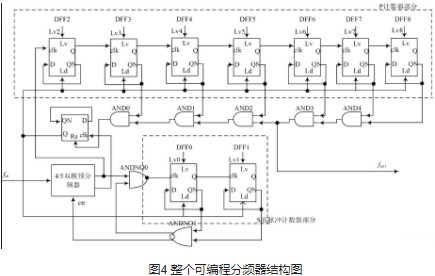

可編程計數器P和吞脈沖計數器S工作在分頻器頻率較低的頻段,采用簡單的異步計數器結構實現分頻功能。這部分的電路一般有兩種實現方式:模擬電路和數字電路,在該設計采用基于SCL的模擬電路來實現,相對于數字電路實現雖然消耗了一定的靜態功耗,但電路噪聲很低,版圖面積小,性能更加好。整個可編程分頻器結構如圖4所示。

其中P計數器部分由7個帶置數功能的D觸發器構成;S計數器部分由2個相同的D觸發器構成,另外包括2個與非門構成反饋邏輯控制預分頻器的分頻比;檢測和置數邏輯電路由5個與門和1個或門構成。D觸發器和邏輯門電路都是由基于SCL結構的模擬電路實現,全差分結構。在P計數器和S計數器中,每個D觸發器構成一個2分頻器,每個2分頻器再級聯。檢測和置數邏輯的功能是使得P計數器和S計數器計數完后自動置數,這部分的設計很關鍵,直接影響了整個分頻器的工作頻率,在本文中提出了一種新的檢測和置數邏輯,提高了分頻器的工作性能和工作頻率。以下通過對比傳統的檢測置數邏輯和改進后的檢測與置數邏輯來說明改進后的優勢。

1.3.1 傳統的檢測與置數邏輯設計

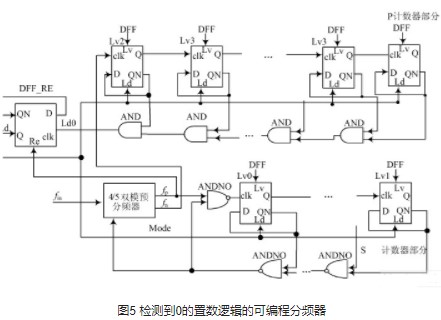

在傳統的基于雙模分頻器的可編程分頻器設計中,是對P計數器減計數到0時檢測,并通過一定的時序邏輯產生一個置數使能信號使得P計數器和S計數器進行置數。其檢測與置數邏輯電路如圖5所示,當P計數器減計數到0時,P計數器中每個D觸發器Qn端輸出都為1,這時級聯的與門邏輯輸出從0跳變到1,形成一個上升沿(為一個檢測信號)。這個上升沿作為帶有復位功能的D觸發器(DFF-RE)時鐘輸入,DFF-RE的復位端由4/5預分頻器輸出控制,即在嚴格的時序控制下,當檢測到P計數器減計數到0時產生一個上升沿信號,此時DFF-RE打開,這個上升沿信號使得DFF-RE輸出從0變為1,一段時間后DFF-RE關閉,故形成了一個置數脈沖,使得計數器重新置數。

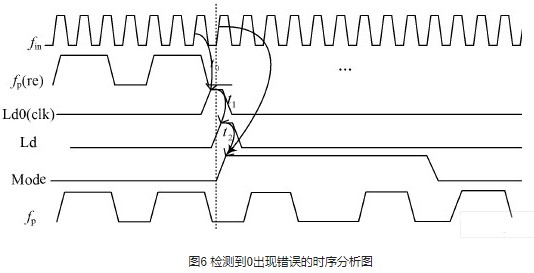

在這種結構中,檢測和置數的整個過程必須在輸入信號的一個周期內完成,從而限制了分頻器的工作頻率。下面通過對傳統檢測置數邏輯的時序分析來說明在輸入頻率較高時出現掉脈沖的現象,其時序圖如圖6所示,其中fin為分頻器的輸入信號,fp為4/5分頻器的輸出信號,同時作為DFF-RE的復位信號,Ld0為P計數器計數到0時的檢測組合邏輯電路輸出的信號,Ld為置數使能信號,即DFF-RE的輸出信號,Mode為控制4/5分頻器分頻數的信號。由圖中可知,在P計數器減計數到0時,檢測邏輯輸出一個脈沖(Ld0),從P計數到0到檢測脈沖信號產生有一個門延遲的t0,檢測脈沖到置數脈沖(Ld)的產生延遲時間為t1,Mode信號的產生延遲為t2。故從檢測到Mode信號上升沿的總延遲時間為t0+t1+t2,若這個總延遲時間大于了一個輸入信號的周期,如圖6所示,Mode信號控制的4/5預分頻器本該2次5分頻變為1次5分頻和1次4分頻,從而出現了掉脈沖的現象,最終導致整個分頻比錯誤。

1.3.2 改進的檢測與置數邏輯設計

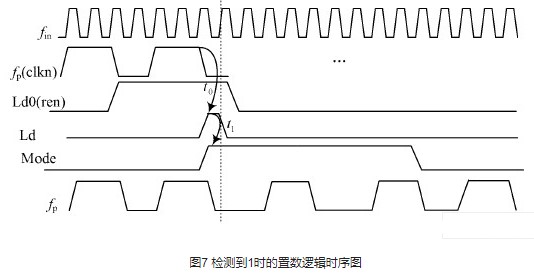

根據系統設計要求,分頻器工作的最高頻率需達到4.0 GHz,基于傳統的檢測置數邏輯的分頻器很難穩定的工作在此頻率下。因此,在該設計采用在P計數器減計數到1檢測,通過一定的時序控制下,當P計數器計數到0時置數,這樣檢測和置數的過程在2個輸入脈沖周期內完成,相對于計數到0檢測的分頻器,工作頻率可以提高2倍。以下具體分析改進后的檢測置數邏輯時序。在改進后的檢測置數邏輯中,如圖4所示,當P計數器減計數到0000001時,P計數器中DFF3~DFF7的QN端輸出都為1,因此AND0輸出由0變為1,AND0輸出反相信號作為DFF-RE復位端信號,而4/5分頻器輸出的反相信號作為DFF-RE的時鐘信號。其檢測和置數時序邏輯圖如圖7所示,當檢測到P計數到1后,DFF-RE便打開,置數脈沖的產生延遲為t0,Mode信號的產生延遲為t1,故由檢測到Mode上升沿信號的總延遲為t1+t2,相比圖6,少了一個門延遲,使得4/5預分頻器正確的進行了2次5分頻,避免了掉脈沖的現象。從對改進的檢測置數邏輯時序分析可知,改進后的設計使得可編程分頻器能夠工作在更高的頻率下。

2 電路版圖設計及仿真結果

2.1 可編程分頻器版圖設計

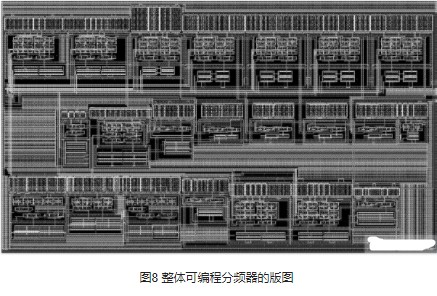

整體可編程分頻器的版圖如圖8所示,由于分頻器中各單元電路都是差分結構,需要考慮到器件的匹配設計,同時對單元電路需要合理布局,以減小關鍵路徑的連線延遲和節省版圖面積。

2.2 可編程分頻器仿真結果

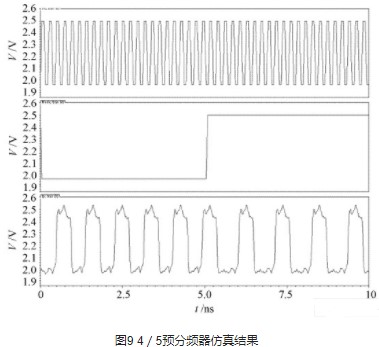

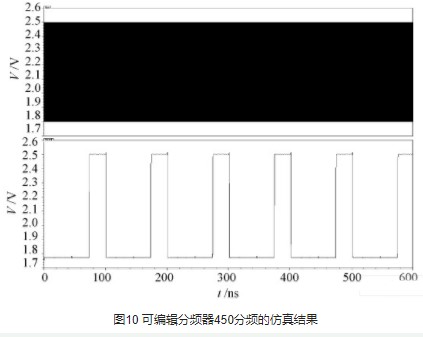

本文的仿真結果是在提取版圖寄生參數后,進行后仿真得到的結果。最高工作頻率可達4.5 GHz,在工作電壓2.5 V下消耗功率約為19 mW。圖9是工作頻率在4.5 GHz下,4/5分頻器的后仿真波形。圖10是可編程分頻器在4.5 GHz下,分頻比為450,P計數器預置數112,S計數器預置數2時的工作波形。從圖中可看出整個可編程分頻器能夠在4.5 GHz下實現正確的分頻。

3 結語

對于射頻頻段的頻率綜合器,分頻器成為了制約環路速度的一個瓶頸。本文通過對吞脈沖結構的可編程分頻器的檢測和置數邏輯電路的改進,使得分頻器的工作速度可以達到4.5 GHz,滿足了多標準移動數字電視接收機調諧芯片的系統設計指標,同時由于該分頻器具有連續的寬分頻比,使其也可應用于其他射頻無線收發芯片中。同時,采用SCL結構的模擬電路實現整個可編程分頻器使得芯片面積較小,約為106 μm×187μm。

-

合成器

+關注

關注

0文章

273瀏覽量

25386 -

分頻器

+關注

關注

43文章

447瀏覽量

49987 -

計數器

+關注

關注

32文章

2256瀏覽量

94702

發布評論請先 登錄

相關推薦

CD4541可編程分頻器參數和電路 電子資料

怎么把小數分頻控制字與整數分頻控制字結合起來去控制可編程分頻器?

5G8630輸出頻率可編程分頻器的原理與應用

HT49 MCU的可編程分頻器(PFD)使用指南

2.4GHz頻率合成器可編程分頻器設計與實現

Hittite推出低噪聲可編程分頻器HMC794LP3E

淺談有源電子分頻器 有源電子分頻器電路圖

采用SCL結構的模擬電路設計寬分頻比CMOS可編程分頻器設計

采用SCL結構的模擬電路設計寬分頻比CMOS可編程分頻器設計

評論