由于成本低和集成度高等特點, CMOS技術正越來越多地應用于無線射頻收發芯片的設計。低噪聲放大器作為射頻信號傳輸鏈路的第一級,整個系統的信噪比( SNR)很大程度上取決于低噪聲放大器(LNA)的噪聲系數(NF)和增益。因此,高性能的LNA成為射頻前端電路設計的關鍵模塊。其主要目的是提供較高的線性度以抑制干擾和防止靈敏度下降;提供足夠高的增益使其可以抑制后續級模塊的噪聲以及良好的輸入輸出阻抗匹配;同時按照無線通信設備發展趨勢所要求的, LNA必須盡可能低的功耗。

Inductive2degenerate cascade 結構式射頻LNA設計中使用最廣泛的結構之一,因為這種結構能夠增加LNA的增益,降低噪聲系數,同時增加輸入與輸出級之間的隔離度,提高穩定性。但是這種結構也有一些缺陷,首先它需要提供一個大感值的柵極電感,大電感不利于集成而且寄生阻抗比較大,相應產生熱噪聲也會比較大;而且共柵級的源端受到襯底寄生影響較大,導致信號損失,噪聲系數惡化。為了實現低功耗的同時實現高增益,一種CS2CS cascaded電流復用結構得到了應用,第二級共享了第一級的偏置電流,第一級的輸出通過一個耦合電容連接到第二級晶體管的柵極上,電路結構反向隔離比較差,導致電路穩定性弱。通過引入一個級間諧振電感可以有效地改善這個問題,在低功耗的同時實現了高增益,改善了穩定性。

本文采用LC并聯網絡來取代柵極大電感,降低噪聲,節省芯片面積。同時采用了電流復用技術的兩級共源結構,而且兩級間采用了級聯的諧振匹配網絡來提高增益,降低功耗。第二部分從理論上分析了所采用的新型結構以及級間諧振電感的作用,第三部分設計了低噪聲放大器電路并給出了仿真結果,最后一部分是結論。

1理論分析

1. 1新型輸入匹配

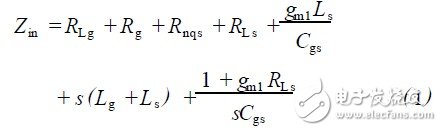

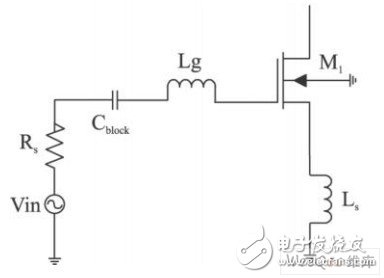

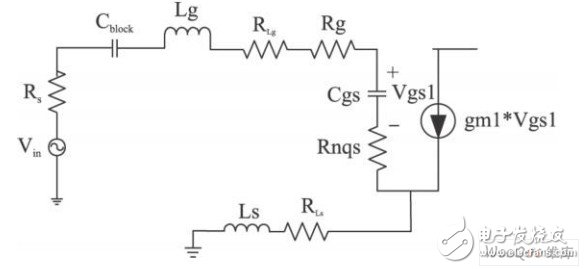

圖1為傳統的Inductive2degenerate cascade結構的輸入匹配電路,這種結構在不惡化噪聲性能的情況下很容易實現匹配,其等效小信號模型見圖2,輸入阻抗見式(1):

圖1傳統電路的輸入匹配結構

圖2傳統輸入匹配電路的小信號等效模型

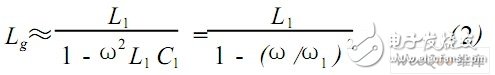

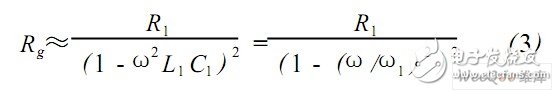

從上式可以看出,要降低Lg ,有幾種簡單的方法,其一是增加輸入管的寬度W,這樣Cgs就變大,從而Lg下降,但是這樣會增大漏極電流, 從而增加LNA的功耗,這顯然是不符合低功耗的要求;另一種方法是在輸入管的柵源端增加一個電容,但同樣降低了輸入端的品質因數, 降低了電路性能。還有一種是使用一個并聯的LC網絡來代替大電感,圖3是LC并聯網絡及其等效電路,為了方便推導,我們將電感的模型等效為一個理想電感L1 和理想電阻R1 的串聯。這個并聯的LC網絡的等效阻抗為:

其中:

圖3并聯LC網絡及其等效電路

公式中是并聯LC網絡的諧振頻率,ω為電路工作的頻率。通過式( 2) ( 3) 可知, 當0 <1 - (w/w1)平方< 1時, 這個小的LC 并聯電路可以產生一個大的電感和大的電阻。由于電阻R g是由電感的寄生電阻等效而來, 并不是一個實際的物理阻抗,因此其產生的熱噪聲比相同阻抗值的實際物理電阻產生的熱噪聲要小, 理論上既可以實現阻抗匹配,同時降低LNA的噪聲系數。

1. 2級間諧振電路

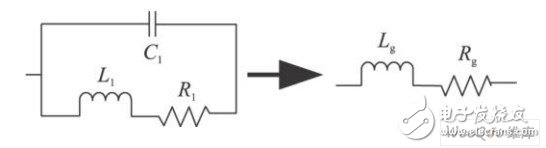

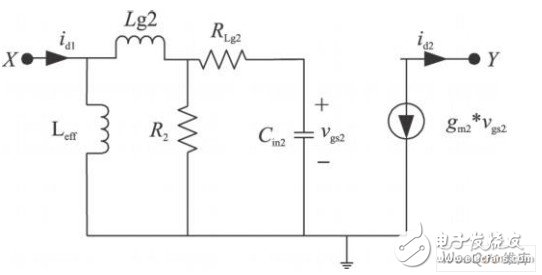

如圖4所示為一個包括級間耦合電容以及級間諧振電感的兩級共源放大器結構, 這種結構受到襯底寄生效應比較小, 在提高增益的同時改善了穩定性。C3 是級間耦合電容,級間諧振電感Lg2用來與第二級MOS管的輸入電容諧振, 這個感值可以采用中的方法來計算。

圖4帶級間匹配的兩級電流復用放大器

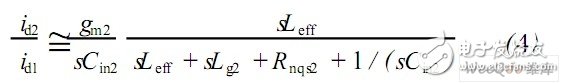

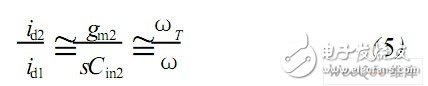

圖5是X 節點到Y 的節點之間的小信號等效電路圖,其中RL g2是電感的寄生電阻, Cin2是包含了M2 管的柵源電容以及Miller電容, Leff是并聯網絡Ld1 , Cd1的等效電感, R2 是一個大電阻,為M2 管提供直流偏置,其影響很小可以忽略不計。從該小信號電路圖可以得到第一級到第二級的電流增益的表達式,見式(4):

考慮到s·Leff對射頻電流來說是一個大的阻抗, 于是上式又可以簡化為:

上式表明通過級間耦合與級間諧振, 從第一級到第二級獲得了可觀的電流增益, 從而可以提高功率增益(例如在本設計中,ωT > 20 GHz) 。

圖5XY兩點間的等效電路圖

2電路設計及仿真結果

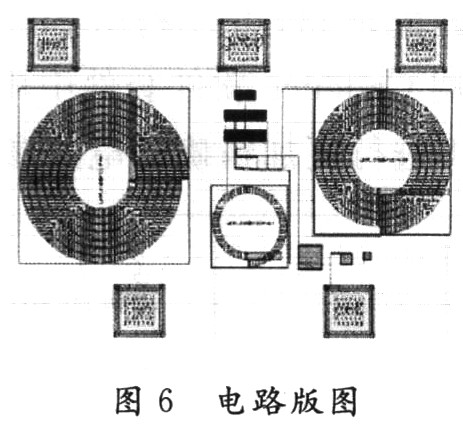

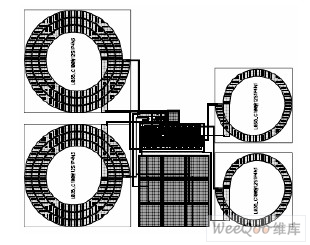

采用改進的匹配結構以及級間耦合,基于SMIC0118μm RF CMOS工藝設計了一個頻率為2. 4 GHz的低噪聲放大器。如圖6所示就是本文的電流復用兩級共源低噪聲放大器的拓撲結構。Ld1 ,Cd1和Ld2 ,Cd2分別是兩極共源管的負載阻抗, R1 , R2 是兩個大電阻分別給兩極共源管提供偏壓,取4 kΩ; C1 , C3 是大電容,起隔直的作用,C5 也是一個大電容,在M2 的源級作為一個旁路電容提供交流地; Lg1 , C2 ,Ld1 , Cd1這兩個并聯的網絡取代大電感實現阻抗匹配,減小芯片面積。

圖62. 4 GHz LNA拓撲結構

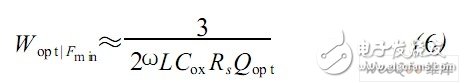

LNA的第一級對噪聲影響至關重要, 根據文獻中的功耗受限情況下放大管的最優柵寬計算公式來計算, 式中關于各個參數的定義見文獻[ 3 ]:

M2 管的柵寬一般為M1 的一半或者相同尺寸,這需要在抑制M2 的噪聲貢獻以及增益線性度等方面來折衷,M3 與M1 組成一個電流鏡為M1 管提供偏壓,一般取W1 = 10W3。為了限制整個電路的功耗, M3 的偏置電流為180 μA, 主體電路消耗1. 8 mA,整個電路共消耗2 mA,供電電壓為1. 8 V。

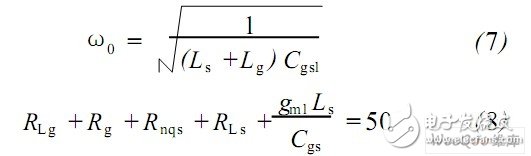

輸入匹配按照式(7) 、式(8) ,其中Lg 是并聯的LC網絡等效感值,級間諧振電感按照文獻[ 9 ]中的方法計算,值得注意的是, 因為密勒效應的影響, 輸入匹配會受到級間匹配元件的影響, 因此需要反復調整各元器件的值以達到良好的匹配。

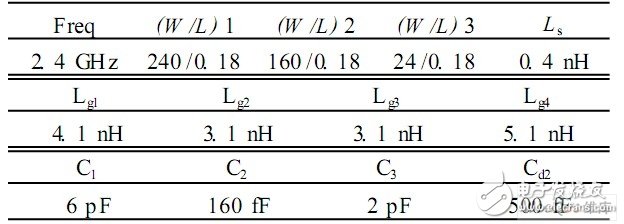

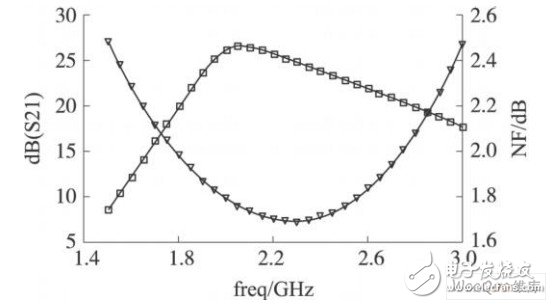

基于SM IC 0. 18μm RF CMOS工藝設計的頻率為2. 4 GHz的低噪聲放大器的各個性能參數由ADS( advanced design system)仿真給出,關鍵的電路元件參數見表1。圖7表明在達到高的功率增益的同時(23 dB@2. 4 G)實現了低的噪聲系數(1. 7 dB@2. 4 G) , 圖8 表明實現了很好的輸入輸出匹配( S11, S22 < - 30 dB) ,同時隔離度大于40 dB。圖9為該低噪放的版圖,面積為0. 88 mm ×1. 3 mm。

表1電路中管子參數以及各個電感的值

圖7低噪放的噪聲系數與功率增益。

圖8低噪放的輸入輸出反射系數

圖9低噪放的版圖

3結論

本文提出了一種新型的全集成的電流復用兩級共源低噪聲放大器,采用了新型輸入匹配以及感性級間匹配結構。為了降低芯片面積,兩個LC 并聯網絡代替了傳統的大電感。這種新型的電流復用結構更有利于輸入匹配,降低噪聲和功耗。采用SM IC0. 18 μm RF CMOS 工藝制作了一個頻率為2. 4 GHz,噪聲系數1. 7 dB, S11為- 30 dB, S22為- 36dB,功率增益為23 dB ,反向隔離度小于- 35 dB,在1. 8 V的供電電壓下僅消耗2 mA 。

-

CMOS

+關注

關注

58文章

5790瀏覽量

236602 -

放大器

+關注

關注

144文章

13720瀏覽量

214747 -

射頻

+關注

關注

105文章

5649瀏覽量

168599

發布評論請先 登錄

相關推薦

CHA3666-99F低噪聲放大器UMS

低噪聲放大器,低噪聲放大器型號參數

【轉帖】正確選擇低噪聲放大器

怎么設計低噪聲放大器?

CMOS多頻帶低噪聲放大器設計

利用Cadence設計COMS低噪聲放大器

采用LC并聯網絡實現CMOS電流復用兩級共源低噪聲放大器的設計

采用LC并聯網絡實現CMOS電流復用兩級共源低噪聲放大器的設計

評論