1 引 言

低噪聲放大器(LNA)位于射頻接收機的前端,其主要功能是對微弱信號進行低噪聲放大。在低噪聲放大器的設計過程中,要綜合考慮其放大能力、噪聲系數和匹配等因素,這需要大量的理論計算和smith圓圖分析,給設計工作帶來困難。

Advanced Design System(ADS)軟件是Agilent公司在HPEESOF系列EDA軟件基礎上發展完善的綜合設計軟件,內含很多進行小信號放大器設計的控件,能實現大量的計算和smith圓圖分析。以下將介紹如何利用ADS設計和仿真低噪聲放大器。

2 低噪聲放大器的設計理論

圖1是放大器電路原理框圖,其中r 表示源反射系數,r 表示負載反射系數。不同的r 和r。. 將影響放大器的穩定性、噪聲系數、增益、駐波等參數。設計放大器的過程就是根據放大器的s參數,以及噪聲系數、增益、駐波等的要求來確定TS和TL,然后根據TS和TL確定輸入、輸出匹配網絡。

圖1 晶體管放大器電路原理框圖

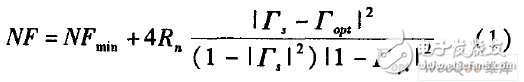

低噪聲放大器主要指標是噪聲系數Ts ,其與源反射系數的關系如下:

其中 NFmin和Rn分別是晶體管的最小噪聲系數和等噪聲電阻,Topt是最佳源反射系數。當Ts=Topt時,可以獲得最低噪聲系數 NFmin。

一般的低噪聲放大器的輸入匹配電路是按照噪聲最佳來設計的,為了獲得較高的功率增益和較好的輸出駐波比,輸出端采用輸出共扼匹配。

3 低噪聲放大器設計仿真和優化

3.1 設計目標

低噪聲放大器設計的關鍵是電路的第一級。對于低噪聲放大器的第二級及后續電路,可以使用MMIC微波單片放大器來完成,其設計相對來說比較簡單。

利用ATF一33143完成電路第一級的設計目標是:頻率:1260MHz一1280MHz;增益:≥10dB;噪聲系數:≤0.5dB;輸入駐波比:≤1.5;輸出駐波比:≤1.5。

3.2 仿真設計

(1)建立模型

上網下載ATF一33143的器件手冊,其器件手冊中提供了標準模型 J。

(2)確定工作點及偏置電路

根據芯片在各直流工作點條件下的性能選擇直流工作點。本文選取的直流工作點為:VDS:4V,IDS=40mA。在該直流工作點狀態下的芯片最小噪聲系數ⅣF i =0.34dB 。

(3)穩定性判斷

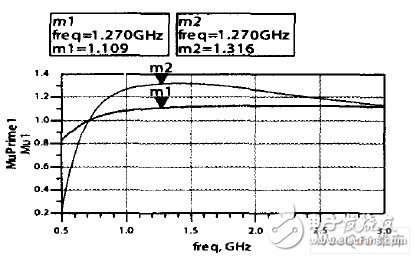

在ADS軟件中,根據Mu控件和Mu—Prime控件來判斷電路的穩定性。電路絕對穩定的充要條件是Mu>1和Mu—Prime>1。

一般的改善穩定性的措施為:

a.串聯阻抗負反饋

在場效應管的源極和地之間串接一個阻抗元件,從而構成負反饋電路。反饋元件常用一段微帶線來代替,它相當于電感性元件的負反饋。

b.穩定衰減器

P型阻性衰減器是一種簡易可行的改善放大器穩定性的措施,通常接在低噪聲放大器末級輸出口。

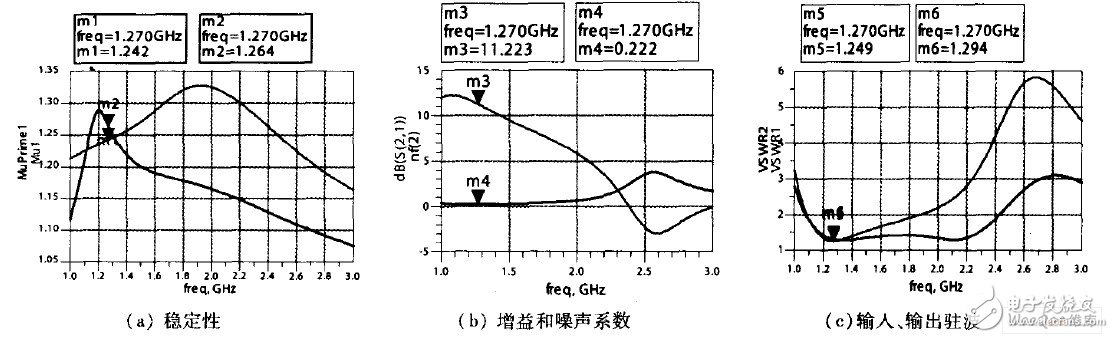

采取的改善穩定性措施為:在芯片源極添加電感構成負反饋;在漏極添加LRC串聯電路。圖2為添加反饋電路后的穩定性仿真結果。電路在0.7GHz~3GHz頻率處于絕對穩定狀態,而工作頻率為1260MHz一1280MHz,故滿足穩定性要求。

圖2 改善后的穩定性仿真結果

(4)設計輸入、輸出匹配電路

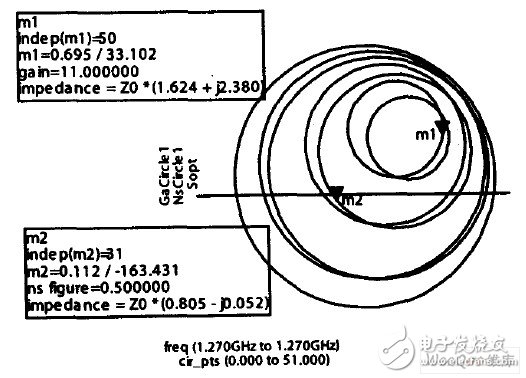

首先通過等噪聲系數圓和等增益圓來設置合理的源反射系數r ,然后根據源反射系數r 和放大器的s參數,按照最大增益匹配來確定負載反射系數Tl根據增益大于10dB和噪聲系數小于0.5dB的設計目標,如圖3所示,設置等噪聲系數圓控件和等增益圓控件。

圖3 等噪聲系數圓控件和等增益圓控件

圖4是等增益圓和等噪聲系數圓以Smith圓圖形式表示的仿真結果。源反射系數點的選取是在噪聲系數、增益這兩個指標間的折衷,選擇m1點為源反射系數點。m1點源反射系數對應的噪聲系數小于0. 3,增益為11dB。

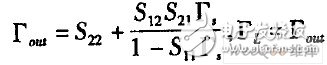

確定源反射系數后,根據公式:

計算出負載反射系數Tl,然后利用Smith原圖設計輸入、輸出匹配電路。

圖4 噪聲系數圓、等增益圓和輸入匹配點的確定

(5)優化

在上述中,分別設計了直流偏置電路和輸入、輸出匹配網絡,但是輸入、輸出匹配網絡的加入會改變場效應管的S參數,從而惡化某些指標。為了滿足所有的設計目標,有必要進行全局的電路優化。首先選取優化變量,設置變量的變化范圍,然后根據設計目標設置仿真目標,優化仿真變量,得到達到預設目標的最佳電路設計參數。優化后的仿真結果如圖5所示。

圖5 優化后的仿真結果

4 結束語

由仿真結果可知,所設計的低噪聲放大器在頻帶1260Mhz~1280MHz工作時,增益約為l1dB,輸入、輸出駐波均小于1.5,噪聲系數約為0.2dB,在1 GHz一3Ghz頻率范圍內絕對穩定,所有指標均滿足設計要求。該設計對于低噪聲放大器的設計研究有著一定的參考價值。

-

放大器

+關注

關注

144文章

13720瀏覽量

214747 -

晶體管

+關注

關注

77文章

9829瀏覽量

139396 -

ADS1220

+關注

關注

24文章

488瀏覽量

125303

發布評論請先 登錄

相關推薦

基于ADS的通信設備低噪聲放大器改進設計與仿真

射頻低噪聲放大器的ADS設計

基于ADS的通信設備低噪聲放大器改進設計與仿真

低噪聲放大器的設計與仿真

利用Cadence設計COMS低噪聲放大器

低噪聲放大器設計的理論基礎

微波低噪聲放大器的仿真設計

利用ADS軟件設計X頻段低噪聲放大器

低噪聲放大器的設計及利用ADS軟件進行仿真研究

低噪聲放大器的設計及利用ADS軟件進行仿真研究

評論