引言

TD-SCDMA是英文Time Division-Synchronous Code Division Multiple Access(時分同步碼分多址) 的簡稱,是一種第三代無線通信的技術標準,也是ITU批準的三個3G標準中的一個,相對于另兩個主要3G標準(CDMA2000)或(WCDMA)它的起步較晚。

使用CMOS收/發開關取代GaAs MOSFET收/發開關的好處之一是CMOS開關電路不需要負的控制電壓。而且,如果能用標準CMOS工藝來完成,開關電路就可以和收發器中其它RF模塊集成在一起,這將降低成本。

TD-SCDMA作為中國提出的第三代移動通信標準[2](簡稱3G),自1998年正式向ITU(國際電聯)提交以來,已經歷十多年的時間,完成了標準的專家組評估、ITU認可并發布、與3GPP(第三代伙伴項目)體系的融合、新技術特性的引入等一系列的國際標準化工作,從而使TD-SCDMA[3]標準成為第一個由中國提出的,以我國知識產權為主的、被國際上廣泛接受和認可的無線通信國際標準。這是我國電信史上重要的里程碑。(注:3G共有4個國際標準,另外3個是美國主導的CDMA2000、WiMAX和歐洲主導的WCDMA.)

TD-SCDMA系統規劃使用的頻段主要為1900MHz-1920MHz和2010MHz-2025MHz.本文采用TSMC 0.35m CMOS工藝來制作射頻收/發開關。通過優化設計,該開關電路在2GHz處取得了較好的仿真結果。

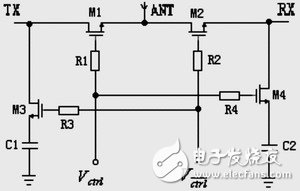

圖1對稱式收/發開關電路示意圖

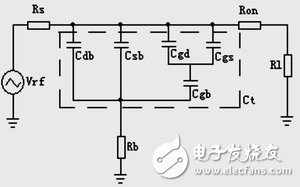

圖2MOSFET導通時的等效電路圖

圖3開關截止一側的小信號等效電路

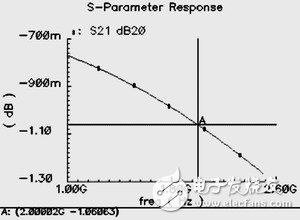

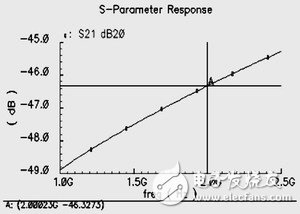

(a) 插入損耗

(b) 隔離度

優化設計

圖1是對稱式串并結構NMOS射頻開關的電路示意圖。串聯的晶體管M1和M2完成主要的開關功能。控制電壓Vctrl 和用于控制晶體管M1和M2的開與合。當Vctrl為高電平時,M1導通,M2截止,開關處于發射狀態;當為高電平時,M1截止,M2導通,開關處于接收狀態。該開關電路還包括旁通電容C1和C2,它們提供了開關電路中TX和RX端口的直流偏置。MOS管柵極上的偏置電阻R1、R2、R3和R4的作用是提高隔離度和線性度。本設計中,串聯MOS管柵寬取200?m,并聯MOS管的柵寬取100?m,旁通電容C1和C2取5pF,柵極偏置電阻R1、R2、 R3和R4均取10K.

射頻收/發開關的重要性能指標為:插入損耗(IL)、隔離度(Isolation)和線性度(通常用1dB壓縮點P1dB來表示)。其中插入損耗是設計的重點。

插入損耗

插入損耗表示當開關導通時射頻信號通過射頻開關的功耗。

管子的導通電阻是影響插入損耗的關鍵因素之一。因此,在本設計中只使用nMOSFET.由于硅襯底的導電特性,管子的漏極和源極對襯底的結電容及相關的寄生電容也是影響插入損耗的主要因素。

為了簡化,只分析包含單個MOS管的電路,圖2為其導通時的等效電路圖。圖2中,Vrf、Rs分別為等效信號源及源內阻,Ron為MOS管的導通電阻,Rb為其襯底電阻,Rl為負載電阻,Ct是其等效電容(虛線部分),其等效式為:

如果負載端和源端都與特征阻抗(Z0)匹配,則插入損耗可以用正向傳輸系數的幅度平方(|S21|2)的倒數來表示。

由該表達式可以看出,導通電阻Ron越大,插入損耗越大;寄生耦合電容Ct越大,插入損耗越小;襯底電阻對插入損耗的影響并不呈簡單的線性關系。實際上,有一個使插入損耗最大的襯底電阻Rb(max)

因此,用CMOS技術制作的RF開關電路要獲得較低的插入損耗,就要注意避免襯底電阻接近Rb(max)。然而,如果不對襯底電阻做特殊處理,這個值基本上屬于RF開關電路中晶體管的Rb值的典型范圍。對于標準CMOS工藝,取得較大的襯底電阻是不容易做到的,因此,降低襯底電阻是更好的方案。在版圖設計中,可通過增加襯底接觸來減小襯底電阻,從而達到進一步減小插入損耗的目的。

IL還可以用管子的柵寬(W)來表示,如(3)式。

一般來說,對于給定的工藝和版圖類型,Rbo、Cto和Rono可以被認為是固定的。所以柵寬的大小對插入損耗起著重要的影響:隨著柵寬的增大,導通電阻 Ron減小,從而使插入損耗減小;如果柵寬繼續增大,通過電容Ct耦合到襯底的信號也會增大,則插入損耗會隨著柵寬的增大而增大。

取并臂M3和M4的柵寬(WM3和WM4)接近WM1的一半。仿真結果表明,當WM1和WM2取200?m且WM3和WM4取100?m時,插入損耗最小。

另外,在MOS管的柵極增加電阻R的阻值也可降低插入損耗。仿真顯示,隨著柵極電阻的增大,插入損耗減小,但增加到10K?以后,插入損耗減小的幅度就很小了,所以考慮到版圖面積,取柵極電阻的阻值為10K?.

隔離度

截止狀態下,開關的小信號等效電路如圖3所示。

圖3中,Ron表示并聯MOS管的導通電阻,Coff表示串聯MOS管在截止狀態下的漏/源極間電容。

依據S與Z參數之間的變換公式,可得到發射端(TX)和天線端(ANT)間的隔離度表達式:

(4) 式表明,通過使并聯的MOS管的導通電阻遠小于信號源的特征阻抗,使得從串聯的、處于截止狀態的MOS管泄漏出來的信號,可以通過并聯的MOS管導通到地,而不是泄漏到發送端,從而大大提高了隔離度。從仿真的結果看,加上并聯MOS管后,

可以將隔離度提高10dB以上,而由此帶來的插入損耗的惡化卻可以忽略。此外,增加并聯MOS管的柵寬,也可以提高隔離度,但同時也會降低插入損耗和線性度,所以不宜取較大的柵寬。

性度線

線性度,即功率處理能力,通常用P1dB來表示。CMOS開關的線性度通常受到以下兩種情況的制約:1.應截止的MOS管發生了導通,對于M3管,這種情況最嚴重;2. MOS管柵極電介質性能不夠穩定。

為了提高開關的線性度,本設計采用了兩種措施:1)在MOS管的漏、源極兩端都加上直流偏置電壓;2)給4個MOS管都加上柵極電阻R.

從仿真的結果看,增加柵極電阻可以使線性度改善5dB左右。

仿真結果

利用模型復現實際系統中發生的本質過程,并通過對系統模型的實驗來研究存在的或設計中的系統,又稱模擬。這里所指的模型包括物理的和數學的,靜態的和動態的,連續的和離散的各種模型。所指的系統也很廣泛,包括電氣、機械、化工、水力、熱力等系統,也包括社會、經濟、生態、管理等系統。當所研究的系統造價昂貴、實驗的危險性大或需要很長的時間才能了解系統參數變化所引起的后果時,仿真是一種特別有效的研究手段。仿真的重要工具是計算機。仿真與數值計算、求解方法的區別在于它首先是一種實驗技術。

采用Cadence Spectre / Spectre RF仿真器進行仿真。在仿真過程中,分別對MOS管的柵寬和柵極電阻的阻值進行了優化選取,并確定了偏置電壓和偏置電容。最終確定串聯MOS管M1和M2 的柵寬取200?m,并聯MOS管M3和M4的柵寬取100?m,柵極電阻R 取10K?,偏置電容C1和C2取5pF.仿真結果如圖4所示。

結語

本文分析了影響對稱式射頻收/發開關性能的因素,包括柵寬、導通電阻、襯底電阻、柵極電阻等。采用TSMC 0.35m CMOS工藝進行設計和實現。經過優化設計和仿真,獲得了插入損耗為1.0 dB、隔離度46.3 dB和1 dB壓縮點12.8 dBm的電路。該射頻收/發開關可以與應用于TD-SCDMA的全集成CMOS收發器集成在一起,構成集成度更高、價格更低的收發器。

-

射頻

+關注

關注

104文章

5592瀏覽量

167857 -

天線

+關注

關注

68文章

3205瀏覽量

140874 -

MOSEFT

+關注

關注

0文章

35瀏覽量

4418

發布評論請先 登錄

相關推薦

基于0.35μm工藝的Delta-Sigma ADC實現

怎么采用標準CMOS工藝設計RF集成電路?

如何在O.5μm CMOS工藝條件下設計采用電流反饋實現遲滯功能的旁路電壓控制電路?

如何用0.6μm CMOS工藝實現功率放大器?

用于TD-SCDMA系統的集成CMOS對稱式收/發開關的設計

基于CMOS工藝的WLAN線性功率放大器設計

0.35μmCMOS光接收機前置放大器設計

采用CMOS工藝的射頻設計研究

采用RFSOI工藝來設計射頻開關

基于0.35μmCMOS工藝的射頻壓控振蕩器設計

采用TSMC 0.35m CMOS工藝實現射頻收/發開關的設計

采用TSMC 0.35m CMOS工藝實現射頻收/發開關的設計

評論