差分輸入ADC特性

目前許多高性能ADC設計均采用差分輸入。全差分ADC設計具有共模抑制性能出色、二階失真產物較少、直流調整算法簡單的優點。盡管可以單端驅動,但全差分驅動器通常可以優化整體性能。

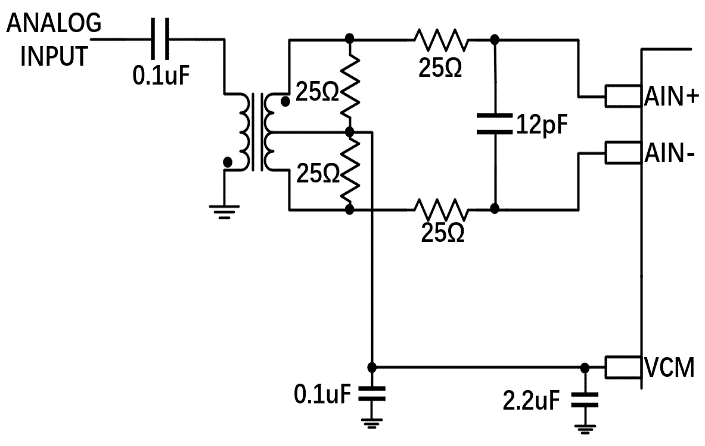

差分輸入ADC的一種最普通的驅動方法是使用變壓器。不過,因為許多應用中頻率響應必須延伸至直流,從而無法使用變壓器來驅動。這類情況就需要使用差分驅動器。本教程重點介紹如何驅動高達10 MSPS采樣速率的高分辨率16至18位ADC.輸入信號帶寬一般限于數MHz.MT-075教程闡述適用于驅動更高速ADC的差分放大器。

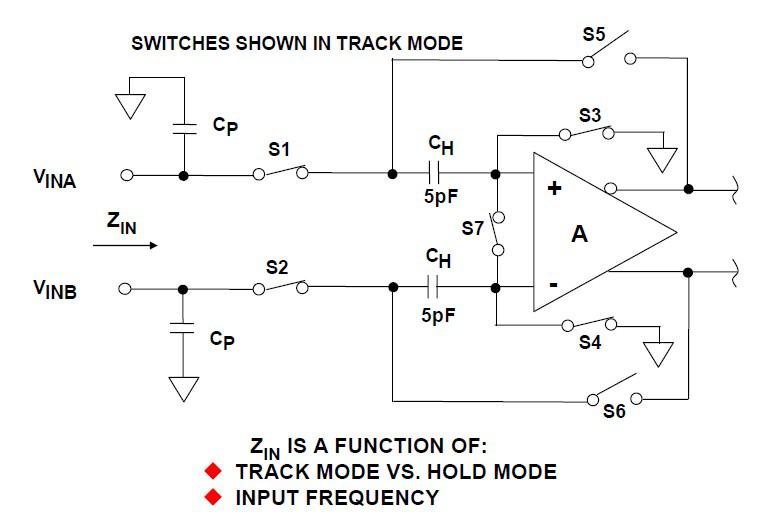

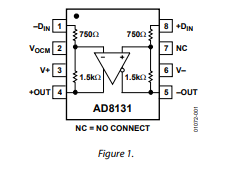

大多數高性能CMOS開關電容流水線式ADC的差分輸入均類似于圖1.

圖1:典型非緩沖開關電容CMOS采樣保持的簡易輸入電路。

大多數ADC都采用該差分結構。這既簡化匹配要求,又減少二階產物。此外,差分結構還有利于抑制共模噪聲。

注意,SHA開關直接連接至每個輸入。因為沒有隔離緩沖器,開關瞬態問題可能十分突出。驅動放大器的瞬態建立時間必須足夠快,否則放大器無法在半個采樣周期內穩定至所需精度(該建立時間必須包括外部串行電阻的效應)。

此結構的差分輸入阻抗呈動態,并在SHA切換采樣模式和保持模式時變化。此外,阻抗和模擬輸入頻率成函數關系。

在跟蹤模式(如圖所示),輸入信號對保持電容CH進行充放電,當電路切換至保持模式時,開關反轉位置,并將保持電容上的電壓傳送至輸出。

十分推薦這類輸入采用差分驅動以實現開關瞬態的共模抑制。雖然可單端驅動它們(一個輸入連接至適當的共模電壓),但因為無法再抑制偶數階失真產物,SFDR性能會下降。

圖2 (A)所示為典型非緩沖CMOS ADC的每個差分輸入以及采樣時鐘。這些輸入使用一個50Ω源電阻來驅動。注意,因為前述開關動作,在每個采樣時鐘的邊沿會出現一次瞬態。圖2(B)所示為在與(A)相同的條件下的ADC差分輸入信號。注意,瞬態電流毛刺屬于共模信號,故大多數會被消除。注意,為了達到最佳消除狀態,必須從一對平衡的源阻抗驅動兩個輸入(阻抗的實部和虛部都必須匹配)。

圖2:典型單端(A)和差分。

(B) CMOS開關電容ADC的輸入瞬態。

驅動精密16和18位差分輸入ADC

圖3所示為ADA4941-1驅動具有開關電容輸入的18位PulSAR系列ADC.這是一種單端雙極性信號、差分ADC輸入的常見應用。為了實現高分辨率,驅動放大器必須具有低失真、低噪聲、高直流精度以及具備單端至差分轉換功能的特點。ADA4941-1是一款低功耗(2.2 mA@ 3.3 V)、低噪聲(10.2 nV/√Hz @ 1 kHz)、低失真(110 dBc @ 100 kHz)的高達18位ADC的差分驅動器。小信號帶寬為31 MHz.該放大器還具有軌到軌輸出、高輸入阻抗和用戶可調節增益的特性。

ADA4941-1由兩個運算放大器組成。圖中下面一個配置成一個非定向同相緩沖器(帶外部反饋電阻)并驅動一個反相放大器。反相放大器的前饋和反饋電阻包括在IC中。盡管反相放大器會產生額外的相移和延時,但這不會在相關頻率處引入顯著的誤差(最高1MHz或2MHz)。

圖3:在+5V應用中ADA4941-1驅動AD7690 18位PulSAR? ADC

在此應用中,兩個電阻分壓器將ADA4941-1的輸出共模電壓設為+2.1 V,這樣輸出只能在離地電平的100m V內。這使放大器軌到軌級具有充足裕量并允許整個電路采用+5 V單電源工作。

AD7690和AD7691的輸入范圍為2.VREF p-p差分。所用基準電壓源為ADR444,這是一個4.096 V基準電壓源。截止頻率為1 MHz的低通濾波器的41.2 電阻和3.9 nF電容適合搭配輸入帶寬為9MHz的AD7690使用。對于所選配置,ADA4941-1輸出噪聲頻譜密度為10.2 nV/√Hz.在濾波器帶寬上積分后此值變成13 uV rms.這對應于運算放大器的107dB SNR,比ADC的100 dBSNR好7 dB.

圖4所示為驅動高性能iCMOSTM PulsarTM ADC(如AD7634)的另一個示例。許多工業應用的信號高達±10 V.iCMOS系列ADC被專門設計來滿足此類應用。大多數iCMOS Pulsar ADC具有差分輸入。這里,ADA4922-1驅動一個16位或18位iCMOS PulSAR ADC.它執行單端至差分轉換。

圖4:在±12V工業應用中ADA4922-1驅動AD7634 18位PulSAR? ADC.

ADA4922-1是一款16至18位ADC差分驅動器,差分輸入范圍高達40 V p-p.小信號帶寬為38MHz.ADA4922-1采用ADI公司專有的第二代XFCB工藝制造,使放大器可以在高電源電壓條件下實現出色的噪聲和失真性能。

針對該運算放大器使用1MHz低通濾波器進行噪聲計算可得15uV rms.ADC的信號范圍為40 V p-p,即14.14 V rms.這由于運算放大器自身會產生119 dB的SNR.

使用100 dB的AD7634 SNR,ADC均方根輸入噪聲可計算為141 V rms.因此,組合輸入ADC噪聲為142 V rms,運算放大器所貢獻的噪聲幾乎可以忽略不計。

發布評論請先 登錄

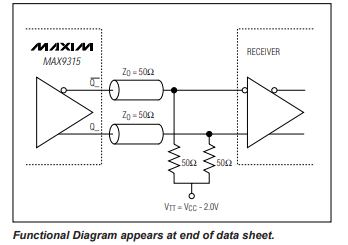

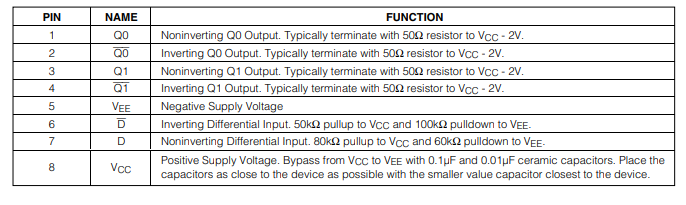

MAX9315 1:5差分LVPECL/LVECL/HSTL時鐘和數據驅動器技術手冊

MAX9320B 1:2差分PECL/ECL/LVPECL/LVECL時鐘和數據驅動器技術手冊

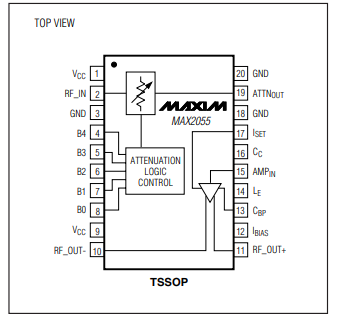

MAX2055數字控制、可變增益、差分ADC驅動器/放大器技術手冊

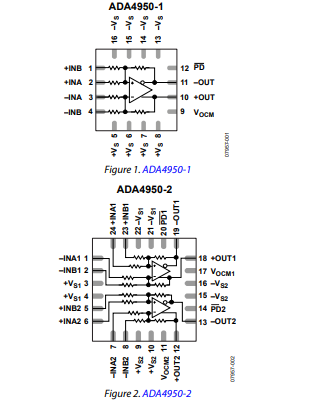

ADA4950-1低功耗、增益可選的差分ADC驅動器技術手冊

MSP430內部的SDADC的驅動一定需要差分驅動放大器嗎?

CDCVF111 1:9差分LVPECL時鐘驅動器數據表

評論