包含千兆采樣率ADC的系統設計會遇到許多復雜情況。面臨的主要挑戰包括時鐘驅動、模擬輸入級和高速數字接口。本文探討了如何才能克服這些挑戰,并給出了在千兆赫茲的速度下進行系統優化的方法。在討論中,時鐘設計、差分輸入驅動器的設計、數字接口和布局考慮都是十分復雜的問題。本文中的參考設計將采用ADC083000/B3000。

時鐘源是高速數據轉換系統中最重要的子電路之一。這是因為時鐘信號的定時精度會直接影響ADC的動態性能。為了將這種影響最小化,ADC的時鐘源必須 具有很低的定時抖動或相位噪聲。如果在選擇時鐘電路時沒有考慮該因素,則系統的動態性能在很大程度上將不由前端模擬輸入或ADC的質量決定。理想時鐘總能 在電平跳變之間保持精確的時間間隔。而實際中,時鐘邊沿之間的時間間隔是在不斷變化的。這一定時不確定性的結果,會使被采樣波形的信噪比在數據轉換過程中 降低。對于所有的抖動源,系統所能容忍的最大時鐘抖動[即由抖動所引起的噪聲不超過量化噪聲(1/2 LSB)]可由下式定義:

如果輸入電壓(VIN)經過優化等于ADC的滿量程(VINFSR),則對抖動的要求就只與ADC的分辨率(N位)和被采樣的輸入頻率(fin)相關。當輸入頻率達到奈奎斯特速率(對于1.5GSps的轉換速率為750MHz)時,總的抖動要求為:

這個值是各種原因引起的抖動的總和。ADC器件內部所引起的抖動被稱為孔徑抖動。以ADC083000為例,在數據表中給出的孔徑抖動為0.4ps, 該值將ADC時鐘的抖動規范限制在0.4ps。但是,當被用于數據轉換系統時,簡單地將振蕩器的性能數據匹配到所需的規范,可能還不足以得到所期望的結 果。這是因為基頻附近存在的其它頻率成分也起著重要的作用。因此,有必要用頻譜分析儀來檢查時鐘信號,并確定與基頻相關的能量沒有分布到過寬的范圍內。擴 展到更高頻率上的尖峰是可見的,并且也會直接影響抖動性能。

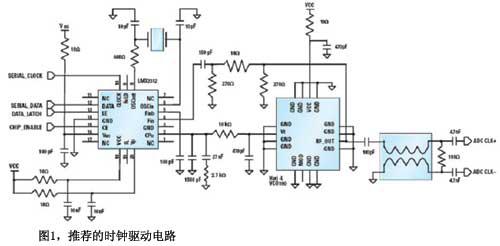

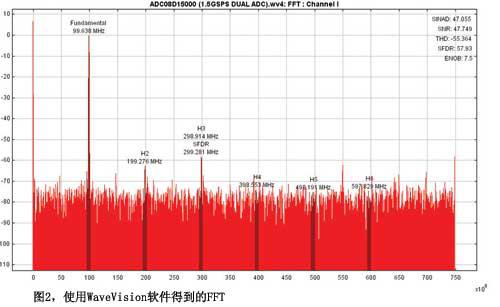

圖1顯示了為ADC083000所推薦的時鐘電路。它由一個與Vari-L壓控振蕩器(VCO)相連的鎖相環(PLL)器件(LMX2312)組成。 此PLL和VCO在奈奎斯特輸入頻率下仍能使ADC083000產品維持所需的信噪比(44dB)。圖2中的FFT顯示了ADC08D1500在1.5 GSps的時鐘速率下,采用圖1中的電路采樣100MHz輸入頻率時的動態性能。

通常使用一個差分放大器作 為單位增益的單端到差分端的轉換器。為什么ADC需要差分輸入呢?因為差分信號不僅有利于抑制共模噪聲,還能提高ADC的諧波性能。降低偶次諧波能帶來更 好的動態性能。使用運放來替代變壓器進行單端到差分端轉換的優勢在于放大器能允許直流信號通過而變壓器卻不能。并且使用放大器比使用變壓器更容易對增益進行控制。

當設計結束后檢查放大器的失調電壓時,要移除運放輸入端的激勵信號。現在使用WaveVision的ADC評估軟件,進行采樣并在時域中觀察這些樣 本。當運放的輸入電壓為零時,ADC的輸出應該處于半量程,即128(8位轉換器)。放大器的任何輸出失調誤差都會引起輸出碼偏離半量程。這樣就能測量運 放的輸出失調誤差。如果存在很大的失調電壓,則需要檢查運放輸入端的阻抗匹配,因為輸入端的阻抗失配會改變輸出失調電壓,由于輸出幅度受到限制,因此會減 小ADC的動態范圍。

捕獲數字輸出數據

以很高的頻率(1GSps甚至更高)對信號進行采樣意味著由轉換器產生的數字輸出數據必須快速地被存儲或至少被快速地轉移。ADC為它的兩個通道提供 了復用數據輸出。這一方法將數據率降低了一半,但增加了所需的位數。對于1GSps的采樣率,ADC的轉換數據輸出速率為500MHz。即使以這一被降低 的速度輸出,大多數分立或內部FPGA存儲器還是難以可靠地捕捉數據。因此最好使用雙數據率(DDR)的方法,在時鐘的上升沿和下降沿均傳輸數據。這樣對 于DDR信號,數據率不變,但時鐘頻率再次被減小一半,變成易處理的250MHz。這一頻率處于目前CMOS存儲電路可實現的范圍之內。在將數據存入存儲 器之前,在FPGA器件的輸入端需要一對中間數據鎖存器。第一個鎖存器由一個同相數據時鐘控制,而第二個鎖存器則由一個相差為180°的異相或反相數據時 鐘控制。

為了簡化這一計時要求,FPGA通常具有PLL(鎖相環)或DLL(延遲鎖相環)形式的數字時鐘管理器。這些器件允許在內部產生相位鎖定到一個輸入時 鐘的時鐘信號,并提供0°、90°、180°和270°的相位延遲。這一時鐘管理特性通過提供一個精確的相移180°的時鐘,使DDR的時序能有效地工 作。它還能確保到來的數據與下降沿同步,因此能可靠地被數據鎖存器捕獲。

被鎖存后,到來的數據可以被轉移到FIFO存儲器或Block RAM中。這樣系統微控制器就能以較慢的速度容易地從中找回這些數據,進行捕獲后的處理。

電路板布局

由于數字開關的瞬時變化主要由高頻成分構成,趨膚效應告訴我們邏輯變化產生的噪聲幾乎與地平面銅皮的總質量無關。總表面積比地平面的總體積更為重要。 典型的充滿噪聲的數字電路與敏感的模擬電路之間的耦合會導致很差的性能,并且似乎無法隔離和補救。解決這一問題的方法就是要很好地將模擬電路與數字電路分 開。由于所引起的公共回流路徑會在ADC的模擬輸入“地”中引起漲落,從而在轉換結果中引入額外的噪聲,因此不應將高功率的數字元件放置在任何線性元件或 模擬與混合信號元件的電源線和電源平面之上或其附近。

通常,我們假定模擬和數字引線應成90°交叉,以避免數字噪聲進入模擬路徑。但是,在高頻系統中應完全避免模擬和數字引線的交叉。輸入的時鐘線應與所 有其它引線(包括模擬和數字)隔離。應該避免通常可被接受的90°交叉,因為在高頻下即使少許耦合也會引起問題。在高頻下,筆直的信號路徑具有最好的性 能。模擬輸入應與充滿噪聲的信號引線隔離,以避免將寄生信號耦合到輸入中去。由于ADC083000要求低電平驅動,因此這一點尤其重要。任何連接在轉換 器輸入端和地面之間的外部元件(例如濾波電容),都應被連接到模擬地平面中一個非常干凈的點上。所有模擬電路(輸入放大器、濾波器等)都應與任何數字元件分開放置。

-

FPGA

+關注

關注

1629文章

21748瀏覽量

603863 -

存儲器

+關注

關注

38文章

7494瀏覽量

163912 -

adc

+關注

關注

98文章

6503瀏覽量

544864

發布評論請先 登錄

相關推薦

ADC083000芯片無法正常工作的原因?

ADC采樣保持過程的具體時間要如何確定?

國產示波器ADC芯片和國產信號源DAC芯片!

采用ADC083000/B3000的3GSps超高速ADC系統設計

ADC08B3000,pdf datasheet (8-Bi

ADC083000,pdf datasheet (8-Bit

國產ADC芯片——adc芯片的多種結構

ADC083000單通道、低功耗、高性能CMOS模數轉換器數據表

采用ADC083000/B3000ADC芯片對ADC系統進行優化

采用ADC083000/B3000ADC芯片對ADC系統進行優化

評論