和計算機一樣,數字信號處理的理論從60年代崛起以來,到80年代DSP產生,它飛速發展改變了信號處理的面貌。今天DSP已廣泛應用在語音、圖像、通訊、雷達、電子對抗、儀器儀表等各個領域。DSP起了十分關鍵的作用,成為數字電路設計的主要方法。

二十世紀80年代以來,一類先進的門陣列——FPGA的出現,產生了另一種數字電路設計方法,具有十分良好的應用前景。基于FPGA的數字電路設計方式在可靠性、體積、成本上的優勢是巨大的。

除了上述兩種方案,還有DSP+FPGA方案,以及選擇內部嵌入DSP模塊的FPGA實現系統的方案。

1 DSP和FPGA的結構特點

1.1 DSP的結構特點

DSP是一種具有特殊結構的微處理器。DSP芯片的內部采用程序和數據分開的哈佛結構,具有專門的硬件乘法器,廣泛采用流水線操作,提供特殊的DSP 指令,可以用來快速地實現各種數字信號處理算法。根據數字信號處理的要求,DSP芯片一般具有如下的一些主要特點:

(1)在一個指令周期內可完成一次乘法和一次加法;

(2)程序存儲器和數據存儲器是兩個相互獨立的存儲器,每個存儲器獨立編址,可以同時訪問指令和數據;

(3)片內具有快速RAM,通常可通過獨立的數據總線在兩塊中同時訪問;

(4)具有低開銷或無開銷循環及跳轉的硬件支持;

(5)快速的中斷處理和硬件I/O支持;

(6)具有在單周期內操作的多個硬件地址產生器;

(7)可以并行執行多個操作;

(8)支持流水線操作,使取指、譯碼和執行等操作可以重疊執行。

1.2 FPGA的結構特點

FPGA的結構是由基于半定制門陣列的設計思想而得到的。從本質上講,FPGA是一種比半定制還方便的ASIC(ApplicaTIon Specific Integrated Circuit 專用集成電路)設計技術。

FPGA的結構主要分為三部分:可編程邏輯塊、可編程I/O模塊、可編程內部連線。可編程邏輯塊和可編程互連資源的構造主要有兩種類型:即查找表類型和多路開關型。

查找表型FPGA的可編程邏輯單元是由功能為查找表的SRAM(Static Random Access Memory 靜態隨機存取存儲器)構成函數發生器,由它來控制執行FPGA應用函數的邏輯。SRAM的輸出為邏輯函數的值,由此輸出狀態控制傳輸門或多路開關信號的通斷,實現與其它功能塊的可編程連接。多路開關型可編程邏輯塊的基本構成是一個多路開關的配置。利用多路開關的特性,在多路開關的每個輸入接到固定電平或輸入信號時,可實現不同的邏輯功能。大量的多路開關和邏輯門連接起來,可以構成實現大量函數的邏輯塊。

FPGA由其配置機制的不同分為兩類:可再配置型和一次性編程型。近幾年來,FPGA因其具有集成度高、處理速度快以及執行效率高等優點,在數字系統的設計中得到了廣泛應用。

2 DSP與FPGA性能比較

DSP內部結構使它所具有的優勢為:所有指令的執行時間都是單周期,指令采用流水線,內部的數據、地址、指令及DMA(Direct Memory Access直接存儲器存取)總線分開,有較多的寄存器。

與通用微處理器相比,DSP芯片的通用功能相對較弱些。DSP是專門的微處理器,適用于條件進程,特別是較復雜的多算法任務。在運算上它受制于時鐘速率,而且每個時鐘周期所做的有用操作的數目也受限制。例如TMS320C6201只有兩個乘法器和一個200 MHz 的時鐘,這樣只能在每秒完成400M的乘法。

將模擬算法、具體指標要求映射到通用DSP中,比較典型的DSP通過匯編或高級語言如C語言進行編程,實時實現方案。如果DSP采用標準C程序,這種C代碼可以實現高層的分支邏輯和判斷。例如通信系統的協議堆棧,這是很難在FPGA上實現的。從效果來說,采用DSP器件的優勢在于:軟件更新速度快,極大地提高了系統的可靠性、通用性、可更換性和靈活性,但DSP的不足是受到串行指令流的限制。

FPGA有很多自由的門,通過將這些門連接起來形成乘法器、寄存器、地址發生器等等。這些只要在框圖級完成,許多塊可以從簡單的門到FIR(Finite Impulse Response 有限沖激響應)或FFT(Fast Fourier Transform. 快速傅里葉變換)在很高的級別完成。但它的性能受到它所有的門數及時鐘速度的限制。例如,一個具有20萬門的Virtex 器件可以實現200MHz時鐘的10個16位的乘法器。

FPGA包含有大量實現組合邏輯的資源,可以完成較大規模的組合邏輯電路設計;與此同時,它還包含有相當數量的觸發器,借助這些觸發器,FPGA又能完成復雜的時序邏輯功能。通過使用各種EDA (Electronic Design AutomaTIc 電子設計自動化)工具,設計人員可以很方便地將復雜的電路在FPGA中實現。象微處理器一樣,許多FPGA可以無限的重新編程,加載一個新的設計方案只需要幾百毫秒。甚至現場產品可以很簡單而且快速的實現。這樣,利用重配置可以減少硬件的開銷。

超過幾MHz的取樣率,一個DSP僅僅能完成對數據非常簡單的運算。而這樣簡單的運算用FPGA將很容易實現,并且能達到非常高的取樣速率。在比較低的取樣速率時,整體上很復雜的程序可以使用DSP,這對于FPGA來講是很困難的。

對于較低速的事件,DSP是有優勢的。可以將它們排隊,并保證它們都能執行,但是在它們處理前可能會有些時延。而FPGA不能處理多事件,因為每個事件都有專用的硬件,但是采用這種專用硬件實現的每個事件的方式可以使各個事件同時執行。

如果需要主工作環境進行切換,DSP可以通過在程序里分出一個新的子程序的方式來完成,而對于每種配置FPGA需要建立專門的資源。如果這些配置是比較小的,那么在FPGA中可以同時存在幾種配置;如果配置較大則意味著FPGA需要重新配置,而這種方法只在某些時候可以采用。

最后,FPGA是以框圖方式編程的,這樣很容易看數據流。DSP是按照指令的順序流來編程的。大多數的單處理系統都是以某種框圖方式開始設計的。實際上,系統設計者大多認為將框圖移植給FPGA比將其轉化為DSP的C代碼更容易。

3 如何進行DSP和FPGA方案選擇

3.1 方案選擇原則

在選擇數字系統核心處理部分的方案時,有很多因素需要考慮。例如如何充分利用已有資源(包括軟、硬件)、系統要求的工作時鐘速率以及算法或工作方式的特點等,這些對最佳方案的選擇有很大的影響。

具體地說,在最初的方案論證階段,可以根據如下問題的回答情況來進行方案選擇:

(1)該系統的取樣速率是多少?

如果高于幾MHz,FPGA是理所當然的選擇。

(2)系統是否已經使用C語言編制的程序?如果是,DSP可以直接地實現。它可能達不到方案的最佳實現,但很容易進一步開發。

(3)系統的數據率是多少?

如果高于20~30Mbyte/second,則用FPGA處理更佳。

(4)有多少個條件操作?

如果沒有,FPGA是很好的;如果很多,則軟件的實現即DSP的實現是更好的選擇。

(5)系統是否使用浮點?

如果是,則使用可編程的DSP更好。目前為止,一些FPGA開發商,如Xilinx 公司的核還不支持浮點,盡管自己可以設計。

(6)所需要的庫是否能夠獲得?

DSP和FPGA都提供諸如FIR或FFT等基本的構建模塊。然而,更復雜的或專用的構件可能得不到,這將決定選擇。

3.2 方案選擇示例

下面提供了幾個數字電路設計例子,有助于理解前面介紹的方案選擇原則。

(1)用于無線數據接收機的抽樣濾波器。典型的CIC(Control Integrated Circuit 控制集成電路)濾波器工作在50~100MHz的取樣率,5步CIC有10個寄存器和10個加法器。要求加速度在500~1000MHz。

在這一速率下任何的DSP處理器將很難實現。然而CIC只有非常簡單的結構,這樣以FPGA來實現將會很簡單。100MHz的取樣率可以達到,甚至某些型號的FPGA還可以有些剩余資源來實現進一步的處理。

(2)實現通信堆棧協議——ISDN(Integrated Services Digital Network 綜合服務數字網)。IEEE1394有很復雜、大量的C代碼,完全不適合用FPGA來實現;但是用DSP來實現卻很簡單。不僅如此,一個信號編碼基數可以得到保留,這樣可以使代碼堆棧在某一產品的DSP上來實現,或者在另一塊DSP上的分離的協議處理器來實現。這將給專門提供為代碼堆棧授權的供應廠家以機會。

(3)數字射頻接收機的基帶處理器。一些類型的接收機需要FFT來獲得信號,然后匹配濾波器一次獲得信號,這兩個模塊可以很簡單的用任何一種方案實現。然而如果要求工作模式轉換/信號獲得和信號接收的轉換;則采用DSP方案更適合。因為FPGA方案需要同時完成兩個模塊。

這里要注意,射頻用FPGA實現更好,因為這是一個混合、多任務的系統。如果應用更大的FPGA,這樣兩個模塊可以同時用一個FPGA來實現。

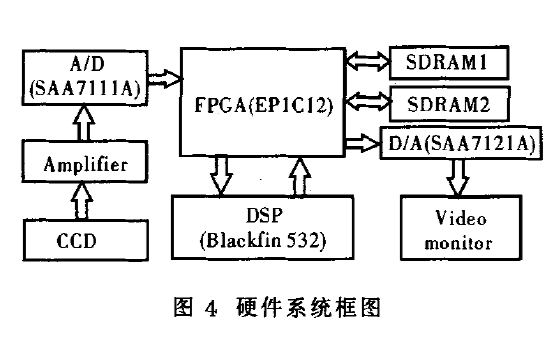

(4)圖象處理器。對于圖象的處理過程多是簡單的和重復的,這樣很適合用FPGA實現。然而,一個成像處理流程往往用于在所觀測的目標識別“斑點”或“感興趣的區域”。這些“斑點”可能大小不一樣,造成后端的判斷及處理過程趨于復雜。同時,所用的算法往往是自適應的,取決于斑點是什么樣的。所以用DSP構成圖象處理管道的后端處理部分是合適的。

總之,DSP和FPGA代表著兩種數字系統的信號處理的過程,各有所長和不足之處。對于許多高速采樣頻率的應用,特別是任務比較固定或重復的情況下,適合采用FPGA方案;同樣,對于較低的取樣速率和有很高復雜度的軟件問題的情況適合采用DSP方案。

4 新的設計思想

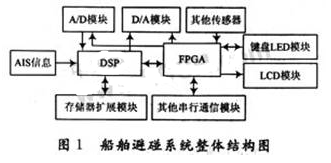

4.1 DSP+FPGA結構

DSP+FPGA結構最大的特點是結構靈活,有較強的通用性,適于模塊化設計,從而能夠提高算法效率;同時其開發周期較短,系統易于維護和擴展。

例如,一個由DSP+FPGA 結構實現的實時信號處理系統中,低層的信號預處理算法處理的數據量大,對處理速度的要求高,但運算結構相對比較簡單,適于用FPGA進行硬件實現,這樣能同時兼顧速度及靈活性。高層處理算法的特點是所處理的數據量較低層算法少,但算法的控制結構復雜,適于用運算速度高、尋址方式靈活、通信機制強大的DSP芯片來實現。

FPGA可以完成模塊級的任務,起到DSP的協處理器的作用。它的可編程性使它既具有專用集成電路的速度,又具有很高的靈活性。

DSP具有軟件的靈活性;而FPGA具有硬件的高速性,從器件上考察,能夠滿足處理復雜算法的要求。這樣DSP+FPGA的結構為設計中如何處理軟硬件的關系提供了一個較好的解決方案。同時,該系統具有靈活的處理結構,對不同結構的算法都有較強的適應能力,尤其適合實時信號處理任務。

4.2 嵌入DSP模塊的FPGA

應用將一些能實現基本數字信號處理功能的DSP模塊嵌入的FPGA芯片是數字電路設計的另一個大趨勢。

有些公司已經或計劃把基于ASIC的微處理器或DSP芯核與可編程邏輯陣列集成組合在一塊芯片上。FPGA提供的DSP性能已超過1280億MAC每秒,大大高于目前主流供應商所能提供的傳統DSP的性能。

其中,Xilinx作為世界可編程邏輯器件的領導廠商,擁有先進的FPGA技術以及先進的開發工具。2000年11月,推出Xilinx XtremeDSP行動,試圖進入這一市場。Virtex-II可以提供6千億MAC(乘法累加運算)每秒的性能。采用這種并行結構,256階FIR濾波器中的每個樣本可以在一個時鐘周期內處理完,因此極大地改善了DSP的性能和效率。

Xilinx XtremeDSP行動的目標是希望滿足寬帶革命的高性能挑戰。其它特性還包括根據如芯片面積(相應于使用的資源)和系統頻率來優化DSP設計。XtremeDSP行動還推出了一些開發工具以彌補傳統上在DSP和FPGA設計方法間存在的差距。

新的Virtex-II系列的增強結構使其在實現需要計算的算法時具有獨特的優勢。Xilinx提供的測試數據表明,Xilinx FPGA比業界最快的DSP運行要快100倍。因此,單個FPGA即可代替傳統上所謂的DSP處理器陣列。

目前世界上的許多手機基站產品采用了Xilinx公司Virtex-E FPGA。為了建立大量的連接,手機基站需要處理大量的數據,其中大部分是采用某種DSP實現的。

性能比較突出的還有QuickLogic公司推出的QuickDSP系列,它提供了嵌入式的DSP構件塊和可編程的邏輯靈活性。這個新的系列除了提供以前的可編程的邏輯和存儲模塊外,還包括專用的乘加模塊。這些合成的模塊可以實現DSP功能。支持DSP功能的軟件可以由公司獲得,除了QuickWorks開發軟件外,DSP 向導包讓使用者產生優化的功能,如定點或浮點算術邏輯,FIR和IIR(Infinite Impulse Response無限沖激響應)濾波器等,只要鼠標點擊幾下即可。

可以預測,在不久的將來,單一的DSP或FPGA實現的數字系統會被DSP+FPGA的結構或嵌入DSP模塊的FPGA設計結構所取代。

-

dsp

+關注

關注

553文章

7987瀏覽量

348763 -

FPGA

+關注

關注

1629文章

21729瀏覽量

603015 -

存儲器

+關注

關注

38文章

7484瀏覽量

163765

發布評論請先 登錄

相關推薦

[討論]FPGA培訓—基于FPGA的DSP系統設計與實現

FPGA培訓—基于FPGA的DSP系統設計與實現

[轉帖]FPGA培訓—基于FPGA的DSP系統設計與實現

運用FPGA解決DSP設計難題

ARM、DSP、FPGA的詳細比較

采用FPGA來實現SVPWM調制算法

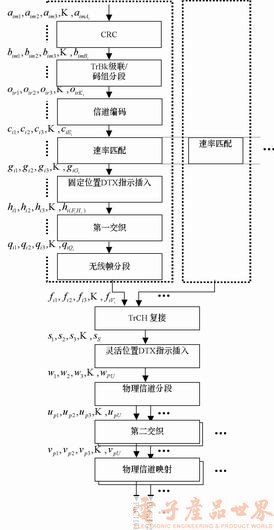

WCDMA系統基帶處理的DSP+FPGA實現方案

如何使用FPGA和DSP實現數字視頻消像旋系統的設計

采用DSP或FPGA實現的數字系統的比較與選擇

采用DSP或FPGA實現的數字系統的比較與選擇

評論