三十多年來,本本體硅(bulk silicon)MSOFET工藝一直是晶體管器件所采用的主要CMOS工藝。我們非常熱衷于從縮小晶體管來提高密度和性能。在相同的成本上具有更快的速度、更大的內存,是一件多么美妙的事情!越來越多的在工藝上的進步目前已能使完好的特征尺寸升級到90nm技術節點。然而,在深層納米尺寸滿足對漏電和性能的需要卻迅速地把傳統的晶體管逼入困境。

要使性能得到繼續的升級,人們正在采用新型材料和結構來改善傳統的CMOS工藝。在超過32nm及以上的技術上,面對著功率性能前所未有的挑戰,晶體管可能通過一系列的跳躍式創新得到發展嗎?盡管答案仍在探索之中,從金屬/高K柵堆疊、新型應變硅到多柵器件等等新型材料和器件結構競相發起這場革命。

當晶體管忙于開關時,微小的晶體管會消耗能量,因此依靠封裝更多的晶體管來提高密度并不湊效。不同工藝的能耗可通過動態功率來測得:

動態功率=CVdd2F

C=器件電容

Vdd=電源電壓

F=開關頻率

此外,作為一種并不完全的開關,即使當它們關閉時也會漏電,這一點對待機功耗起到作用。

待機功耗=I漏電xVdd

I漏電=漏電電流

當你把10億只晶體管集成到一個100mm2面積的裸片上時,功耗就會迅速增加,且情況正變得更糟。對功耗進行管理是當前從系統、設計到工藝的所有人員的壓倒一切的活動。降低功耗并不難,難在你要跟性能進行平衡。

短溝道靜電學

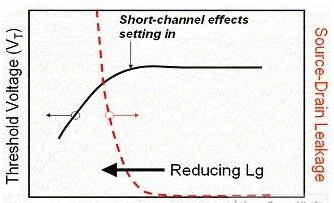

由于工藝和材料的限制,在我們急于壓縮門柵和溝道尺寸之時,源/漏結點和門柵電介質的升級卻不沒能跟上不能步伐。這導致短溝道靜電更加不足,當器件關閉時,門柵對源-漏的漏電影響更弱(也就是亞門限模式)。隨著在門柵與超出正常界線的源/漏之間的溝道電荷分配的增加(如圖1),會導致亞門限漏電增加,這點可從門限電壓出乎我們意料的降低中反映出來(圖2)。

圖1:器件電荷分配的影響有以下三種情況:(a)統一的溝道滲雜;(b)超淺結;(c)高的容器植入摻雜。

圖2:以門柵極長度(Lg)為函數的器件閥值電壓(VT)及源/漏漏電的曲線。對于更小的Lg,短溝道效應的開始造成VT減少。這一點同時伴隨著源?漏漏電的指數增長。

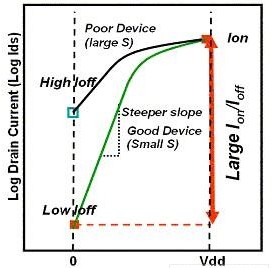

要緩減這一狀況,我們可使源和漏結點(xj)更淺且更陡(圖1b),或者通過增加結點周圍的溝道摻雜,來屏蔽靜電對源/漏的影響(降低耗盡寬度)(1c)。由于低阻抗超淺結點特別具有挑戰性,我們在進行伸縮時,大量的增加溝道摻雜來抑制漏電。增加摻雜會帶來兩種不良的副作用,會導致開關電流(Ion/Ioff)比急劇降低,該比值對于好的開關應被最大化。通過實現低亞門限擺幅(S),靜電的開關比可(圖3)以最大化。一個簡單的一維MOS電容器的S描述忽略了由[1]給出的源/漏的電荷分配的影響:

S = 1/(亞門限斜率) = 2.3 kT/q (1 + Cdm/Cox) 2.3 kTq (1 + 3Tox/Wdm)

T = 溫度

Cdm = 損耗電容

Cox =門柵電容

Tox =門柵電介質厚度.

Wdm = 溝道損耗寬度

取決于柵極與溝道之間的電容耦合(Cdm/Cox),S測量門柵在關閉與打開溝道之間擺動的良好程度。增加溝道摻雜,而不使門柵電介質厚度(Tox)相應地減少,會導致S的增加。對于短溝道MOSFET,S也可通過門柵與短溝道之間的電荷分配得到增加,這也會受到終接電壓的影響。顯然,在維持良好短溝道控制時,如果缺乏溝道摻雜(Cdm0),S值就最小(例如,最小化的源/漏門柵電荷分配)。如果不能完全自由地伸縮門柵電介質厚度及結點深度,由于短溝道控制在那時變得極度依賴于越來越多的溝道摻雜,從而使S最小化對于體MOSFET而言就是一個令人畏懼的事情。

圖3:具有匹配的電流,但具有不同的亞門限斜率的兩個器件之間的亞門限行為。

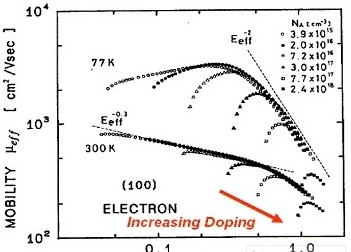

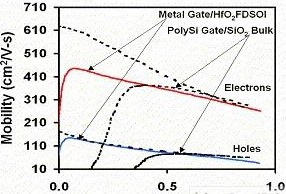

摻雜的另一個高代價是損傷傳輸速度。具有高溝道摻雜的器件被迫在更高門柵電場進行工作。這增加了具有門柵電介質界面溝道載流子的散射,導致載流遷移率(圖4)和折衷的驅動性能的大幅下降。

圖4:對于不同溝道摻雜水平(NA)和溫度[2], MOSFET的電子遷移率是有效電場的函數。

超薄體器件

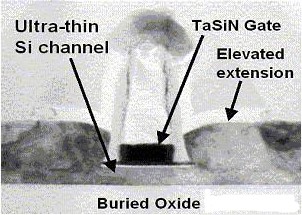

絕緣上硅(SOI)的異質結構為建造具有超薄硅體(硅厚度Tsi<10nm)(圖5)的器件創造了機會。通過由硅電介質界面建立的天然靜電屏障,超薄SOI提供一種控制短溝道效應的可選手段。由于受到超薄硅溝道的限制,源/漏結點深度現在就自然的變淺了。

圖5所示為一個具有金屬門柵和高K門柵電介質的40nm-Lg全耗盡超薄(UT)SOI器件的透射電子顯微鏡(TEM)圖像。

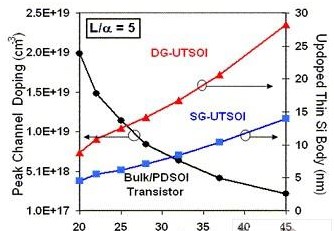

與體晶體管不同,超薄SOI通過它們的體結構來改進短溝道靜電效應,這一結構減少了它們對溝道摻雜的依賴(圖6)。要采用溝道摻雜工藝來控制最小體晶體管中的漏電,防止其增長到不可控制的水平,這可通過采用薄Si來計算。由于損耗電容Cdm保持為最小值,通過減少S,可使得開/關電流的比率最大化 。

圖6 所示為體MOSFET與超薄(UT)SOI所需的溝道摻雜之間的比較,以為給定Lg實現相同的短溝道控制(SG: 單一門柵,;DG: 雙門柵;PD-SOI: 部分損耗的 SOI)。

由于具有低溝道摻雜或不具溝道摻雜,這樣一個器件的門限電壓可主要通過門柵和電介質材料來確定。由于等效的溝道損耗寬度?Wdm?比Tsi更大,因此,溝道是完全損耗的。通過放棄使用溝道摻雜物來控制短溝道效應,完全損耗的SOI器件能在減少的有效電場進行操作,在此,載流子遷移率更高(圖7)。

圖7與等效的體晶體管相比,在具有更高遷移率的情況下,FD-SOI器件能以更低的有效電場工作。

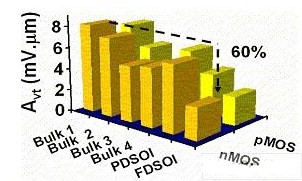

取消溝道摻雜也減少了因隨機摻雜物波動引起的可變性。盡管在薄Si體厚度中有變化,與有摻雜體器件相比,FD-SOI器件顯示非常大地改進了器件與器件之間的匹配性能 (圖8)。這對于存儲容量不斷擴大的SRAM和受隨機變化影響的模擬技術而言則是非常重要的。

圖8: FD-SOI與其它來自不同工藝的等效器件之間的失配比較(PDSOI:部分損耗的SOI)。

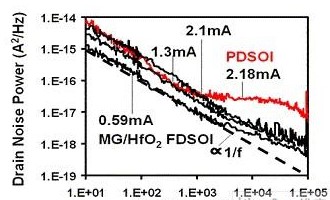

FD-SOI對浮體效應的免疫性和最小化源/漏(S/D)結電容(Cj)以及跟金屬門柵和高K電介質的結合,為低功耗和混合信號應用提供了多種優點,這些優點包括降低的門漏電、良好的線性及低噪音[3](圖9)。

圖9:與PDSOI器件相比,FD-SOI 器件顯示出更低的噪音。

應變硅與增強傳輸特性

通過改善短溝道靜電的影響,降低了漏電、可變性及待機功耗。在某種程度上,它甚至改進了傳輸特性。然而, 要充分地降低動態功耗,而不必對漏電和性能作出折衷,就需要進一步增強傳輸特性。

由于動態功耗的二次方程式取決于Vdd (CVdd2F), 調整電源電壓是降低動態功率的最有效的方法。然而,如果門限電壓并沒有降低, 那么,Vdd的減少會導致晶體管中載流子密度(Qi)的大量損耗。

Qi(max) Cox (Vdd-VT)

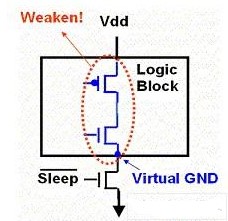

由于源/漏漏電呈指數地依賴于VT(圖2), 要調整VT就變得十分受到限制。此外,Cox的增加受到Tox的限制, 這一點最終受到門漏電和電介質可靠性的限制。 當晶體管被堆疊以減少漏電時,一個類似的問題又出現了(圖10)。在邏輯模塊中的堆疊器件要減少其最大門柵過驅動的虛擬節點(Vdd'-VT),因此,它們會隨著堆疊的增加變得更加弱。

圖10:晶體管堆疊對于實現“休眠”晶體管和電源門控技術已很常見。

要恢復相同的電流(I=Qi速率),載流子速率(或遷移率)必須得到增加以彌補Qi損耗。這正是遷移率隨應變硅的優越而得到增強之處。

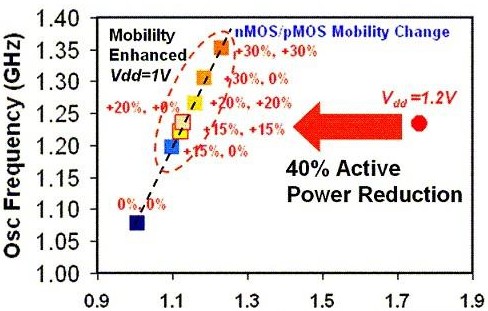

隨著英特爾宣布,把應力襯底材料和SiGe源/漏的結合進入90nm 技術節點,針對不同工藝的應變硅已應用到產品之中,被集成以增強他們的CMOS器件[4]。此外,人們還研究了從雙壓力襯底到襯低應變硅的許多其它的方法。推動晶體管性能的根本目標是相同的:實質性地增強遷移率,我們能在維持電路性能的同時,為降低動態功耗,而對驅動電流進行折衷(圖11)。

圖11: 振蕩器電路模擬表明:在保持頻率性能的同時提高遷移率,通過把Vdd從1.2V 降到1V,可以減低平均功耗。

這就意味著提高遷移率?傳統的高性能晶體管的發展推動力?也開始向低功耗管理這個前沿轉移,因此,要研究獲得更高遷移率的縮放路徑。

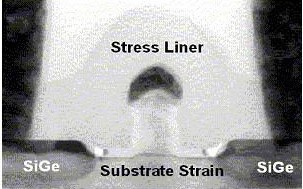

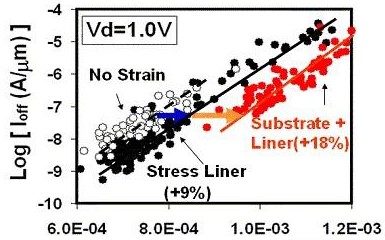

通過工藝技術把現有各種應力材料的優勢結合起來并加以增強,是進一步提高性能的自然方法(圖12, 13) [5]。最終,除了應變硅外,可能還需要具有更高遷移率的非硅材料,從而引領工藝及設計工程師努力開發新工藝并解決各種設計復雜性問題。

圖12:直接制作在在絕緣體上的應變硅(襯底應變)與嵌入式SiGe源?漏及襯底應力材料的結合,可以實現混合應變PMOSFET。

圖13:由應力襯低結合的絕緣體(襯底應變硅)上直接制作的應變硅增強了的NMOSFET性能。

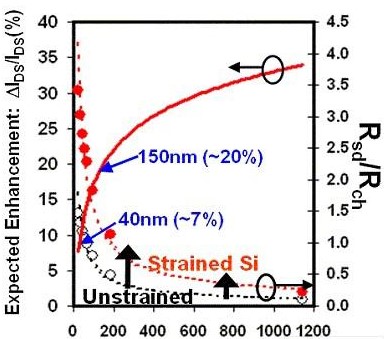

提高遷移率終于獲得了成功? Lg和溝道遷移率的提升加速了晶體管溝道阻抗(Rch)的降低,而寄生源/漏和接觸電阻(Rsd)要以更慢的速度降低。由于寄生參數導致越來越多的電壓降,增加Rsd/Rch比率會導致逐漸抵消所增強的晶體管性能,盡管遷移率增加(圖14)[6]。這就意味著,要把寄生電阻急劇降低的新型工藝與提高遷移率同時開發,以避免相互抵消。

圖14:因遷移率增強,驅動電流增強及作為Lg應變硅函數之一的Rsd/Rch加速了Rsd/Rch的增長,導致返回的驅動電流逐漸減小。

本文小結

我們發現日益改進的靜電學及晶體管傳輸有助于形成一種成熟的方法,這種方法能夠降低有源和待機功耗。要做到這一點,新型晶體管結構和材料拓展了性能功耗設計空間,使之超躍了傳統的本體硅晶體管。最終,通過構成一個由多層系統-電路-器件電源管理生態系統構成的底層,晶體管的創新將會繼續在定義下一代提高功效的策略時發揮關鍵作用。

-

CMOS

+關注

關注

58文章

5710瀏覽量

235421 -

晶體管

+關注

關注

77文章

9682瀏覽量

138084 -

MOSEFT

+關注

關注

0文章

35瀏覽量

4412

發布評論請先 登錄

相關推薦

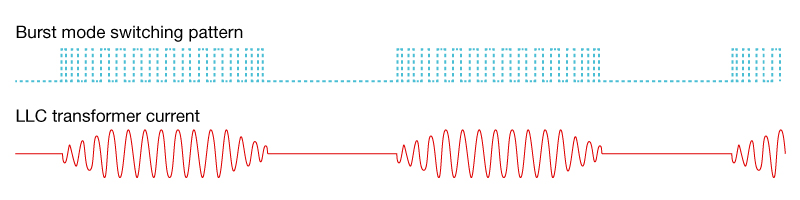

如何降低LED照明開關電源待機功耗

智能功率管理 - 降低家電待機功耗的有效方法

如何在 AC/DC 設計中降低待機時的可聞噪聲和功耗

提高能效并最大限度降低物料成本

有源濾波器APF的功效

吸收與緩沖電路的功效

反激式拓撲中最大限度降低空載待機功耗的參考設計

電源待機功耗怎樣降低

如何提高智能手機的待機功耗

CMOS器件功效的方法資料下載

如何降低功率CMOS器件的有源和待機功耗和提高應用功效

如何降低功率CMOS器件的有源和待機功耗和提高應用功效

評論