引言

隨著射頻無線通信事業的發展和移動通訊技術的進步,射頻微波器件的性能與速度成為人們關注的重點,市場對其的需求也日益增多。目前,CMOS工藝是數字集成電路設計的主要工藝選擇,對于模擬與射頻集成電路來說,選擇的途徑有多種,例如Si雙極工藝、GaAs工藝、CMOS工藝等,在設計中,性能、價格是主要的參考依據。除此以外,工藝的成熟度及集成度也是重要的考慮范疇。

1.概述

對于射頻集成電路而言,產品的設計周期與上市時間的縮短都是依賴仿真精確預測電路性能的設計環境的功能。為了使設計環境體現出高效率,精確的器件模型與互聯模型是必須要具備的,在設計工具中非常重要,對于射頻與模擬技術,器件模型決定了仿真的精度。

采用CMOS工藝,在射頻集成電路上的應用時間還補償,也使得在一些模型方面還不完善。對于射頻CMOS集成電路而言,對其影響最大的是寄生參數,在低頻環境下,由于對這些寄生參數的忽視,往往使電路的高頻性能受到影響。

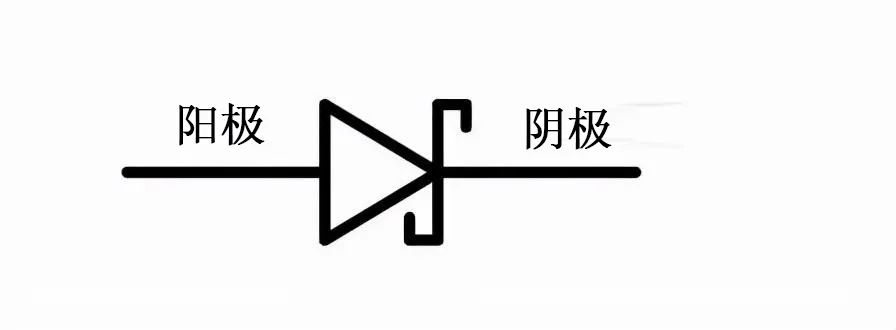

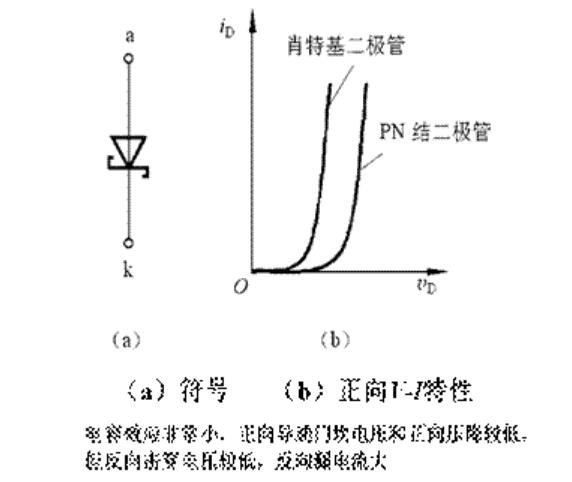

肖特基二極管具有自身獨特的優勢,例如快速開關速度和低正向壓降。由于這些優異的高頻性能,他們有被廣泛應用在開機檢測離子和微波網絡電路中。肖特基二極管通常制作的款式包括n型或p型半導體金屬材料,如砷GaAs和SiC.正向偏置的肖特基二極管的性能是由多數載流子器件,少數載流子主要是確定這些p型或n型二極管的屬性。為了改善高頻性能和集成電路的電源電壓減小到現代集成電路,集成的肖特基二極管是很重要的。但可以用于集成肖特基二極管的過程常常是沒有現成的,不能和CMOS電路單片集成。以往根據其設計,在標準CMOS工藝基礎上制造出肖特基二極管。在本文中,主要針對集成肖特基二極管的設計及實現進行描述,并且基于成本考慮,該標準CMOS工藝基礎上肖特基二極管生產工藝不需要任何修改。所測量的結果也符合要求,在SPICE仿真模型中得到驗證。

2.CMOS工藝技術

近幾十年,因為CMOS技術的發展,也使得在制造射頻集成電路時,采用CMOS技術得以實現。但是,因為CMOS制造工藝通常是以數字電路作為導向。面向數字電路設計的CMOS首先由芯片代工廠研發出來,注重功率耗散與時速。

在數字CMOS工藝快速發展成熟以后,在其基礎上,通過修改制程與添加掩膜層實現信號的混合及模擬射頻CMOS工藝。傳統CMOS工藝包含BJTs、MOSFETs以及各種電阻,如擴散電阻、多晶硅電阻及N阱電阻。但是,對于CMOS工藝而言,還應該涵蓋各種高頻無源器件,例如變容二極管、MIM電容、高Q值電桿及變壓器等。

同樣,作為肖特基二極管來說,也是CMOS工藝技術的重要環節。例如,需要額外高能離子注入形成深注入N阱降低程度耦合與噪聲系數。

需要注意的是,盡管射頻CMOS工藝是基于數字CMOS工藝而來,但其不僅僅是添加幾層掩膜來實現高頻無源器件,對于器件的性能而言,射頻工藝與數字工藝的優化目標是不同的,在進行改進的時候,也有可能與傳統的CMOS工藝發生沖突。

3.肖特基二極管的工作原理

之所以金屬半導體能夠形成對壘,主要原因是由于不同的功函數引起的。將金屬的功函數定義為技術費米能級與真空能級間的能量差,表示一個起始能量與費米能級相等的電子由金屬內部移向真空中所需要的最小能量。該能量需要克服金屬晶格與被拉電子與其它電子間的作用,還有一個作用是用來克服金屬表面存在的偶極矩。因此,功函數的大小在一定程度上可以表述電子在金屬中被束縛的強度。和金屬類似,半導體的功函數也被定義為費米能級與真空能級間的能量差,因為半導體的費米能級通常處于禁帶中,禁帶中一般沒有電子,因此該功函數的定義就可以看做是將電子帶導帶或者價帶移向真空能級需要的平均能量。對于半導體來說,還有一個很重要的參數,就是電子親和能,表示板代替導帶底的電子向外逸出所需要的最小能量。

對于肖特基勢壘的形成而言,假設現有一塊n型半導體和一塊金屬,兩者具有相同的真空電子能級,假設半導體的功函數比金屬的功函數小,同時,假設半導體表面無表面態,那么其能帶到表面都是平直的。此時,兩者就形成一個統一的電子系統,因為金屬的費米能級比半導體的費米能級低,因此半導體中的電子就會流向金屬,這樣金屬表面就會帶負點,半導體帶正電。所帶電荷在數值上是等同的,因此對于整個系統來說,還是保持電中性,從而提高了半導體的電勢,降低了金屬的電勢。如果電勢發生變化,所有的電子能級及表面電子能級都會隨之變化,使之趨于平衡狀態,半導體和金屬的費米能級在同一水平上時,電子的凈流動不會出現。原來的費米能級的差異被二者之間的電勢差進行補償,半導體的費米能級下降。

4.肖特基二極管的設計和布局

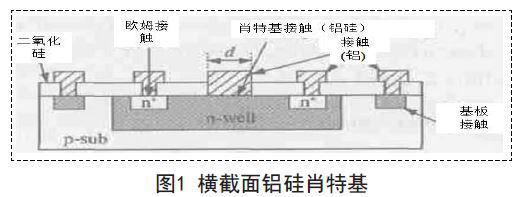

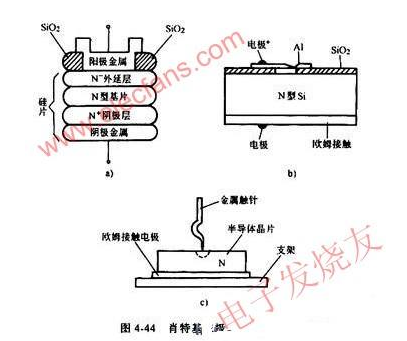

這種設計是基于標準CMOS工藝下,通過MPW在0.35μm工藝中得到實現的。當金屬層直接沉積到低摻雜n型或p型半導體區域,形成一個肖特基二極管。當這兩種材料彼此接觸,由于電勢差的存在就會產生一個勢壘高度,電子必須克服的電流才能流入。低摻雜的半導體上的金屬的陽極和半導體動脈插管,通過歐姆接觸在陰極上。在我們的設計中只使用n型肖特基二極管。跨節的Al-Si肖特基二極管如圖1所示。

在該設計中,沒有出現P+有源區在n阱接觸下接觸材料是鋁面積(等于到dxd)。因此,金屬層將直接連接到低摻雜n阱區。其結果是形成了的Al-Si的肖特基二極管接觸。對于鑄造工藝中需要確定的參數,例如密度、功函數等,只能通過對該區域的肖特基二極管進行控制得以實現,進行二極管的I-V曲線或者其它參數的修改。

根據標準CMOS工藝基礎上的肖特基二極管的布局及設計。首先,為了降低肖特基二極管的串聯電阻,肖特基和歐姆接觸電極之間的距離按照設計規則被設置為最小允許的距離。

其次,采用肖特基二極管布局的方法。交織式的布局為每一個串聯電阻提供了并聯連接的途徑,這是肖特基接觸的優勢所在。

5.所制作的二極管的測定結果

根據MPW,對肖特基二極管的不同部位通過三種交織方法進行標準C M O S工藝下的0.35μm制造,并對測得的結果進行了討論。

5.1 I-V的功能

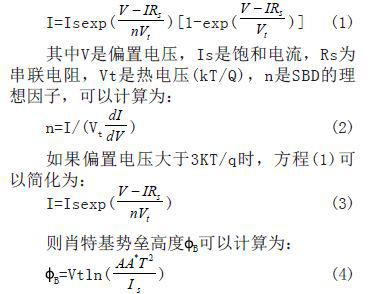

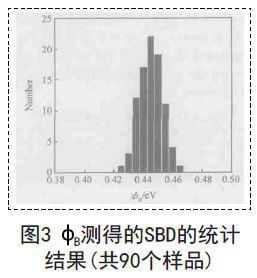

基于對串聯電阻的考慮,肖特基二極管的IV功能可表示為:

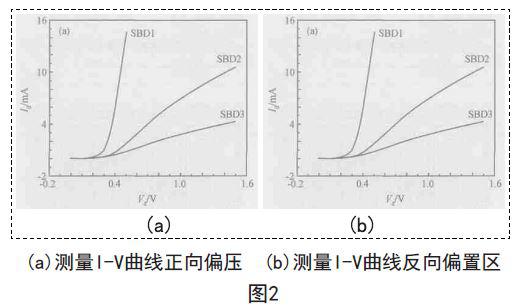

其中A*是有效的理查森常數。

所測量的I-V曲線如圖2所示。

(SBD1,SBD2,SBD3分別為16,1.6,0.64μm2)通過擬合公式(3)和所測得的結果,我們可以得到實現SBD的方法,如表1的參數所示。

從表1中可以觀察到,隨著相互交織的樹木的增多,串聯電阻的阻值明顯的降低。

為實現SBD的測量,勢壘高度B的測量的統計結果如圖3所示。在所測的90個樣本中,SBD1、SBD2、SBD3各30個樣本,從而求得實現SBD的勢壘高度為0.44eV左右。

擊穿電壓是4 . 5 V左右,在今后的工作中,在正常的SBD設計與生產中,擊穿電壓可以延長一些方法的使用,例如在自對準保護環境與SBD的制造過程中,5.2 C-V的功能

下面給出了小信號肖特基二極管的結電容Cj:

其中,Nd為摻雜濃度的n-阱,Φn是費米能級之間的電位差和導帶邊緣相等于(EC-Ef)/q.

圖4顯示了測得的反向偏壓為SBD的C-V曲線。

5.3 S參數測量和SBD高頻建模

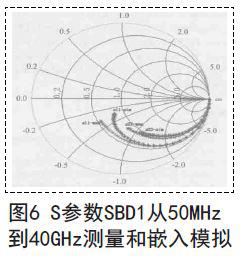

為了測量高頻率的S參數設計的設備,每個SBD被放置了有三個探頭焊盤。中間信號墊的大小是85μm×85μm和頂部/底部的的地面尺寸是85μm×135μm的。使用GSG探頭和網絡分析儀,我們可以得到S參數設計的SBD.但是,S參數的直接測量結果包括墊片、金屬線和覆蓋的寄生電容。對于設計的設備而言,盡管寄生參數是非常小的,但這些寄生參數是絕對不能被忽視的,在計算的時候應該將GSG探頭直接測量的S參數減去。在本文所研究的設計中,我們制作兩個虛擬的GSG信號墊作為測試裝置,假如兩個信號墊一個是偽GSG信號墊,一個是SBD信號墊,且兩個信號墊同等大小。除此以外的虛擬信號墊都是開放的,這也就是我們所說的開放式信號墊。S參數由啞墊進行測量。接著就可以得到信號墊和金屬線的寄生電阻和電容。將這些寄生參數減去,就能夠得到S參數的無寄生電阻和電容。將這種方法稱之為去嵌入技術。

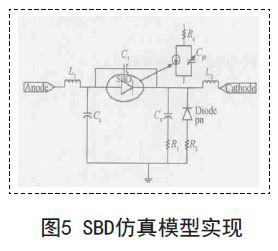

使用測得的S參數可以抽象為高頻模擬SPICE模型。圖5顯示SBD仿真離子模型的實現。L1和L2顯示出的輸入和輸出串聯電感。Ci和Co表示陽極輸入輸出電容和陰極節點。C1具有相互交織的肖特基二極管的兩個端口之間的寄生電容。R1和R2為連接S參數下NWLL到地面下電阻的n-阱的模型。pn二極管反映的寄生蟲n阱p-次二極管。在我們的設計中,可以用得到的pn二極管的參數通過標準CMOS工藝0.35μm的SPICE模型。

如圖6所示,為S參數SBD1測量和模擬。

表2給出了仿真離子模型的參數,頻率SBD1從50MHz到40GHz,該模型可以匹配到30GHz的測量結果。

6.結束語

隨著無線通訊具有的靈活性和高機動性的特點,其應用越來越廣泛,也順應了市場的需求。由于CMOS工藝在諸多的工藝中最為成熟、成本最低,卻功耗最小,因此得到廣泛的應用,隨著技術的不斷成熟,CMOS工藝基礎上的肖特基二極管設計及實現也成為現實。也是未來射頻集成電路發展的必然趨勢。通過MPW在標準CMOS工藝制造的肖特基勢壘二極管中的設計應用,可知鋁硅接觸的勢壘高度約0.44eV.

通過I-V,C-V和S參數測量可以實現SBD.通過本文所示,SBD設計的優勢較為明顯,最為顯著的是設計成本較低,能夠被廣泛的應用與商業標準的CMOS工藝中。在以后的工作中,更多的重點將集中在標準CMOS工藝設計的SBD的反向擊穿電壓和頻率范圍擴展。

-

CMOS

+關注

關注

58文章

5722瀏覽量

235614 -

射頻

+關注

關注

104文章

5591瀏覽量

167831 -

無線

+關注

關注

31文章

5455瀏覽量

173400

發布評論請先 登錄

相關推薦

什么是肖特基二極管?肖特基二極管的工作原理和作用

采用射頻CMOS工藝技術實現肖特基二極管的設計

采用射頻CMOS工藝技術實現肖特基二極管的設計

評論