引 言

智能電表(smart meter)作為智能電網的終端計量儀器,不僅需要能夠精確計量用戶的用電信息,而且還需各種通信功能,如RS485.紅外。電力線載波等,以實現自動化遠程管理。因此,智能電表在整個智能電網的建設中起著關鍵性作用。而對于智能電表的核心---電能計量專用芯片(Electrical Measurement Unit,EMU)也提出了更高的要求。目前計量芯片的模數轉換電路基本上都采用Sigma-Delta 型,而降采樣濾波器是Sigma-Delta ADC 的核心組成部分,因此,對降采樣濾波器的研究具有十分重要的意義。

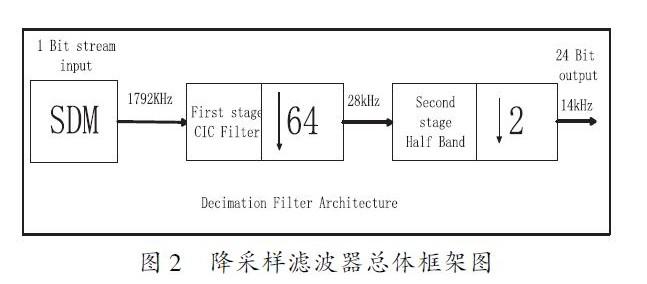

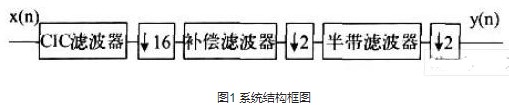

在Sigma-Delta ADC 中,功耗主要集中在降采樣濾波器 。而濾波器的功耗主要由乘法器決定,因此如何減少濾波器中乘法器的個數成為降采樣設計的研究重點.HOGENAUE 提出了級聯積分梳狀濾波器(Cascaded Integrator Com,CIC),由于CIC濾波器無須乘法運算,因此與傳統通過FIR 濾波器直接降采樣相比,極大地降低了面積與功耗。然而當降采樣率較大時,單級CIC 濾波器卻無法滿足要求,且功耗也相對較大。多級采樣交換理論及多相原理從而降低乘法運算次數,該方法的難點在于多相因子的不確定性,且不同的多相因子得到的濾波器結構不一樣,功耗也不一樣。串行算法實現CIC 從而降低功耗,但串行方法不適合計量芯片中并行的數據處理。文中提出了一種級聯抽取的方法,不僅結構簡單,也易于實現,完全滿足電能計量的需求。前級為CIC 濾波器,后級為HBF 濾波器,實現128 倍的抽取。由于HBF 只適用于2 倍抽取,因此前級CIC 降采樣率為64 倍。對HBF 的非零系數采用有符號CSD 編碼,進一步減少了電路功耗。

1 CIC 濾波器原理及設計

CIC 濾波器的基本結構如圖1 所示,由積分級和梳狀級級聯組成。

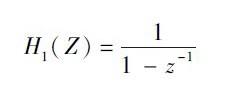

積分級采樣頻率為FS ,它的傳遞函數:

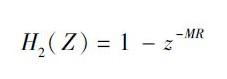

降采樣的倍數為R,相對于積分級,梳狀級的采樣頻率為FS / R,它的傳遞函數:

其中M 為延遲因子,控制梳狀級的頻率響應,在設計中,M 的取值一般為1 或2.

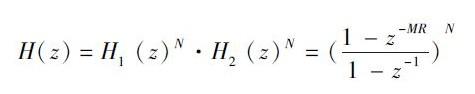

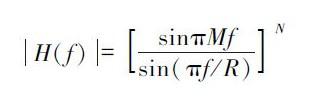

假設CIC 濾波器有N 階,那么總的傳遞函數為 :

幅值響應為:

CIC 濾波器的優點是結構非常有規律,由若干級積分級與梳狀級級聯組成,且內部無須乘法運算,因此,在變速率系統中得到了廣泛的應用。但隨著降采樣率的增加,內部寄存器的寬度以及功耗將會成倍的增加。電能計量芯片Sigma – Delta 的采樣頻率為1792kHz,后續數字信號處理的頻率為14kHz,因此,在本設計中,為了實現128 倍的降采樣,采用了分級抽取的方法。降采樣濾波器的總體框架如圖2 所示 。

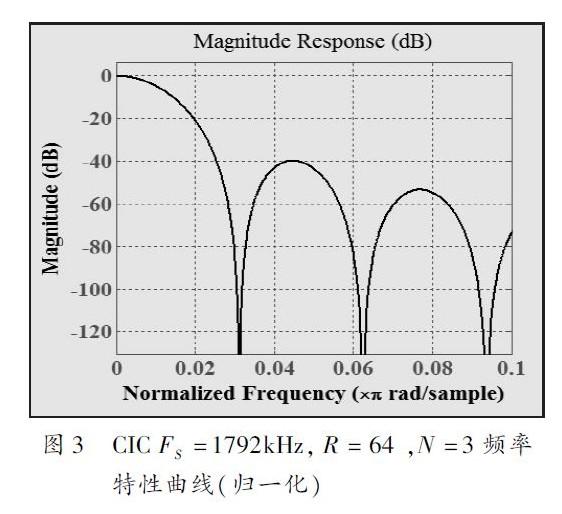

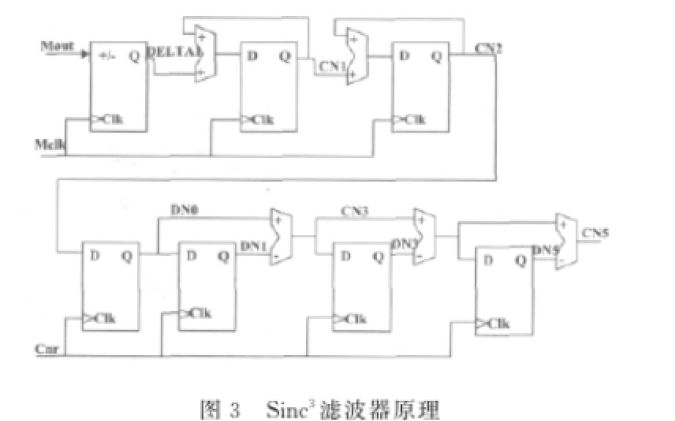

由于Σ-△為二階調制器,因此,三階CIC 濾波器即可達得很好的抽取效果。假定延遲因子為1,則內部寄存器的長度L = (N*(log2R ) + 1) 為19bit.采樣定點算法,內部寄存器量化為Sfix34. En15,輸出為Sfix24. En23.由CIC 濾波器的結構以及幅值響應公式可知,當R 足夠大時,信號通過CIC 濾波器時,幅值將會被放大[RM]N 倍,此設計中為643 ,因此,需將CIC輸出右移18 位,消除增益對信號的影響。圖3 為通過MATLAB 仿真得到FS =1792kHz, R = 64,N = 3 的歸一化(0 - 0. 1)幅頻特性曲線。

2 半帶濾波器的設計

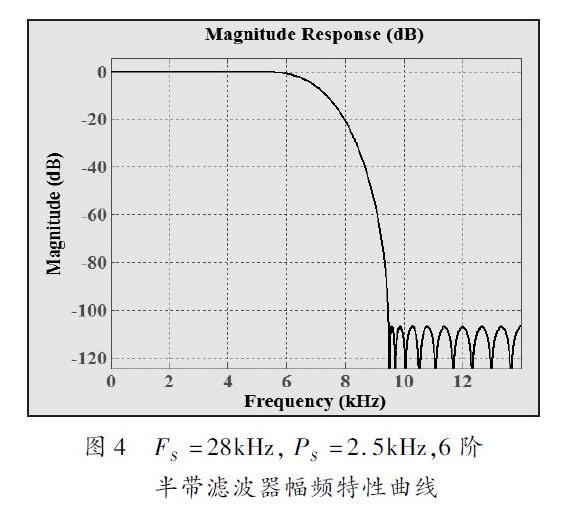

第二級的抽取濾波器用于衰減經過第一級梳狀濾波器后混疊在基帶內的信號分量和量化噪聲分量。由于電能計量對信號有嚴格的線性相位要求,所以必須采用FIR 型濾波器。半帶濾波器是一種特殊的線性相位濾波器,它的偶數系數都為零(中間位系數為0. 5),因此其實現濾波的運算量與同樣長度的其它線性相位濾波器相比減少一半,這將進一步減小芯片面積。降低電路的功耗。

綜合考慮芯片面積以及系統的頻率響應,HBF 設定為6 階。考慮到正弦信號的高次諧波以及CIC 補償濾波器的通帶頻率,HBF 的通帶頻率設定為2. 5kHz.

由于HBF 的系數值很少,量化精度不夠將影響系統的傳輸特性,仿真到的系數采用Sfix48. En47 Bit,內部乘法器采用Sfix56. En55 Bit 可滿足系統要求,而考慮到補碼定點數加法有可能產生溢出,所以加法器量化為Sfix56. En54 Bit.圖4 為通過MATLAB 仿真得到的HBF 幅頻特性曲線。

HBF 的運算包括乘法以及加法,而乘法運算的功耗最大。傳統的乘法運算采用移位相加的原理,相加次數等于乘數中1 的個數,因此減少乘數中1 的個數即可降低乘法電路的功耗.CSD 編碼正好滿足這一要求,經過CSD 編碼后,將乘法系數中1 的個數降到最低,從而減少加法(或減法)的次數.CSD 編碼含三重值{1,0,-1},編碼原則是從最低有效位開始,用100…0(-1) 來取代所有大于2 的1 序列。例如上述HBF中乘法系數b (3)= 0. 28847028573567002,量化后b(3)= 48′h24EC98258D1E(Sfix48_En47),則對應的CSD 編碼b (3)= 0+00+0+000-0-00+0+0-00000+0+0-0-00+0-0+00+000-0(“+”表示1,“-”表示負1)。

x(n)*b(3) = – (x(n) 《 《 1) + x(n) 《 《 5 + x(n)《 《 8 – (x(n) 《 《 10) + x(n) 《 《 12 + … + x(n)《 《 40 + x(n) 《44,因此,經CSD 編碼后, b (3)的乘法運算變成只有10 次加法和7 次減法運算,與傳統的移位相加相比,減少了運算的次數,從而降低了HBF 的功耗。

3 補償濾波器的設計

從圖3 可以看出,CIC 濾波器幅頻特性曲線在通帶內并不平坦,在通帶內信號被衰減。為了克服這一缺點,可加入補償濾波器,它的幅頻特性正好與CIC 濾波器相反,完成對頻率響應的補償,從而擴展了系統的頻率特性。

補償的基本原理是使通帶內信號的衰減為零。補償濾波器的幅值響應與(4)式相反。

當R 足夠大時,補償濾波器的響應接近反SINC 函數,因此補償濾波器也稱之為反SINC 濾波器。

補償濾波器一般可借助MATLAB 仿真,再與CIC濾波器級聯觀察補償后總的頻率響應是否滿足系統要求,從而得出補償濾波器的參數。圖5 為圖3 中CIC濾波器加入補償后的幅頻特性曲線圖。

在圖3 中,衰減點在1kHz 左右,而從圖5 中可以看出,加入補償濾波器后,衰減點出現在2. 5kHz 左右,因此,補償濾波器可以很好地克服由于CIC 濾波器在通帶內幅值衰減的問題。

補償濾波器的采樣頻率為CIC 濾波器降采樣后的頻率( FS / R),為了避免頻率混疊,其截止頻率的最大值為采樣頻率的一半:FC = (FS / R) / 2.在實際應用中,為了得到更加理想的頻率特性,截止頻率一般設定為采樣頻率的四分之一,即FC = (FS / R ) /4.

4 實驗數據以及結論

本設計針對電能計量芯片.Sigma-Delta 的采樣頻率為1792kHz,數字電路工作時鐘為14kHz.CIC 濾波器的降采樣率R =64.根據經驗,當CIC 濾波器的階數比Sigma-Delta 調制器的階數高一階時可以達到較好的效果,因此,本CIC 濾波器設定為3 階,延遲因子為1.半帶濾波器采樣頻率為28kHz,通過MATLAB仿真,6 階通帶頻率為2. 5kHz 可以滿足系統要求。在實驗過程中利用Verilog HDL 語言,HBF 采樣對稱結構以及CSD 編碼,在CSMC 0. 18μm 工藝下綜合,得到面積與功耗如表1 所示。

5 結束語

本設計根據電能計量芯片的要求,對Sigma-Delta降采樣濾波器進行優化設計。由于單級CIC 濾波器在實現高倍降采樣率時功耗大,效果不理想,因此,本設計對128 倍的降采樣進行分級抽取,前級采用CIC 濾波器進行64 倍抽取,后級采用半帶濾波器實現2 倍抽取。在HBF 的實現過程中采用對稱結構以及CSD 編碼,減少運算過程中乘法的次數以及乘法運算過程中移位相加次數,降低了電路功耗。與傳統方法相比,經優化后,電路面積減少8% ,功耗降低15% .

-

芯片

+關注

關注

458文章

51526瀏覽量

429491 -

智能電網

+關注

關注

35文章

2952瀏覽量

116692 -

濾波器

+關注

關注

161文章

7919瀏覽量

179507

發布評論請先 登錄

相關推薦

求助,AD7190關于Σ-Δ ADC其中的抽取濾波器的數據轉換問題求解

Σ-Δ ADC數字濾波器類型

數字下變頻中抽取濾波器的設計及FPGA實現

FPGA的FIR抽取濾波器設計詳細教程

關于高頻數字抽取濾波器的設計

基于FPGA的_ADC數字抽取濾波器Sinc_3設計

ADC數字下變頻器:抽取濾波器和ADC混疊,第1部分

應用于電能計量芯片中Σ-△ADC的數字抽取濾波器的設計

應用于電能計量芯片中Σ-△ADC的數字抽取濾波器的設計

評論