1 引言

隨著移動(dòng)及便攜式電子設(shè)備的普及和芯片頻率的不斷提高,功耗成為電路設(shè)計(jì)中必須考慮的重要因素。近來(lái),集成電路設(shè)計(jì)工具已經(jīng)逐步支持多電壓設(shè)計(jì),因而,使得對(duì)適合多電壓實(shí)現(xiàn)的數(shù)字信號(hào)處理部件的算法改進(jìn)、體系結(jié)構(gòu)、以及邏輯電路等的研究成為進(jìn)一步降低功耗的關(guān)鍵問(wèn)題。

通常電路都工作于相同的電壓,多電壓技術(shù)是劃分出不同的電壓區(qū),進(jìn)而采用不同供電電壓以降低功耗。以往的研究大多是按照系統(tǒng)中各個(gè)部件不同的頻率或性能來(lái)劃分不同電壓區(qū)。而高性能數(shù)字信號(hào)處理設(shè)計(jì)中很多情況都是數(shù)據(jù)通路上的大量計(jì)算,工作頻率基本都是一致的,因此本文針對(duì)這種情況尋求適合多電壓設(shè)計(jì)的電壓分區(qū)方案。在單一頻率的電路層劃分出不同的供電電壓區(qū),意味著把對(duì)應(yīng)于不同時(shí)間約束的路徑,確定為不同的電壓需求,按照布局情況進(jìn)行電壓區(qū)的劃分。由此可知,當(dāng)長(zhǎng)短路徑規(guī)則的歸屬在不同的模塊時(shí),則易于用多電壓技術(shù)實(shí)現(xiàn),但大多數(shù)情況是長(zhǎng)短路徑交織在一起,很難按長(zhǎng)短路徑分組劃分不同電壓區(qū)。

本文提出的方法使得電路層錯(cuò)綜在一起的路徑按照其不同的時(shí)間延遲規(guī)則的分離開(kāi),關(guān)鍵路徑和各種不同延遲的非關(guān)鍵路徑對(duì)應(yīng)為不同的模塊,針對(duì)不同的路徑長(zhǎng)度采取不同的供電電壓。通過(guò)剩余數(shù)方法將一個(gè)乘法運(yùn)算化簡(jiǎn)為幾個(gè)非常簡(jiǎn)單的乘法或加法,并將濾波器按照不同的路徑延遲劃分幾個(gè)相互獨(dú)立的模塊,使之適合采用不同的供電電壓,從而降低功耗。

2 路徑成組分離分析

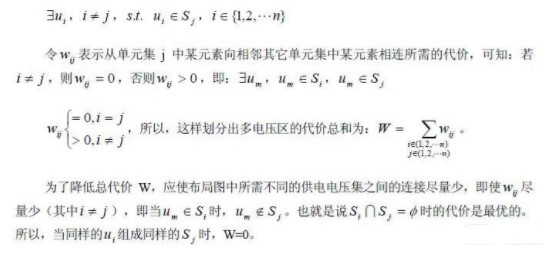

假設(shè)在綜合后的電路網(wǎng)表中,有n 種不同長(zhǎng)度等級(jí)的路徑,分別采用n 種不同的供電電壓。那么在需要多電壓供電的電路的布局布線圖中,將需要用不同電壓供電的單元集(即不同長(zhǎng)度的路徑)記作ui ,i=1,2,Ln,i表示共需n種不同的電壓。

在標(biāo)準(zhǔn)單元設(shè)計(jì)的電路級(jí),電壓供電區(qū)是規(guī)則的方框區(qū),因此用方框?qū)⑿枰撤N電壓的單元區(qū)框起,每一個(gè)方框內(nèi)的所有單元組成一個(gè)單元的集合,記作Sj ,j=1,2,Ln。對(duì)于用Vi 供電的單元ui ,可以用比Vi 高的電壓Vj 》Vi 供電,不影響性能,但不能用小于Vi 的電壓供電。

由于EDA 工具自動(dòng)布局的作用,不同的路徑被隨機(jī)的分布在版圖上,不同路徑上的單元也是無(wú)規(guī)律的分布,也就是說(shuō)所需不同電壓的單元是不規(guī)則分布的,因此按照上述劃分集合的方法對(duì)布局圖中的單元進(jìn)行劃分后,每個(gè)集合中將存在不同供電電壓的元素,即:

通過(guò)以上分析,如果能夠把整個(gè)電路按照不同的路徑長(zhǎng)度成組分離為不同的區(qū)域,則采用多電壓實(shí)現(xiàn)的代價(jià)最小。下一節(jié)將以剩余數(shù)系統(tǒng)為例詳細(xì)介紹路徑成組分離的多電壓實(shí)現(xiàn)。并在后面給出面積與功耗的優(yōu)化結(jié)果分析。

3 剩余數(shù)方法

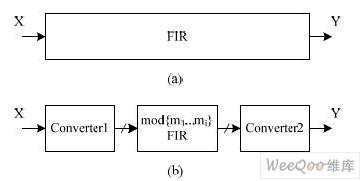

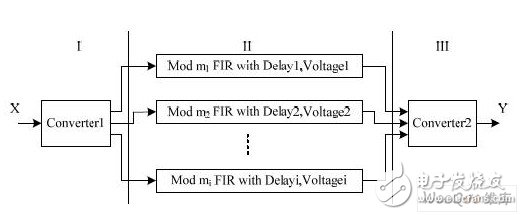

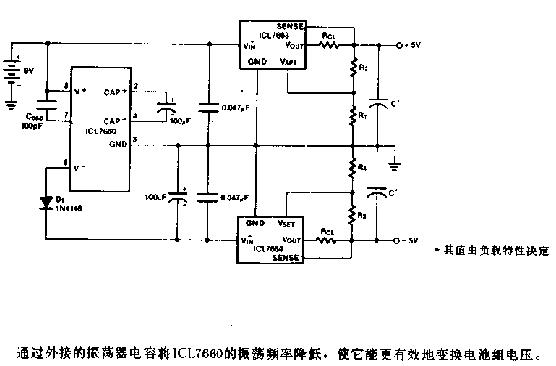

與常用的濾波器的結(jié)構(gòu)略有不同,用剩余數(shù)方法實(shí)現(xiàn)FIR filter 的結(jié)構(gòu)如圖1,該方法需要先將正常的輸入轉(zhuǎn)換為一組(設(shè)組內(nèi)元素個(gè)數(shù)為i)余數(shù)表示,然后是i 個(gè)獨(dú)立的FIR,最后將這一組獨(dú)立的FIR 的計(jì)算結(jié)果再轉(zhuǎn)換為正常的輸出。

圖1 (a) 傳統(tǒng)FIR 結(jié)構(gòu)(b) 剩余數(shù)方法FIR 結(jié)構(gòu)

用剩余數(shù)表示來(lái)實(shí)現(xiàn)FIR filter ,其功能上是等效的,但是其增加了正常模式和剩余表示之間的轉(zhuǎn)換,同時(shí)由于采用余數(shù)的模乘和模加,大量節(jié)約了濾波器的乘累加資源。因此,在整體實(shí)現(xiàn)上,是否能節(jié)約面積和功耗將主要決定于轉(zhuǎn)換部件的開(kāi)銷(xiāo)。

3.1 選擇合適的一組模

對(duì)于硬件電路實(shí)現(xiàn),從運(yùn)算簡(jiǎn)單的角度出發(fā)來(lái)選擇一組模,當(dāng)然最好是2n ,其次是形如2n ±1,所以模組可以取為:彼此互素的一組數(shù)mi = {2 p1 ±1,2 p2 ±1,L2q }。

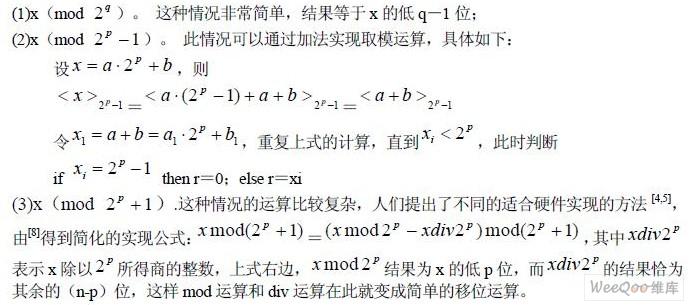

3.2 正常模式到剩余表示的轉(zhuǎn)換

正常表示到剩余表示的轉(zhuǎn)換實(shí)際就是取模運(yùn)算,對(duì)于上面選定的一組模,取模運(yùn)算有以下三種:

3.3 剩余表示到正常表示的轉(zhuǎn)換

如果按照中國(guó)剩余定理,這一步的計(jì)算將非常復(fù)雜。由[6]可將原來(lái)中國(guó)剩余定理算法中復(fù)雜的乘法、mod 運(yùn)算都化簡(jiǎn),剩下的只有查表、加法和移位操作。對(duì)于二進(jìn)制補(bǔ)碼表示的有符號(hào)數(shù),可采用[6]提出的將負(fù)數(shù)轉(zhuǎn)換到正數(shù)去做的方法。

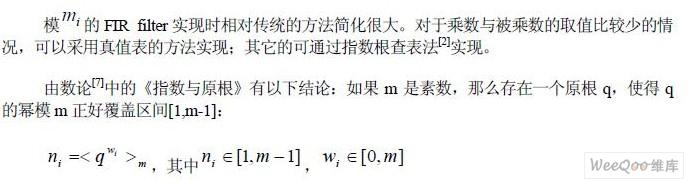

3.4 模乘的實(shí)現(xiàn)

n 和w 之間的轉(zhuǎn)換可以通過(guò)查表實(shí)現(xiàn),對(duì)n=0 的情況在外面判斷,即n=0 時(shí)結(jié)果為0。

3.5 多電壓分區(qū)

從體系結(jié)構(gòu)可以看到,RNS 方法將濾波器的結(jié)構(gòu)劃分為3 部分,如圖2 中ⅠⅡⅢ

圖2 多電壓分區(qū)圖

其中中間部分有i 條相互獨(dú)立的路徑(i 的值為所選定的一組模的數(shù)量),每條路徑由于其模乘運(yùn)算的復(fù)雜度不同而導(dǎo)致電路級(jí)的路徑時(shí)延也大不相同。顯然,模乘運(yùn)算最復(fù)雜的一條路徑將成為中間部分關(guān)鍵路徑,因此可以把時(shí)延明顯較小的路徑i 的FIR filter 模塊采用低電壓實(shí)現(xiàn)。

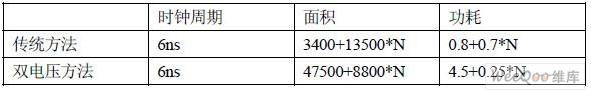

4 功耗與面積分析

以12bits 輸入,8bits 系數(shù)為例。根據(jù)前面選模的方法選取modulo sets = {3, 5, 7, 17, 31, 32}; Converter2采用流水線復(fù)用技術(shù)實(shí)現(xiàn),共需要7個(gè)表、1個(gè)加和一些DFF的資源。下面先看一下在TSMC0.25工藝時(shí)單一電壓情況下不同的模mi 路徑的時(shí)延信息,如下表:

由于模3、5、31、32 路徑上的單個(gè)tap 的時(shí)延都小于3.6ns ,相當(dāng)于富余了40%的時(shí)序約束(6-3.6=2.4ns ),我們就可以通過(guò)在這些非常富余的路徑上降低供電電壓來(lái)降低功耗。在雙電壓設(shè)計(jì)下,將供電電壓從2.5V 降到2.0V,功耗大約是4.5+0.25*N 。在同樣的工藝下實(shí)現(xiàn)傳統(tǒng)FIR, 得到功耗面積與抽頭數(shù)的關(guān)系為:設(shè)抽頭數(shù)為N

當(dāng)抽頭數(shù)為16 時(shí),采用此雙電壓方法可節(jié)省20%-30%的功耗。

5 結(jié)論

長(zhǎng)短路徑成組分離方法是指把路徑長(zhǎng)度分成不同的級(jí)別,每一個(gè)級(jí)別結(jié)合時(shí)序約束確定不同的電壓,這樣就把原來(lái)都按最長(zhǎng)路徑規(guī)定的單一電壓電路轉(zhuǎn)換為多電壓電路。分析了以往多電壓研究中電壓分區(qū)的原則,而高性能數(shù)字信號(hào)處理設(shè)計(jì)中由于數(shù)據(jù)通路上大量的計(jì)算,使得以往的原則并不適用;通過(guò)對(duì)電路布局的多電壓代價(jià)進(jìn)行分析,得出把電路按照不同的路徑長(zhǎng)度成組分離為不同的區(qū)域時(shí),易于采用多電壓實(shí)現(xiàn)。以剩余數(shù)方法為例仿真分析結(jié)果顯示功耗有明顯優(yōu)化。

-

芯片

+關(guān)注

關(guān)注

460文章

52520瀏覽量

440982 -

濾波器

+關(guān)注

關(guān)注

162文章

8138瀏覽量

182081 -

eda

+關(guān)注

關(guān)注

71文章

2930瀏覽量

177997

發(fā)布評(píng)論請(qǐng)先 登錄

鋰電池成組不一致及優(yōu)化方案

初探成組技術(shù)應(yīng)用

高效氨分離器氣液分離機(jī)理與應(yīng)用

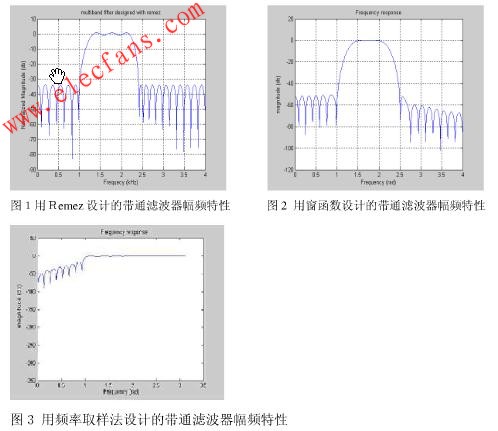

基于Matlab的FIR濾波器的優(yōu)化設(shè)計(jì)方法

基于FPGA的FIR數(shù)字濾波器的優(yōu)化設(shè)計(jì)

硬件與軟件對(duì)實(shí)現(xiàn)FIR濾波算法的影響

團(tuán)隊(duì)成員信息共享的路徑優(yōu)化算法

FIR數(shù)字濾波器優(yōu)化設(shè)計(jì)

負(fù)荷恢復(fù)的機(jī)組分層協(xié)調(diào)恢復(fù)優(yōu)化

基于約束關(guān)鍵路徑的代價(jià)優(yōu)化調(diào)度算法

關(guān)于高分子分離膜材料及其研究進(jìn)展

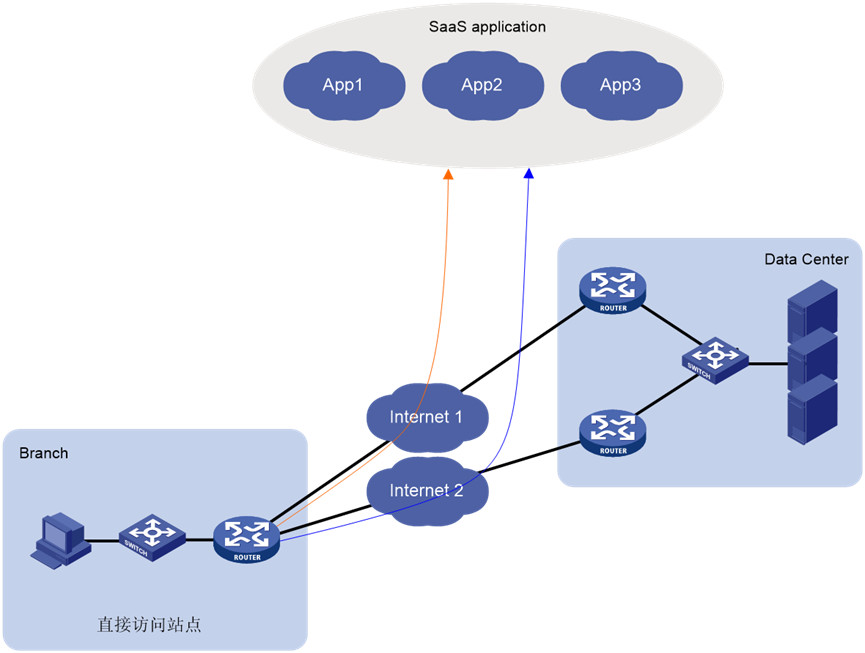

SaaS路徑優(yōu)化技術(shù)實(shí)現(xiàn)

評(píng)論