與開發成本很高的ASIC相比,FPGA可重復編程的性能正受到系統設計者的青睞。此外, FPGA的性能和功能也越來越強大,包括32位軟處理器、SERDES、 DSP塊和高性能的接口。現在的低成本FPGA甚至可以滿足大批量的應用。設計人員采用FPGA能夠快速開發產品,以應對產品快速上市(市場要求縮短產品的開發時間)和遠程更新的需求。

但是,把器件生產、現場更新和固件遠程重構的工作外包可能會導致FPGA被復制、克隆或盜版。這對某些企業是個嚴重的問題,因為有些算法對企業保持競爭優勢是必不可少的,而外包可能使這些算法被別人利用。因此,考慮FPGA設計的安全性是一件非常重要的事。

FPGA有兩種類型 :基于SRAM、需要用外部引導器件配置的易失FPGA,以及將配置保存在內存中因而不需要外部引導器件的非易失FPGA。基于 SRAM的FPGA是易失器件。如果切斷電源,配置即被刪除,必須對器件進行重新配置,然后器件才能工作。這類器件可以用處理器或使用SPI或并行閃存通過JTAG端口編程。就安全性而言,它們是很脆弱的。一旦系統上電,盜版者就能輕而易舉地獲取FPGA的位流。 Flash和反熔絲FPGA是非易失性的器件,它們上電后即可編程,無需使用任何外部存儲器。這些非易失器件擁有最高級別的安全性。但是,反熔絲FPGA受到兩個方面的制約: 1 )它們不能再次編程。2 )它們的性能和內存容量有限。而Flash FPGA和SRAM FPGA是可以重復編程的。

盜版行為分為幾種類型:“克隆”復制系統元件的行為,甚至不必知道內部的邏輯。通過攔截FPGA的位流和復制配置,可以輕松地克隆一個低成本SRAM FPGA。“逆向工程”需要理解FPGA的邏輯功能,以便進行修改以滿足盜版者的需要。盜版者可以分析無保護的位流以復制原先的設計,或解剖器件分析其內容。還有一個被廣泛使用的盜版手段是“生產超過客戶訂購量的系統”,然后向市場出售多余的系統,而專利持有者卻無法從中取得收益,沒有任何方法可以阻止不擇手段的分包商這樣做。最后一種盜版方法是“盜竊服務”,盜版者通過破解系統的安全設置來獲得特定的服務,如收看衛星電視節目。

打擊盜版可以采用多種安全措施,最簡單的方法的是使用一個保密位,防止FPGA的配置數據被截獲。有了這個保密位,盜版者如果試圖讀取配置數據,讀出的數據將全部為零。所有的FPGA都有這種類型的保護。然而,如果引導文件位于器件的外部,相對就比較容易復制配置,標準的SRAM FPGA就是這種情況 。如果配置數據是在器件內部,如非易失FPGA ,保密位就會有很好的保密效果。

與反熔絲FPGA不同 ,SRAM FPGA和Flash FPGA是可重復編程的,它們允許用戶調整設計或賦予FPGA一個全新的功能。此外,現在甚至可以遠程修改FPGA配置文件,從而修改系統。雖然重構對某些應用來說是個優點,但它也可能成為一個安全隱患,因為盜版者可能攔截并獲取新的碼流。不過這可以通過在傳輸時保護位流來解決。

雖然Flash FPGA比SRAM FPGA更安全 ,它們也有缺點。它們的密度和存儲容量有限,功能和I/O的速度也有限。

針對這些缺點,萊迪思半導體公司已經開發出一種創新的技術,它結合了以下兩種技術的優點:

* 性能和存儲器容量較大的低成本SRAM

* 可以內部存儲重構數據的Flash

萊迪思獨特的flexiFLASH技術,將SRAM和Flash整合在同一個FPGA中,可以同時實現以下幾個方面的優點:

* 位流配置

* 以最短的系統中斷時間進行遠程重新配置

* 數據保護和器件加鎖

復雜系統中的設計安全性

工程師正面臨著構建日益復雜的系統的挑戰。

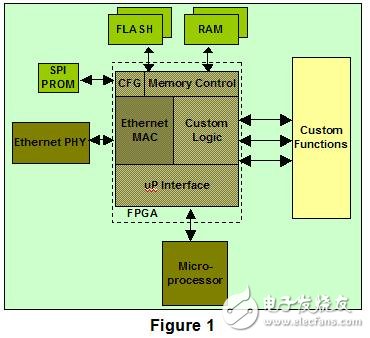

圖1展示了一個FPGA與微處理器相連的系統 。微處理器通過一個外部PHY和一個集成在FPGA內的MAC 與以太網連接。與競爭者的產品不同,這個微處理器中還包含用戶邏輯。 FPGA通過一個Flash來配置。Flash和RAM中包含有微處理器的程序和系統的數據。如果系統需要更新,就通過以太網來發送數據。為了保護設計, FPGA數據和位流都經過了加密。但是,發送到微處理器的數據和指令未加擾,因此盜版者能夠查看此數據并加以復制。一種可能的解決辦法是在FPGA內實現軟微處理器,它可以訪問FPGA的內部存儲器組,而從外部卻無法看到存儲器組。這些存儲器組可以用來存儲重要的算法和數據。

圖1 FPGA與微處理器相連的系統

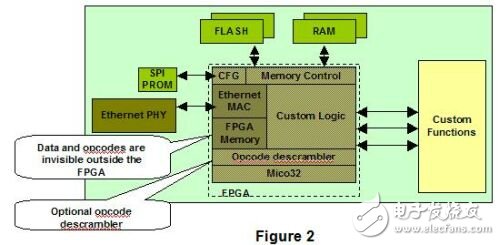

圖2展示了同一個設計,但處理器集成在FPGA之中。圖2中采用的軟微處理器是LatticeMico32 。設計師構建了解擾器,因此加擾是機密的。使用解擾器允許加密的指令存儲在外部存儲器。為了加密位流,萊迪思為幾款FPGA提供了128位AES密鑰。

圖2 處理器集成在FPGA之中

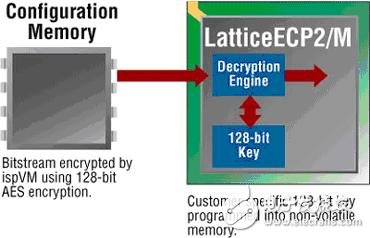

首先,工程師應用萊迪思的軟件設計工具套件ispLEVER ( 7.0或更高版本)開發FPGA代碼,完成綜合、映射、布局布線和仿真后,產生位流,經最后驗證后再用ispVM系統( 萊迪思的編程工具)對電路板編程。當設計師對系統的功能感到滿意時,此時就要來做保護設計的工作。可以用萊迪思的ispLEVER工具或萊迪思的編程工具ispVM System對位流加密,用戶可選擇128位密鑰。編碼的位流可以是十六進制(從0至F ,不區分大小寫)或一個ASCII密鑰(可用所有字母數字字符和空格,大小寫敏感),然后使用任何非加密的文件編碼將該位流加載到配置存儲器中。

圖3 用128位AES密鑰保護設計

現在密鑰應該已經保存在一個可編程存儲區。編程是通過器件的JTAG端口進行。應該注意到,用密鑰對位流加了密,現在只能通過加密的位流對FPGA進行配置。用sysCONFIG接口或JTAG接口可以對萊迪思的FPGA進行編程。該sysCONFIG接口可以讓用戶使用集中配置模式,或Flash SPI ,或以并行的方式使用并行配置模式重新輸入數據。符合IEEE 1149.1和IEEE 1532標準的JTAG端口允許以突發位流(或快速編程)模式、或用1532模式對數據進行編程。JTAG端口用來對器件中的AES 128位密鑰編程。不需要用特別的模式來保存FPGA中的128位密鑰。

在萊迪思的FPGA中使用一個編碼位流可以防止器件的配置被重新讀取,但需要一些措施來確保配置能夠正確地運作。位流未加密時,FPGA執行CRC操作。如果程序不正確,DONE信號保持在0,INITN變為0 。用戶仍然可以訪問JTAG Usercode寄存器。對FPGA的位流譯碼時,它存儲位流用戶碼,用來存放FPGA應用程序的版本號。

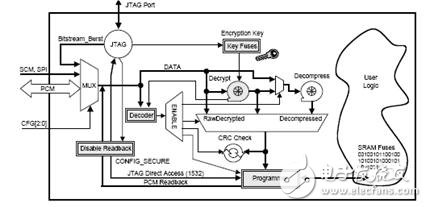

圖4展示了加密位流的數據路徑。當數據進入FPGA時,解碼器讀引導程序,前面所有的數據被忽略。即使解碼器檢測到加密的文件,如果FPGA的密鑰未被編程,數據則被阻止,DONE信號保持在‘0 ’ (表示配置失敗) 。如果密鑰已被編程,FPGA檢查引導程序,指出后面所有的數據應通過解碼器。然后FPGA檢查標準引導程序,得知數據是否已被壓縮。如果數據沒有被壓縮,則將它直接發送到解碼單元。如果數據已壓縮,就先把它送到解壓縮引擎,然后再送到解碼單元。一旦通過CRC校驗,即對SRAM進行編程。DONE位被激活時,解壓縮和譯碼擎不工作,允許其它JTAG鏈元件接收配置數據。

圖4 加密位流的數據路徑

萊迪思的經濟型ECP2/M FPGA擁有位流加密功能,內置閃存的非易失LatticeXP2 FPGA也有此功能。LatticeXP2 FPGA把SRAM映射合并入同一塊芯片,設計和含有位流配置的Flash映射都在此芯片上工作。當設計師重點關注電路板的面積和快速啟動時間時,這類器件特別有用。

內置閃存的FPGA

非易失FPGA提供額外的Flash保護安全功能,可以防止內存因意外或未經授權的操作被擦除或重新編程。Flash保護功能采用64位密鑰。

對器件進行刪除或重新編程時, ispVM System會核查Flash是否被保護。如果是,就要求用戶輸入64位密鑰,然后ispVM檢查這個密鑰是否與存儲在器件中的密鑰一致,如果一致就執行操作。但是,如果丟失了密鑰,器件就再也不能被擦除了。

這些安全性措施不僅保護了用戶電路板上的設計,而且也防止了試圖修改系統功能的盜版行為。這些功能還有助于遠程的系統更新。萊迪思FPGA提供這一功能,使用戶可以通過對FPGA重復編程來更新他們的系統,而不會中斷它與周圍元件的聯系。此功能被稱為TransFR 。

FPGA最值得注意的的特點是設計人員很容易對器件進行重構。但是,重構通常意味著系統要中斷很長時間。但是,萊迪思開發的TransFR技術將重構的影響降至最低。萊迪思的幾個FPGA系列都支持TransFR技術,包括那些含有內置閃存的器件,如MachXO 、LatticeXP和LatticeXP2 ,以及像LatticeECP2 /M那樣的SRAM FPGA。

圖5 用最短的中斷系統時間進行遠程更新

TransFR是一種同時使用基本任務編程和邊界掃描單元的技術。基本任務編程修改非易失存儲器的內容(內部的或外部的) ,以便使FPGA的SRAM部分繼續工作。萊迪思的FPGA擁有可以取樣和預加載的邊界掃描單元,可以在編程時控制FPGA的I/O。

圖6 執行TransFR的4個步驟

執行TransFR的4個步驟:

1,進行基本任務編程。系統對FPGA的非易失性存儲器再編程,但不會中斷SRAM的功能。

2,可以鎖定I/O的狀態,用戶可以保持或預先確定I/O的狀態。在整個重新配置過程中,I/O的值保持不變,以防止系統被關閉。

3, 接著用JTAG命令把新的配置傳輸至非易失存儲器。一完成對SRAM就執行全局復位,以便使該器件處于一個已知的狀態。然后釋放I/O的狀態,并再次鎖定PLL。

4,釋放輸出,內部邏輯停止對I/O的監測。

要使用TransFR,需要用到ispLEVER開發工具和ispVM。

用戶通過使用128位AES密鑰加密文件和Lattice TransFR技術完成了更新過程,但仍有可能因為系統本身的弱點或違法行為引發系統故障。雖然FPGA的位流是加密的,但是非法操作或傳輸中的錯誤都可能損壞它,從而導致FPGA被阻塞,使系統無法正確地重啟。為了解決這個問題,萊迪思推出了“雙引導 ”功能。

雙引導配置

在配置存儲器中存儲兩個編程文件。

圖7 雙引導配置

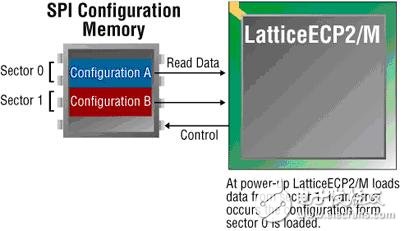

激活PROGRAM引腳或啟動JTAG刷新指令后,FPGA下載存儲在Sector 1的位流 。如果CRC出錯,FPGA自動恢復到Sector 0配置。Lattice XP2非易失FPGA也有此功能。該Flash元件擁有主動配置,還有一個用來存放安全( “golden” )配置的SPI Flash。

萊迪思擁有許多能幫助設計人員保障設計安全的產品。Lattice ECP2/M FPGA是一款擁有128位AES密鑰的高安全性器件。這些經濟的器件提供了大存儲容量(高達5.3 Mbit)、高速I/O和SERDES 。非易失性LatticeXP2 FPGA是市場上一款很獨特的器件,它有著極高的安全性。由于采用了FlexiFlash技術,位流存儲在器件的Flash中, 并由128位AES密鑰對它進行保護。此外, TransFR更是保障了絕對安全的遠程系統更新。

設計的安全性應該是設計過程的一部分,而不是事后再去考慮。無論選擇了哪種技術,最重要的是要防止設計被篡改,無論這個篡改行為是無意的還是非法的。

-

FPGA

+關注

關注

1629文章

21748瀏覽量

603841 -

存儲器

+關注

關注

38文章

7494瀏覽量

163910 -

微處理器

+關注

關注

11文章

2264瀏覽量

82495

發布評論請先 登錄

相關推薦

鋰離子蓄電池安全性的測試與研究方法

nios如何保證安全性的

FPGA器件如何提升物聯網安全性

怎么提高SRAM工藝FPGA的設計安全性?

如何最大限度地提升自助服務設備的安全性?

如何提高SRAM工藝FPGA的設計安全性?

如何提高SRAM工藝FPGA的設計安全性?

軟件安全性測試方法研究

MAX II器件實現FPGA設計安全解決方案

FPGA設計安全性的解決方案研究

FPGA設計安全性的解決方案研究

評論