引 言

硅上液晶顯示(Liquid Crystal 0n Silicon,LCoS)技術(shù)是CMOS半導(dǎo)體集成電路和液晶顯示相結(jié)合的技術(shù)。LCoS技術(shù)具有如下優(yōu)勢(shì):

(1)可以利用標(biāo)準(zhǔn)CMOS工藝和成熟的LCD工藝線(xiàn);

(2)物理尺寸可以做的非常小;

(3)即使像素尺寸非常小,仍可以得到非常高的開(kāi)口率。

由于其技術(shù)和制造優(yōu)勢(shì),LCoS技術(shù)有著廣泛的應(yīng)用前景。由于其尺寸小、功耗低、分辨率高,可以用作移動(dòng)通訊等設(shè)備的顯示屏,如頭盔顯示。目前彩色 LCoS顯示系統(tǒng)主要分為單片和三片式系統(tǒng)2種,單片式系統(tǒng)對(duì)于三片式系統(tǒng)主要有以下優(yōu)點(diǎn):體積小,成本低,易于實(shí)現(xiàn)小型化;三片式需要像素校準(zhǔn),而單片式則不需要。本文主要討論單片彩色LCoS顯示系統(tǒng)的設(shè)計(jì)與實(shí)現(xiàn)。

2 顯示原理

三片式彩色LCoS顯示系統(tǒng)利用空間混色實(shí)現(xiàn)彩色顯示,而單片式彩色LCoS系統(tǒng)只用1片 LCoS芯片,分時(shí)掃描紅、綠、藍(lán)3個(gè)子場(chǎng)的圖像,并且在每個(gè)子場(chǎng)結(jié)束的時(shí),分別將對(duì)應(yīng)顏色的背光燈打開(kāi),利用人眼的視覺(jué)殘留效應(yīng)實(shí)現(xiàn)彩色顯示。當(dāng)子場(chǎng)的頻率越高,圖像的閃爍程度就越低。

3 系統(tǒng)總體概述

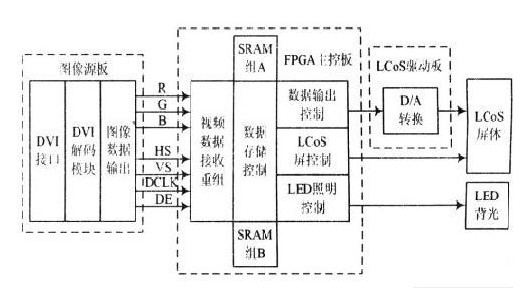

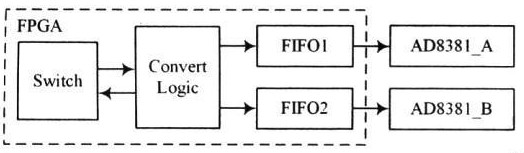

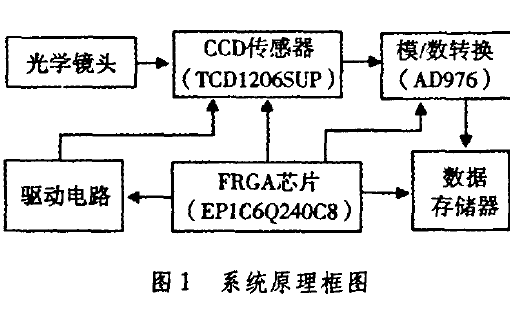

單片彩色LCoS整個(gè)系統(tǒng)的框圖如圖1所示

在整個(gè)系統(tǒng)的最前端是l塊以A139887A為主芯片的圖像源板,該板負(fù)責(zé)對(duì)DVI信號(hào)進(jìn)行解碼,解碼后的信號(hào)交由后面的FPGA板進(jìn)行處理;FPGA板除了對(duì)圖像數(shù)據(jù)進(jìn)行重組外,還需要產(chǎn)生LCoS驅(qū)動(dòng)板和LCoS芯片所需的時(shí)序,F(xiàn)PGA芯片使用Altera的EPlC6,另外板上還有 2組6片SRAM作為圖像數(shù)據(jù)的緩存;LCoS驅(qū)動(dòng)板的任務(wù)是進(jìn)行D/A轉(zhuǎn)換,驅(qū)動(dòng)LCoS芯片模塊進(jìn)行顯示,該驅(qū)動(dòng)板包括D/A芯片AD8381和 LCoS芯片的電源模塊;LCoS芯片模塊則包括LCoS顯示芯片、LED背光模塊以及光學(xué)組件。

4 主要芯片介紹

主控板的核心器件FPGA采用Altera公司的EPlC6Q240C8,該器件包括5 980個(gè)LE,80 kb的內(nèi)部SRAM,2個(gè)內(nèi)部PLL,最大可支持185個(gè)用戶(hù)I/0管腳。經(jīng)過(guò)*估,其豐富的資源可以很好地完成LCoS的主控單元的所有功能,包括:接收前級(jí)轉(zhuǎn)換好的視頻數(shù)據(jù),處理后保存到一組RAM中,同時(shí)從另一組RAM中讀出處理好的數(shù)據(jù)送至D/A,并控制D/A轉(zhuǎn)換,產(chǎn)生LCoS的上屏?xí)r序和 LED光照系統(tǒng)的控制時(shí)序。

板載SRAM采用ISSI公司的IS61LVl0248,用作圖像數(shù)據(jù)的緩存,單片容量為1 M×8 b字節(jié)。本系統(tǒng)共使用6片這樣的SRAM。分為2組,每組3片,進(jìn)行乒乓操作。每組SRAM地址線(xiàn)共享,數(shù)據(jù)線(xiàn)位寬擴(kuò)展為24 b。

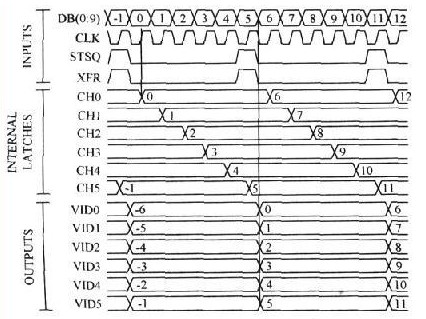

本系統(tǒng)D/A轉(zhuǎn)換采用Analog Device公司的AD8381。該芯片支持高達(dá)100 MHz的10 b數(shù)字輸入,6路9~18 V電壓的模擬輸出。其典型時(shí)序如圖2所示。圖2中DB(O:9)是輸入的數(shù)字信號(hào);CLK是采樣時(shí)鐘;STSQ表示新的一組數(shù)字信號(hào)的開(kāi)始;XFR表示開(kāi)始一次轉(zhuǎn)換,其下降沿有效。本系統(tǒng)采用的LCoS芯片為8路模擬輸入,因此這里采用2片AD8381,每1片用到其中的4路。

根據(jù)圖2中的時(shí)序,并考慮到實(shí)際情況,具體應(yīng)用如下:每個(gè)周期同時(shí)向兩個(gè)AD838l的數(shù)據(jù)口發(fā)送一個(gè)像素?cái)?shù)據(jù),4個(gè)周期后進(jìn)行數(shù)據(jù)鎖存,由STSQ和 XFlR這兩個(gè)控制信號(hào)控制,這樣同時(shí)得到8個(gè)像素的像素值,而不需要如圖2那樣發(fā)送6個(gè)數(shù)據(jù)后再進(jìn)行一次轉(zhuǎn)換。輸出的模擬電壓值在下一個(gè)鎖存信號(hào)的下降沿完成轉(zhuǎn)換。STSQ和XFR這2個(gè)管腳由同一個(gè)FPGA管腳驅(qū)動(dòng)即可。在其他管腳中,E/0信號(hào)和R/L信號(hào)分別用于選擇時(shí)鐘信號(hào)是上升沿有效還是下降沿有效和像素?cái)?shù)據(jù)發(fā)送順序,這里設(shè)計(jì)成外部跳線(xiàn)。另一個(gè)控制信號(hào)INV用來(lái)確定圖像數(shù)據(jù)電壓是正信號(hào)還是負(fù)信號(hào)的,由于液晶的特性,在每幀開(kāi)始時(shí)將其取反。而AD8381的參考電壓VMID和屏的參考電壓VCOM連接在一起,在INV的配合下,實(shí)現(xiàn)對(duì)屏的交流驅(qū)動(dòng)。

5 FPGA程序設(shè)計(jì)

5.1 模塊劃分

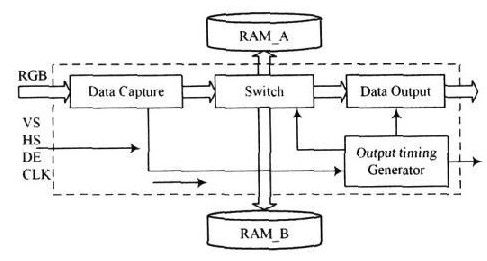

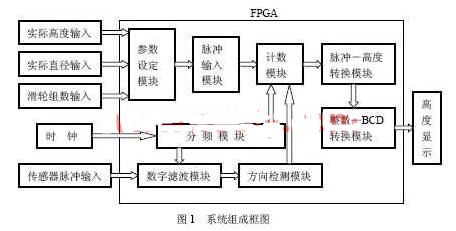

整個(gè)FPGA程序的模塊框圖如圖3所示。主要包括:D/Ata Capture模塊,負(fù)責(zé)將輸入的數(shù)據(jù)按一定的格式順序存放到SRAM中;Switch模塊,負(fù)責(zé)控制RAM的切換;D/AtaOutput模塊,負(fù)責(zé)從 SRAM中讀取數(shù)據(jù)按照一定的格式發(fā)送出去;Output timing Generator模塊,負(fù)責(zé)生成輸出的控制時(shí)序,并且控制D/Ata Output模塊的輸出和Switch模塊的切換,而該模塊的工作是受到D/Ata Cap—ture模塊控制的。

5.2 存儲(chǔ)安排

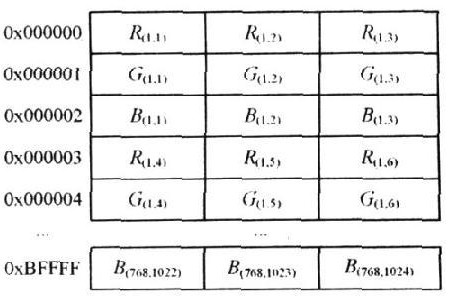

為了獲得較大的數(shù)據(jù)位寬,并且考慮到FPGA管腳數(shù)量,用于緩存圖像的SRAM選用的是3片1 M×8 b容量的,作位擴(kuò)展,這樣可以存放下完整的1幀數(shù)據(jù)。具體說(shuō)就是每個(gè)地址存儲(chǔ)的大小是3個(gè)字節(jié),可以用來(lái)存放3個(gè)像素的數(shù)據(jù)(同種顏色)。地址0x0放置 3個(gè)像素的紅,而地址Oxl存放3個(gè)像素綠,地址0x2存放3個(gè)像素藍(lán),而這3個(gè)地址的3個(gè)像素在屏幕上是第一行的第1,2,3個(gè)像素,接下來(lái)地址0x3 又存放了3個(gè)紅色像素,如此循環(huán),直到地址0xBFFFF存放最后3個(gè)像素的藍(lán)色數(shù)據(jù)。如圖4所示。

5.3 算法流程

(1)D/Ata Capture模塊的數(shù)據(jù)轉(zhuǎn)存算法

D/AtaCapttire模塊負(fù)責(zé)將輸入的數(shù)據(jù)按一定的格式順序存放到SRAM中。每個(gè)時(shí)鐘從AD9887A板過(guò)來(lái)的數(shù)據(jù)是24位的RGB數(shù)據(jù),8位紅,8位綠,8位藍(lán),而實(shí)際輸出的時(shí)候是按照l(shuí)幀紅1幀綠1幀藍(lán)的順序輸出的。因此如果能將讀入的24位RGB數(shù)據(jù)按照一定的格式存放,就可以方便的讀取數(shù)據(jù),格式如圖4所示。

的寄存器r1~r6用來(lái)緩沖6個(gè)像素的RGB值。用6個(gè)狀態(tài)完成類(lèi)似矩陣轉(zhuǎn)換的任務(wù),每個(gè)狀態(tài)會(huì)輸出1個(gè)24 b的轉(zhuǎn)換好的數(shù)據(jù),并生成地址,即每個(gè)狀態(tài)都會(huì)將1個(gè)24 b的數(shù)據(jù)存入到SRAM中,而這24 b就是3個(gè)像素的同一種顏色的值。

(2)D/Ata Output模塊數(shù)據(jù)輸出算法

D/Ata Output模塊是數(shù)據(jù)輸出模塊。每個(gè)時(shí)鐘周期從SRAM中讀取到的是3個(gè)像素的數(shù)據(jù),而每個(gè)時(shí)鐘發(fā)送到每個(gè)AD8381的是一個(gè)像素?cái)?shù)據(jù),因此是不同步的,需要使用雙時(shí)鐘FIFO作流量控制才能使數(shù)據(jù)正確傳輸,具體的讀取操作:如圖5所示。像素O~3放入FIFO1,像素4~7放人FIFO2,這樣依次下去,每個(gè)FIFO放入4個(gè)像素。每個(gè)時(shí)鐘放2個(gè)像素。該處理任務(wù)由Convert Log—ic子模塊完成。還要注意的是由于每種顏色的數(shù)據(jù)不是連續(xù)存放的,因此下一個(gè)地址的值是加3而不是加1。

6 實(shí)驗(yàn)結(jié)果

經(jīng)過(guò)對(duì)比實(shí)驗(yàn)證實(shí),在子場(chǎng)場(chǎng)頻比較低的時(shí)候,單片彩色LCoS顯示系統(tǒng)的閃爍程度會(huì)比較高。由于條件所限,研究中選用的LCoS芯片所支持的最高場(chǎng)頻為120 Hz,該芯片是為三片式LCoS系統(tǒng)設(shè)計(jì)的,因此用在單片彩色系統(tǒng)中具有一定的局限性。實(shí)驗(yàn)中FPGA程序可以實(shí)現(xiàn)90 Hz,120 Hz和180 Hz三種子場(chǎng)頻率。在相同的背光源條件下,90 Hz場(chǎng)頻時(shí)的色彩相對(duì)于其他兩種要好些;180 Hz時(shí)系統(tǒng)也完全能夠正常運(yùn)作,只是色彩稍差,這與LCoS芯片本身有關(guān),不過(guò)其閃爍程度已經(jīng)可以忽略;120 Hz子場(chǎng)時(shí)的閃爍還是比較明顯的,色彩和90 Hz子場(chǎng)時(shí)基本差不多。

因此,要實(shí)現(xiàn)單片彩色LCoS顯示系統(tǒng)的無(wú)閃爍,必須使用較高的子場(chǎng)頻(不低于180 Hz),有關(guān)資料顯示,目前已經(jīng)出現(xiàn)了為單片彩色LCoS系統(tǒng)設(shè)計(jì)的LCoS芯片,其支持的場(chǎng)頻可達(dá)360 Hz,如果選用這樣的芯片,就可以實(shí)現(xiàn)無(wú)閃爍顯示。

就本系統(tǒng)來(lái)說(shuō),已經(jīng)獲得了不錯(cuò)的顯示效果,色彩、對(duì)比度都達(dá)到了比較好的狀態(tài),而且閃爍程度也非常低。如果要獲得更好的顯示效果,就要選擇支持更高場(chǎng)頻的 LCoS芯片。另外,由于該LCoS的響應(yīng)時(shí)間比較長(zhǎng),在屏幕的上沿和下沿還有微弱的色彩混疊現(xiàn)象,這也可以通過(guò)選用支持高場(chǎng)頻的LCoS芯片來(lái)解決。

7 結(jié) 語(yǔ)

盡管本系統(tǒng)已經(jīng)取得了不錯(cuò)的顯示效果,但是還不是很完美,還必須采用新型的LCoS芯片。而對(duì)于這種最高支持360 Hz場(chǎng)頻的LCoS芯片,對(duì)硬件速度和D/A的速度都提出了較高的要求:如果源圖像的場(chǎng)頻為60Hz,而每個(gè)子場(chǎng)的頻率為360 Hz,則應(yīng)該有2幀圖像相同,同時(shí)每個(gè)子場(chǎng)的時(shí)間縮短為原來(lái)的一半(與180 Hz子場(chǎng)頻率比),需要數(shù)據(jù)發(fā)送數(shù)率和D/A速度至少要快一倍。但是這樣的好處就是使本系統(tǒng)所存在的閃爍和色彩交疊顯現(xiàn)的到徹底解決,使單片彩色LCoS 系統(tǒng)的顯示質(zhì)量趨于完美。

本文主要介紹視頻顯示系統(tǒng)的硬件結(jié)構(gòu),以L(fǎng)COS顯示芯片的驅(qū)動(dòng)時(shí)序要求為設(shè)計(jì)標(biāo)準(zhǔn),提出一種基于FPGA的解決方案,使得系統(tǒng)具有靈活性和可修改性,方便以后的升級(jí)以及維護(hù)。并對(duì)FPGA程序的算法做了詳細(xì)的介紹。最后對(duì)系統(tǒng)存在的問(wèn)題做了討論,并提出一些解決方法,以及對(duì)未來(lái)系統(tǒng)的展望。

-

FPGA

+關(guān)注

關(guān)注

1641文章

21912瀏覽量

611744 -

led

+關(guān)注

關(guān)注

242文章

23612瀏覽量

668845 -

芯片

+關(guān)注

關(guān)注

459文章

51910瀏覽量

433420 -

顯示系統(tǒng)

+關(guān)注

關(guān)注

1文章

145瀏覽量

24524

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

基于EP1C6Q240C8的FPGA芯片實(shí)現(xiàn)電子測(cè)試系統(tǒng)的設(shè)計(jì)

FPGA EP1C6Q240C8 外圍電路圖阿

LCoS顯示技術(shù)的大屏幕HDTV介紹

求助:FPGA ep1c6q240c8如何連接外部雙口RAM?

有誰(shuí)用過(guò)EP1C6Q240C8N這個(gè)型號(hào)的芯片嗎?

LCoS芯片設(shè)計(jì)要考慮什么?

LcoS顯示系統(tǒng)的研究

EP1C6Q240C6開(kāi)發(fā)板的原理圖

EP1C6Q240C8實(shí)現(xiàn)LCD滾屏

開(kāi)發(fā)板EP1C6Q240C6開(kāi)發(fā)板原理圖

LCoS顯示芯片--一類(lèi)新型SoC芯片的設(shè)計(jì)與應(yīng)用

通過(guò)VHDL語(yǔ)言和EPlC6Q240C8芯片實(shí)現(xiàn)16QAM調(diào)制器的設(shè)計(jì)

使用FPGA設(shè)計(jì)CCD高速數(shù)據(jù)采集系統(tǒng)的資料說(shuō)明

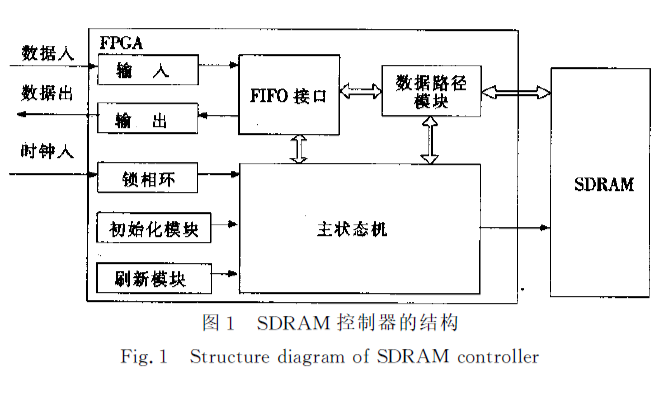

如何使用FPGA實(shí)現(xiàn)高速圖像存儲(chǔ)系統(tǒng)中的SDRAM控制器

評(píng)論