1、 NAND FLASH

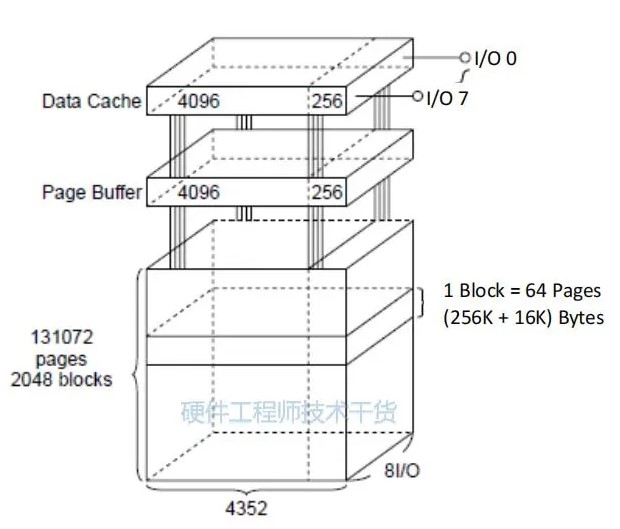

NAND寫回速度快、芯片面積小,特別是大容量使其優(yōu)勢明顯。頁是NAND中的基本存貯單元,一頁一般為512 B(也有2 kB每頁的large page NAND FLASH),多個頁面組成塊。不同存儲器內(nèi)的塊內(nèi)頁面數(shù)不盡相同,通常以16頁或32頁比較常見。塊容量計算公式比較簡單,就是頁面容量與塊內(nèi)頁面數(shù)的乘積。根據(jù)FLASH Memory容量大小,不同存儲器中的塊、頁大小可能不同,塊內(nèi)頁面數(shù)也不同。例如:8 MB存儲器,頁大小常為512 B、塊大小為8 kB,塊內(nèi)頁面數(shù)為16。而2 MB的存儲器的頁大小為256 B、塊大小為4 kB,塊內(nèi)頁面數(shù)也是16。NAND存儲器由多個塊串行排列組成。實際上,NAND型的FLASHMemory可認為是順序讀取的設(shè)備,他僅用8 b的I/O端口就可以存取按頁為單位的數(shù)據(jù)。NAND在讀和擦寫文件、特別是連續(xù)的大文件時,速度相當快。

2、 NAND FLASH與NOR FLASH比較

NOR的特點是可在芯片內(nèi)執(zhí)行,這樣程序應(yīng)該可以直接在FLASH內(nèi)存內(nèi)運行,不必再把代碼讀到系統(tǒng)RAM中。NOR的傳輸效率很高,但寫入和讀出速度較低。而NAND結(jié)構(gòu)能提供極高的單元密度,并且寫入和擦除的速度也很快,是高數(shù)據(jù)存儲密度的最佳選擇。

這兩種結(jié)構(gòu)性能上的異同主要為:NOR的讀速度比NAND快;NAND的寫入速度比NOR快很多;NAND的擦除速度遠比NOR快;NAND的擦除單元更小,相應(yīng)的擦除電路也更加簡單;NAND的實際應(yīng)用方式要比NOR復(fù)雜得多;NOR可以直接使用,并在上面直接運行代碼,而NAND需要I/O接口,因此使用時需要驅(qū)動程序。

3、NAND FLASH在系統(tǒng)中的控制

在沒有NAND FLASH硬件接口的環(huán)境中,通過軟體控制CPU時序和硬件特殊接線方式實現(xiàn)仿真NANDFLASH接口,進而實現(xiàn)在嵌入式系統(tǒng)中脫離NANDFLASH專用硬件接口進行對NAND FLASH讀、寫、擦除等操作的實現(xiàn)方法。

本方法主要工作在以下兩個方面:

軟件方面:針對特殊硬件線路的軟體設(shè)計和嚴格的CPU時序控制;

硬件方面:硬件的線路設(shè)計,利用NOR FLASH專用硬件接口控制NAND FLASH。

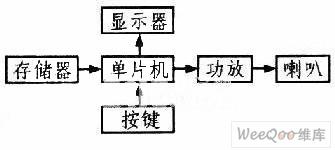

首先建立的開發(fā)平臺如圖1所示。

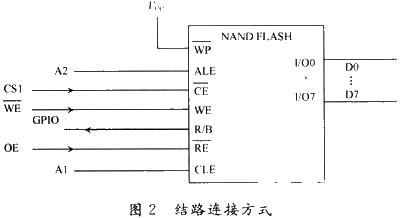

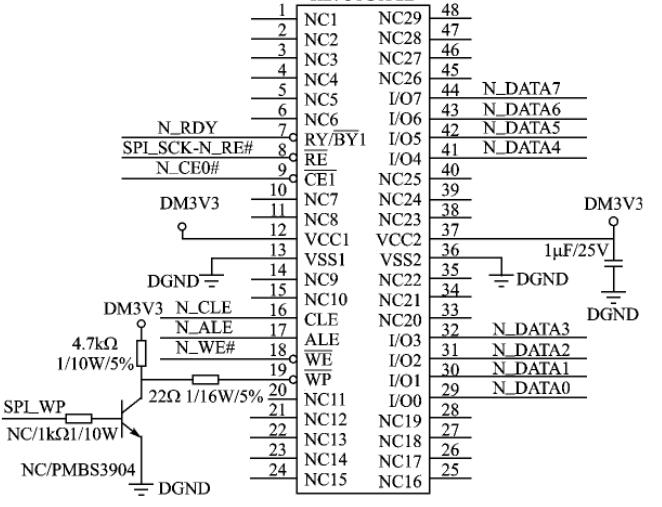

本平臺使用Intel的PXA270 Processor,無內(nèi)建NAND FLASH Controller,使用NOR FLASH Controller控制NAND FLASH,具體的線路連接方式如圖2所示。

NAND FLASH的I/O0~I/07引腳用于對FLASH發(fā)送操作命令和收發(fā)數(shù)據(jù),ALE用于指示FLASH當前數(shù)據(jù)為地址信息,CLE用于指示當前數(shù)據(jù)為操作命令信息,當兩者都無效時,為數(shù)據(jù)信息。CE引腳用于FLASH片選。RE和WE分別為FLASH讀、寫控制,R/B指示FLASH命令是否已經(jīng)完成。逭里選用的是CE don‘t care的NAND FLASH。

NAND FLASH的讀寫操作以page方式進行,一次讀寫均為一個page,erase方式以block方式進行。這種方式,使其讀寫速度大大提高。

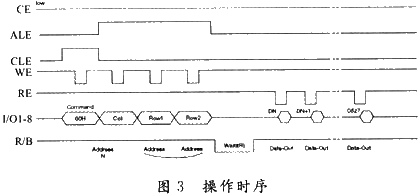

在時序方面,以讀操作為例,其時序如圖3所示。

操作過程主要分為以下幾個步驟:

(1)發(fā)送讀操作命令

CE有效,CLE有效,WE有效,I/O0~I/O8上面數(shù)據(jù)為command代碼數(shù)據(jù)。

(2)發(fā)送地址數(shù)據(jù)(需要讀取的FLASH地址)

CE有效,ALE有效,WE有效,I/O0~I/O8上面為所需地址數(shù)據(jù)。由于地址數(shù)據(jù)較多,所以需要分幾次依次發(fā)送。每次發(fā)送都需要產(chǎn)生WE信號以將其寫入NANDFLASH芯片。

(3)等待R/B信號,最后讀出數(shù)據(jù)

在最后一個地址數(shù)據(jù)寫入FLASH之后,R/B信號即變低。等待芯片完成整個page數(shù)據(jù)讀取之后,R/B信號變高。此時,CE有效,ALE,CLE均拉低,依次產(chǎn)生RE信號,從I/O0~I/O8讀取出所需數(shù)據(jù)。

對于寫操作和擦除操作,其基本原理相同,只是信號順序略有改變,就不再贅述。

由于使用了CPU地址線A1,A2連接CLE,ALE引腳,對CPU低2、3位地址的讀寫操作就意味著對NANDFLASH進行讀寫命令/數(shù)據(jù)操作。如果此程序工作在OS

上的application層的話,MMU已經(jīng)屏蔽程序?qū)Φ讓佑布?/p>

的直接訪問,所以需要對MMU進行設(shè)定,為NANDFLASH開辟一塊。Memory映像區(qū)域,這樣就可以通過OS對底層的NAND FLASH進行操作。以該系統(tǒng)為例,使用CPU的CS1引腳控制NAND FLASH的CE信號,先將其映像為0x24000000地址,此時,對0x24000000地址讀寫即對NAND FLASH芯片進行數(shù)據(jù)讀寫,而對Ox24000002地址寫數(shù)據(jù),使CPU的A1地址引腳為高,即對NAND FLASH發(fā)送command命令,同樣,對0x24000004地址寫數(shù)據(jù),即對NAND FLASH發(fā)送address數(shù)據(jù)。

在對NAND FLASH發(fā)送命令/數(shù)據(jù)之后,由于程序運行速度比FLASH芯片快很多,需要在每一次操作之后插入若干等待周期,并利用CPU的GPIO檢測芯片R/B信號。直至芯片完成本次操作再進行下一步操作。

需要注意的是,在對FLASH發(fā)送命令數(shù)據(jù)過程中的等待,沒有反饋信號可以檢測,只能通過反復(fù)調(diào)試確定其所需等待時間。

在設(shè)計中采用CPU的CS1信號對NAND FLASH進行CE(片選)控制。此處不能采用CPU的GPIO進行控制,因為在嵌入式設(shè)備的ARM CPU中,CPU本身采用了指令、數(shù)據(jù)自動預(yù)讀的高速緩存技術(shù)和流水線技術(shù)。因此,當程序在NOR FLASH里面直接運行的時候(目前絕大多數(shù)嵌入式系統(tǒng)采用的方式),在運行任何兩段相連的代碼中間,CPU都有可能對NOR FLASH進行指令或數(shù)據(jù)的預(yù)讀操作,從而產(chǎn)生大量的RE,OE信號和地址信號。如果使用GPIO控制NAND FLASH的CE信號則無法避免這種影響。CPU的CS1信號是由CPU內(nèi)部自動產(chǎn)生,因此在CPU預(yù)讀期間,CS1信號可以有效屏蔽NANDFLASH芯片。并且,由于NAND FLASH芯片支持CEdon’t care模式,在CE無效的情況下,芯片本身的工作狀態(tài)并不會被干擾,由此保證了NOR FLASH和NANDFLASH在同一CPU界面中互不干擾的穩(wěn)定運行。對于CS1信號的寬度等參數(shù),也需要在實驗中進行調(diào)節(jié),才能保證整個系統(tǒng)快速穩(wěn)定的運行。

4 、NAND FLASH在系統(tǒng)中的讀寫速度

經(jīng)過測試在該系統(tǒng)平臺中,OS為Palm OS 5.4;CPU使用PXA270 312 MHz;SDRAM使用Samsung的16 bdata width HYB25L256160AF-7.5@104 MHz;NANDFLASH選用Samsung 128 MB 8 b I/O NAND FLASHK9F1G08U0A達到在文件系統(tǒng)下面的讀/寫的速度為3 MB/s,擦除的速度為65 MB/s,在手持式設(shè)備中運用性能已經(jīng)夠了。

責(zé)任編輯:gt

-

NAND

+關(guān)注

關(guān)注

16文章

1681瀏覽量

136119 -

存儲器

+關(guān)注

關(guān)注

38文章

7484瀏覽量

163763 -

RAM

+關(guān)注

關(guān)注

8文章

1368瀏覽量

114641

發(fā)布評論請先 登錄

相關(guān)推薦

NAND Flash非易失存儲器簡介

Nand Flash接口定義解析 基于AMD FPGA的Nand Flash接口讀寫實現(xiàn)

NAND Flash的儲存結(jié)構(gòu)與接口設(shè)計

單板硬件設(shè)計:存儲器( NAND FLASH)

Nand Flash存儲管理在DSP系統(tǒng)中的實現(xiàn)

Nand+Flash存儲管理在DSP系統(tǒng)中的實現(xiàn)

NAND FLASH在WINCENET系統(tǒng)中的應(yīng)用設(shè)計

flash存儲器的讀寫原理及次數(shù)

DRAM、NAND FLASH、NOR FLASH三大存儲器分析

基于EPG3231和NAND Flash存儲器實現(xiàn)聲音播放器設(shè)計

NAND Flash 的存儲結(jié)構(gòu)以及NAND Flash的接口控制設(shè)計

基于NAND FLASH存儲器實現(xiàn)在系統(tǒng)中的讀寫和控制

基于NAND FLASH存儲器實現(xiàn)在系統(tǒng)中的讀寫和控制

評論