1、引 言

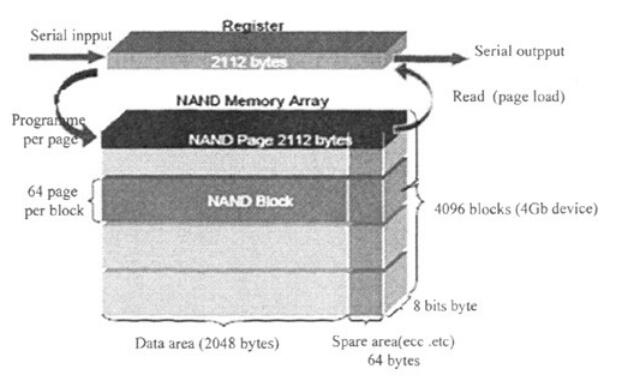

隨著消費類電子產(chǎn)品包括PDA,MP3、智能手機等手持設(shè)備的市場需求逐步擴大,產(chǎn)品間的競爭也愈發(fā)激烈,降低產(chǎn)品的設(shè)計成本,提升產(chǎn)品的市場競爭力成為嵌入式系統(tǒng)開發(fā)者所面臨的重大挑戰(zhàn)。NAND FLASH和NORFLASH作為兩種主要的非易失性存儲器,被應(yīng)用于各種嵌入式系統(tǒng)。其中NAND FLASH主要優(yōu)點在于存儲密度高、容量大,有更占優(yōu)勢的存儲性價比。但是NANDFLASH由于其獨特的頁式讀寫方式,并不適合程序的直接執(zhí)行。因此,從NAND FLASH啟動需要片上存儲器作為代碼執(zhí)行的中轉(zhuǎn)區(qū)。本文所討論的一種系統(tǒng)啟動方式,是在缺少片上存儲器支持的情況下,實現(xiàn)系統(tǒng)直接從NAND FLASH啟動。論文中充分考慮了如何實現(xiàn)軟、硬件之間的協(xié)同工作,以完成SOC系統(tǒng)的設(shè)計。

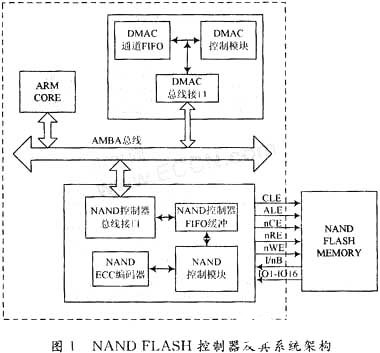

2、NAND FLASH控制器的結(jié)構(gòu)

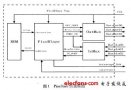

本文所討論的NAND FLASH控制器是針對一款基于ARM7TDMI的SoC芯片,該控制器在芯片中的位置如圖1所示,作為AMBA總線上的一個從設(shè)備集成于AHB上。主要模塊包括總線接口模塊、FIFO緩沖模塊、ECC編碼模塊以及邏輯控制模塊。

總線接口模塊主要的功能是轉(zhuǎn)換AMBA總線上的控制和數(shù)據(jù)信號:將總線上的數(shù)據(jù)送入FIFO或?qū)?shù)據(jù)從FIFO讀出到總線上,將總線上的控制信號轉(zhuǎn)換時序后送到控制模塊。

NAND控制器包含一個寬度為32 b,深度為4的緩沖FIFO,用于解決高速總線與低速設(shè)備之間數(shù)據(jù)傳輸速度的匹配問題。為提高總線的傳輸效率,以及控制器設(shè)計的便利性,NAND FLASH在總線上的數(shù)據(jù)傳輸采用DMA的方式來完成。譬如在讀取FLASH一頁數(shù)據(jù)時,數(shù)據(jù)持續(xù)寫入控制器FIFO,F(xiàn)IFO滿時發(fā)出DMA傳輸?shù)恼埱螅瑫r暫停FLASH的數(shù)據(jù)讀取,控制信號nRE拉高,直至DMA響應(yīng)請求即FIFO不滿時,F(xiàn)LASH的數(shù)據(jù)傳輸重新開始。當(dāng)選擇應(yīng)用的FLASH位寬為8,頁大小為(512+16)B時,控制器需要發(fā)出(32+1)次4拍字寬度的DMA傳輸請求來完成數(shù)據(jù)和校驗信息的讀取。

控制模塊的上作主要是將總線接口轉(zhuǎn)換的控制信號,按照NAND FLASH的接口協(xié)議.將片選、地址、命令、讀寫使能按照所配置的時序要求,發(fā)送到NAND FLASH中,并且控制數(shù)據(jù)的傳輸個數(shù),以及DMA請求、數(shù)據(jù)傳輸完成中斷、數(shù)據(jù)錯誤中斷等系統(tǒng)信號。

NAND FLASH可靠性相對較差,存儲器芯片中有壞塊的存在,會導(dǎo)致存儲數(shù)據(jù)出錯。ECC校驗?zāi)K針對NAND FLASH的可靠性問題,提供了一種查錯、糾錯的機制。ECC校驗碼在數(shù)據(jù)讀人時,由硬件計算完成后寫入到FLASH的校驗位中,當(dāng)此頁數(shù)據(jù)讀出時,校驗碼再次生成與存儲器校驗位中的數(shù)據(jù)進行比較,若相同則沒有損壞位,若不同,則給出出錯中斷,軟件通過檢查比較結(jié)果,判斷出錯位的位置進行糾錯處理。糾錯功能僅針對單bit位的出錯,當(dāng)一個以上位同時在一頁中出現(xiàn)時,ECC校驗不能給出出錯位正確的位置。

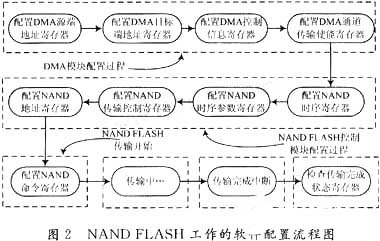

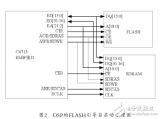

3、NAND FLASH工作的軟件流程

按照上節(jié)對控制器結(jié)構(gòu)以及傳輸機理的分析,NANDFLASH的使用需要在FLASH控制器模塊以及DMA控制器模塊的協(xié)同下完成,工作的軟件流程如圖2所示。

軟件驅(qū)動的主要工作是配置DMA模塊以及FLASH控制模塊,當(dāng)傳輸完成,檢測到中斷后,軟件查詢狀態(tài)寄存器,其中的狀態(tài)位來自FLASH。當(dāng)一次操作完成后,控制器自動向FLASH發(fā)出查詢狀態(tài)的命令0x70,讀出的狀態(tài)字保存在控制器的狀態(tài)寄存器中。

4、NAND FLASH系統(tǒng)啟動的傳統(tǒng)模式

目前支持從NAND FLASH啟動的SoC芯片中,一般都內(nèi)嵌有片卜存儲器。各個處理器廠商對這塊片上存儲器定義的容量大小有所不同,但是啟動模式都是比較一致的。NAND FLASH按頁順序讀取的方式,意味著對當(dāng)前的存儲地址訪問后就無法馬上再次訪問,需在當(dāng)前頁訪問完成后,重新對此頁訪問時,才可對先前的地址單元再次訪問,這就導(dǎo)致了一些程序語句無法執(zhí)行,譬如跳轉(zhuǎn)、循環(huán)等語句的使用。因此NAND FLASH僅作為啟動代碼的存儲區(qū),而真正執(zhí)行的存儲器區(qū)域是內(nèi)嵌的片上存儲器或者片外的SDRAM。

以上文中描述的控制器為例,按照這種啟動模式,程序搬運以及執(zhí)行的過程如下:

![]()

系統(tǒng)上電前,外部硬線NAND BOOT開關(guān)選擇從NAND FLASH啟動。芯片設(shè)計時,默認DMA占有系統(tǒng)總線,DMA按照配置寄存器的默認值工作,其源地址指向NAND FLASH,目標地址指向片上SRAM,NANDFLASH控制器在NAND BOOT選中的情況下,默認向NAND FLASH的首頁發(fā)出讀命令。即上電后,DMA控制器以及NAND FLASH控制器默認的把FLASH存儲器中的第一頁搬到了片上SRAM中。一直到DMA的工作完成前,ARM核無法占用總線。此時零地址映射在片上SRAM,DMA完成搬運后,ARM開始執(zhí)行程序。此段代碼完成的工作包括對SDRAM控制器的初始化,從NAND FLASH搬運核心代碼至SDRAM,配置地址重映射寄存器至零地址處,最后將PC指向零地址的SDRAM。在SDRAM執(zhí)行的代碼開始真正啟動系統(tǒng)。

5、NAND FLASH系統(tǒng)啟動的新方法

一般情況下,片上存儲器在作為啟動代碼轉(zhuǎn)移階石的同時,往往在啟動后也有其特殊的作用。可以作為特殊的程序區(qū),譬如在進行MP3解碼過程中,核心解碼函數(shù)作為頻繁調(diào)用的程序,可以安排在片上SRAM中,以提高讀取速度,提升系統(tǒng)性能。在SoC芯片開發(fā)過程中,在整體架構(gòu)以及模塊功能的變化之后,這塊內(nèi)嵌的SRAM失去了原來的作用,而僅作為NAND FLASH啟動時的代碼跳板,對于整個芯片而言,付出的代價比較大。于是提出了在沒有片上存儲器的架構(gòu)下,從NAND FLASH啟動的一種新模式。

在上述一般模式啟動過程中,片上SRAM所起到的作用,就是執(zhí)行NAND FLASH中第一頁的代碼,將真正的啟動代碼引入到SDRAM,最后將PC指針指向SDRAM。在失去片上SRAM的支持后,可以在控制器的FIFO中去執(zhí)行此段代碼,這需要在硬件以及軟件代碼中作出適當(dāng)?shù)母淖儭?(1) 首先需要改變的是地址映射的機制,系統(tǒng)上電后,ARM即從零地址開始執(zhí)行指令,零地址映射到NAND FLASH的FIFO入口地址,地址的譯碼過程由AMBA總線模塊完成。在外部硬線NAND BOOT拉高的條件下,AMBA從設(shè)備地址譯碼模塊在啟動過程中,將零地址的設(shè)備選擇權(quán)給到緩沖FIFO。在第一頁的指令執(zhí)行完畢后,PC指針也指向SDRAM。

(2) 其次是NAND FLASH控制器在啟動過程中,對數(shù)據(jù)的讀取方式。鑒于NAND FLASH大批量數(shù)據(jù)讀寫的特性,往往采用DMA方式對數(shù)據(jù)進行操作。啟動過程中,由ARM core直接向FIFO讀取數(shù)據(jù),在FIFO讀空的情況下,將從沒備READY信號拉低,等待NAND中的數(shù)據(jù)讀出。并且在此讀取過程中,DMA的請求被屏蔽。

(3) NAND FLASH型號類型眾多,從每頁容量大小、數(shù)據(jù)寬度、地址級數(shù)以及各型號芯片不同的時序參數(shù),決定了一個控制器接口的兼容性要求相當(dāng)?shù)母摺榱思嫒輳牟煌腘AND FLASH啟動,設(shè)置了4根硬線作為選擇。NAND BOOT選擇是否從NAND FLASH啟動;PAGESIZE選擇每頁大小,支持512 B/page,2 kB/page;IOWIDE選擇數(shù)據(jù)端口的寬度,支持8位、16位;AD-DRESSCYCLE選擇發(fā)送地址級數(shù),支持3級、4級、5級地址。時序參數(shù)的配置值可以采用默認的寬松值,在讀取首頁信息之后,將配置值根據(jù)當(dāng)前的時鐘頻率以及芯片類型,選擇舍適的時序值以達到最佳的性能。 (4) 存儲器首頁的代碼是在緩沖FIFO中執(zhí)行的,F(xiàn)IFO的入口地址是一個高24位的選通地址,因此當(dāng)系統(tǒng)啟動時,零地址開始增加,對FIFO中瀆出的指令而言,低8位地址的變化是無關(guān)的,F(xiàn)IFO始終被選通。指令的輸出是默認的順序輸出。這就要求首頁的代碼中不可以出現(xiàn)循環(huán)、跳轉(zhuǎn)等語句,并且要求在128條指令內(nèi)完成需要的操作。

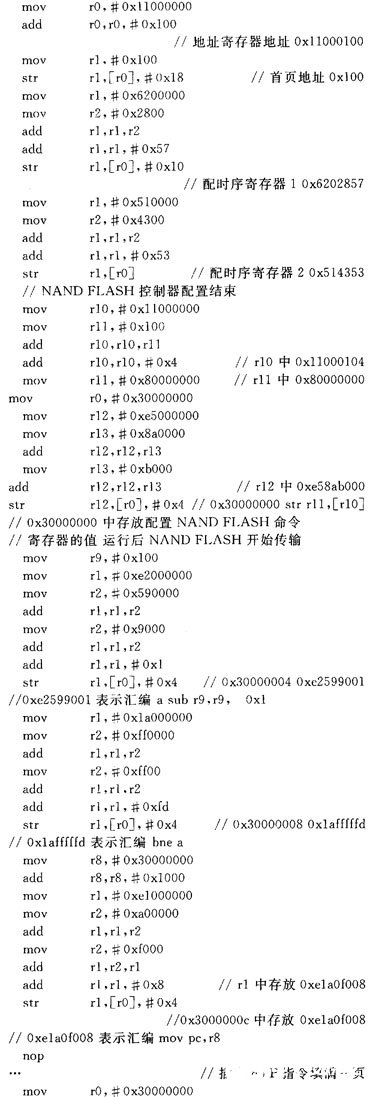

6、啟動代碼和流程的分析

上述的匯編程序即是存放在NAND FLASH首頁的啟動代碼,啟動的流程如下:

(1) 配置DMA控制器的4個寄存器,通道使能后,等待FLASH發(fā)出的搬運請求;

(2) 配置NAND FLASH控制器的3個寄存器,選擇適合的地址、時序參數(shù)與所用的FLASH芯片吻合;

(3) 分別在r8~r11中放入程序需要的備用值;

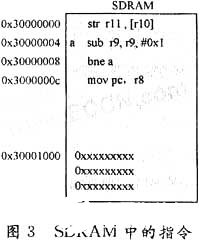

(4) 將需要在SDRAM中運行的4條指令搬入SDRAM 0x30000000處;

(5) 執(zhí)行Nop指令,Nop指令用于填充一頁NANDFLASH中的剩余空間;

(6) 執(zhí)行在頁末的指令,將PC指針指向SDRAM的0x30000000處;

(7) 執(zhí)行SDRAM中的指令,首先啟動NANDFLASH的數(shù)據(jù)傳輸,將程序搬往SDRAM的0x30001000處。其次執(zhí)行一個循環(huán)語句,等待第一頁的程序搬完,之后將PC指針指向0x30001000處,啟動程序從0x30001000處正式開始執(zhí)行。

7、結(jié) 語

本文提出了一種NAND FLASH自啟動的新方案,通過對硬件電路以及軟件代碼作合適的調(diào)整,從芯片中去除了內(nèi)部SRAM,降低了SoC芯片的開發(fā)成本。本方案已經(jīng)通過一款命名為GarfieldV的SoC芯片的測試,達到了預(yù)期的效果。

責(zé)任編輯:gt

-

控制器

+關(guān)注

關(guān)注

112文章

16332瀏覽量

177812 -

NAND

+關(guān)注

關(guān)注

16文章

1681瀏覽量

136121 -

FlaSh

+關(guān)注

關(guān)注

10文章

1633瀏覽量

147944

發(fā)布評論請先 登錄

相關(guān)推薦

標準NAND FLASH控制器/超高速NAND FLASH陣列控制器

請問單片機如何控制nand flash

基于qualcomm平臺的kinect應(yīng)用系列實現(xiàn)Turtlebot的開機自啟動方式

加密芯片C6748 NAND FLASH下載完程序,無法自啟動怎么回事

什么是NAND Flash?如何去使用NAND Flash控制器?

一種NAND FLASH自啟動的新方法

一種在片上系統(tǒng)中實現(xiàn)Nand Flash控制器的方法

基于PicoBlaze的Nand Flash控制器的實現(xiàn)

NAND FLASH在WINCENET系統(tǒng)中的應(yīng)用設(shè)計

基于TMS320C6000DSPS系統(tǒng)的Flash引導(dǎo)自啟動設(shè)計

基于Android系統(tǒng)自啟動程序設(shè)計

NAND Flash控制器的設(shè)計與驗證

NAND Flash主機接口控制器技術(shù)研究

基于NAND FLASH控制器的自啟動方式實現(xiàn)SOC系統(tǒng)的設(shè)計

基于NAND FLASH控制器的自啟動方式實現(xiàn)SOC系統(tǒng)的設(shè)計

評論