系統體系結構

本設計正是基于SOPC的思想,開發實現自主知識產權的MVB收發控制器IP核,借助于QuartersII開發工具,集成至AlteraFPGA器件內部,構建SOC片上系統實現MVB網卡基本功能,相比傳統國外的MVB網卡,大大簡化了系統的結構,降低了開發難度。

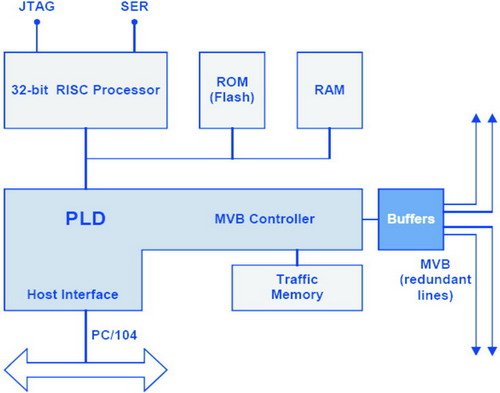

傳統MVB網卡的硬件結構比較復雜,設計實現上有較大的難度。如圖1所示,是Duagon公司的一款典型的MVB網卡d113的硬件結構。其硬件主要有以下幾個部分構成:中央控制器采用高性能的32位ARM處理器,存儲系統由非易失性程序存儲器(ROM)Flash,以及數據存儲器RAM組成,可編程器件上實現MVB收發器以及外部PC/104總線接口。

圖1 d113硬件框圖

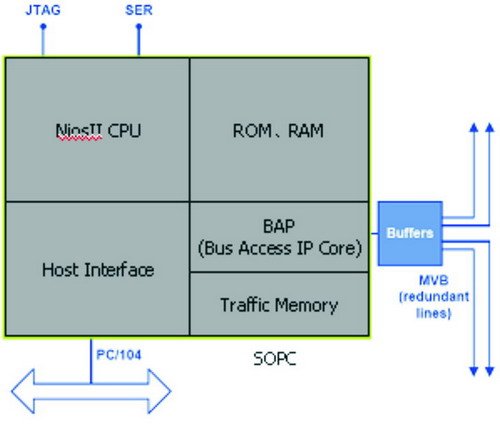

本設計在一片FPGA上,采用SOPC技術實現的MVB網卡:由Altera公司提供的32位高性能軟核處理器NiosII取代ARM處理器,ROM,RAM及TrafficMemory均可以在FPGA片內由SOPCBuilder工具實現,再集成MVB總線訪問IP核便可以構成MVB網卡,實現了真正的片上系統。其硬件框圖如圖2所示。

圖2 網卡結構框圖

總線訪問IP核的實現

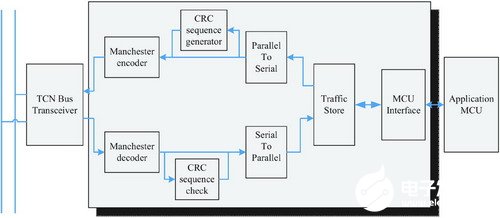

總線訪問IP核是實現WTB和MVB的總線訪問處理器(BAP)的核心內容。由此IP核結合物理層的總線收發器完成總線訪問。總線訪問IP核可分為物理層、數據鏈路層與應用層的接口三大部分。1)在物理層實現基帶曼徹斯特Biphase-L編解碼,介質冗余處理,介質安裝單元接口;用于輸入解碼的數字鎖相環的設計。2)鏈路層包括尋址方式,F-code(功能代碼)的生成,主從設備幀內容的填充,介質訪問控制(MAC)等。3)與應用層的接口通常采用共享存儲器的方法,需要完成端口的定義與維護,通信存儲器的控制等。其邏輯框圖如圖3。

圖3 網卡結構框圖

MVB幀結構

在MVB中有兩種幀格式,一種是只能由總線主設備發送的主設備幀,簡稱主幀,一種是為響應主幀而由從設備發送的從設備幀,簡稱從幀。一個幀以9位定界符開始,主設備幀分界符和從設備幀分界符對防止同步失敗是不相同的。

MVB編碼器

MVB總線數據以幀為基本單位,數據幀采用了曼徹斯特碼傳輸,編碼和解碼器不只是進行曼徹斯特編解碼,幀頭幀尾的特殊編解碼也需要在這里進行,采用傳統的曼徹斯特編解碼器將無法完成此項工作。在本設計中,采用了結合收發器的狀態機具體狀態進行編解碼的設計方法解決這一問題。MVB幀發送器通過控制邏輯模塊調用曼徹斯特編碼與CRC校驗模塊、通信存儲單元模塊完成緩沖區數據的發送。

MVB幀接收器

接收器實現的關鍵是有效數據幀的識別,實現思路類似于發送器,根據編碼校驗可以實現。另一個問題是與總線的接口方式,該設計采用了8位并行數據寬度輸出,加序號標識的方法可以接收任意給定長度的有效數據。

數據校驗

幀數據用一個或更多的8位校驗序列來保護,數據的內容應處理成64位的代碼字(對小一些的數據用16或32位),不包括起始分界符和終止分界符。這個代碼字和隨后的校驗序列應作為最高有效的數據位首先發送。

校驗序列按被其保護的16,32或64位數據的循環冗余校驗(CRC)計算。校驗序列按多項式計算,7位運算結果用一個偶校驗位進行擴展。所有的8位數據取反發送。

通信存儲單元模塊

通信存儲器(TrafficStore)作為MVB標準中的一個重要實現手段,是MVB接口網卡中的重要組成部分。通信存儲器容量的大小依據具體應用而定。在MVB網絡中通常所需要的通信存儲器容量為32或64個端口即可,每個端口需要占用的空間最大為256位,這樣通信存儲器所需要的空間為8kbits或16kbits。開辟FPGA中的DRAM作為通信存儲單元,完成數據交互功能。用來存儲經由MVB總線傳輸的數據,是控制邏輯模塊與編碼校驗單元之間的共享單元。控制邏輯模塊依據通信存儲模塊端口地址的起始地址,以及其數據長度,來讀取相應的過程數據和消息數據等。

Avolon總線接口設計

MVB總線處理IP核與NiosII的接口設計的實現是通過TrafficStore(共享RAM)來實現的。使用QuartersⅡ中的MegaWizard?plug-inManager工具來產生一個雙口RAM模塊,其設置如表1所示。

該通信存儲器與NiosII處理器通過Avalon總線接口。

SOPC片上系統MVB網卡的實現

總線訪問IP核與NiosII的系統集成

利用QuartersII的SOPCBuilder工具我們集成了NiosII軟核處理器、4k的片內RAM、MVB總線訪問IP核(包括編碼器和解碼器)以及LCD控制模塊,構成了一個能實現MVB一類網卡功能的片上系統。

軟件設計

基于以上所述的SOPC系統,我們設計了一個基本的MVB節點以實現過程數據傳輸。本節點將0x14地址設置為源端口,當主幀輪詢0x14地址時,本節點將此端口里的數據打包成從幀發送到總線上面,以刷新0x14地址的宿端口。

altera_avalon_mvb.h的設計,包括總線訪問IP核寄存器讀寫的宏定義。

#defineIORD_ALTERA_AVALON_MVB_SENDREG(base)IORD(base,0)

#defineIOWR_ALTERA_AVALON_MVB_SENDREG(base,data)IOWR(base,0,data)

在主函數里置MVB總線接收允許位,循環等待接收MVB主控制器發過來的主幀。節點在接收到主幀之后,程序進入中斷處理程序。在中斷程序里提取接收到的主幀里的端口地址,并與自身預設的端口地址碼進行比較,如果地址碼相符,則節點將本端口的數據通過MVB發送器發到總線上,實現端口數據刷新操作。

仿真及實現

仿真波形

在本實驗中,對實驗室設計的MVB板卡進行了功能仿真和FPGA驗證,通過對過程數據的發送與接收驗證了所搭建的MVB系統。

實測波形

在編好程序后,再編譯一遍QuartersII工程文件,將得到的.pof文件下載至FPGA內,上電后用示波器測輸出管腳,便可觀察到MVB幀波形。對照IEC-61375協議標準,可以判斷出該波形為符合標準的正確波形,并且源端口節點上收到了正確的數據,從而證明該過程數據端口的成功刷新。

結語

目前國內的列車網絡及控制技術是在技術引進的基礎上發展起來的,國外廠商只愿提供產品而不轉讓關鍵技術。由于難以單獨購買網絡專用芯片等種種原因,目前仍是直接采用國外產品,或用國外(設計)的網卡(萬元以上的高價)等進行系統集成,以此構成列車通信網絡(即國產化)。本論文圍繞MVB總線底層協議展開研究,基于SOPC設計思想,對利用FPGA實現IEC61375協議進行了嘗試,初步完成了MVB網絡I類板卡的設計。目前,對該網絡協議的實現方面還僅限于初期階段,只實現了MVB總線基本的過程數據的收發。該系統的后續還需加入消息監督數據等的通信。在實際的節點應用中,也可能出現各種各樣的問題需要加以改進。

責任編輯:gt

-

控制器

+關注

關注

112文章

16334瀏覽量

177815 -

總線

+關注

關注

10文章

2878瀏覽量

88053 -

IP核

+關注

關注

4文章

327瀏覽量

49485

發布評論請先 登錄

相關推薦

基于SOPC的列車通信網卡的設計

MVB技術在列車PIS組網中的應用

基于SOPC的車輛息線控制器設計方案

MVB總線協議分析儀的設計與實現

多功能車輛總線,深扒MVB協議

MVB三層架構的網絡模型(OPNET仿真)

MVB-CAN通信網關的硬件設計框圖、軟件設計和系統性能測試詳細介紹

采用NET+50和MVBC01芯片實現MVB 2類設備系統的設計

采用可編輯邏輯器件實現MVB總線分析結構的設計

通用MVB從站網卡Modbus協議概述

基于SOPC的MVB收發控制器IP核實現MVB網卡的設計

基于SOPC的MVB收發控制器IP核實現MVB網卡的設計

評論