數字邏輯設計人員在實現設計目標時有不少工具可用。為適應所需的大量邏輯數和數據率,設計人員可選用FPGA。FPGA在相對小的空間內,以多引腳數封裝提供巨大數量的數字邏輯門。

在印刷電路板(PCB)放置多個多引腳FPGA和其他器件,確保所有互連的完整無損是比較困難的。在制造中用X射線技術可以檢驗大概的互連問題, 而需要更精確的方法來檢測制造、調試和復雜PCB更換的互連問題。

一種方法是JTAG(IEEE1149.1)技術。JTAG(聯合測試行動組)功能包括基本的輸入/輸出邊界掃描控制(由1149.1規范確定)以及內部資源的重新編程性和控制。數字設計中所用的很多元件都具有JTAG性能。微處理器可用JTAG提供調試接入。FPGA和CPLD可用JTAG編程。這些JTAG性能為制造、設計和服務人員提供一個強有力的生產高質量板的工具。

在系統中實現JTAG控制邏輯時,考慮DFT(design-for-test),而這與一般的FPGA設計技術是矛盾的。

DFT設計考慮包括:

·主要的測試/調試能力必須與系統開發每個階段的FPGA功能無關。

·FPGA需要在現場更新測試控制邏輯,并且在重新編程期間應變得不起作用。假若希望系統是“5個9”(99.999%)可用的,則需要另一種FPGA結構。

·FPGA通常是JTAG掃描鏈的部分,而且感興趣的是FPGA互連的檢驗。FTAG控制邏輯不能置FPGA進入測試模式,并同時工作在非測試模式。

一個小的定制非易失性的即時接通可編程邏輯(PLD)能很好的適合系統DFT考慮。這樣的一種器件可提供足夠的邏輯和足夠的I/O組,使其容易調試和接口到JTAG,以便提供測試性、重新可編程性的控制功能性。這使得小的PLD成為板測試無故障的理想元件。

典型的PCB測試結構

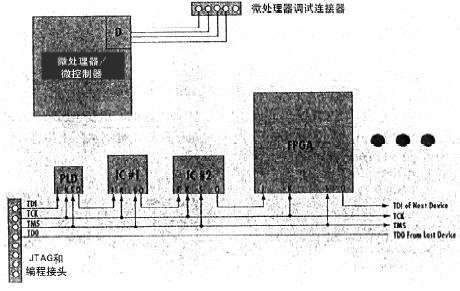

JTAG的主要用途集成在制造測試。它對開發環境有損害,它主要是處理任務而不是制造級連接性測試。圖1示出典型的PCB測試結構。

圖1示出一個微處理器基系統和連接到一個JTAG接頭的器件鏈路。這是一個簡單的框圖。

JTAG接頭和與它較連的所有器件是單串行鏈路。所有邊界掃描和系統中的測試邏輯都是做為單結構連接的。構成測試系統進入邏輯子單元,其靈活性是有限的。JTAG鏈路的長度受TCK(測試時鐘)扇出和TMS(測試模式選擇)限制。

微處理器具有一些調試控制形式,而這種控而這種控制部分或全部由JTAG管理。某些調試工具與JTAG鏈路中的其他器件不能很好的共存,這就是為什么圖1中的微處理器與JTAG鏈路中的其他器件是獨立的。

有一些方法(如TCK和TMS線上的附加分立緩沖器)可以解決這些問題。用多個JTAG接頭也可以做成幾個JTAG鏈路。此方案為了能測試整個系統,應具備驅動多個JTAT接頭的測試設備。

在這種實現方案中,到測試和編程接口的接入需要有鏈路配置的詳細知識,即采用各種硬件接頭和硬件配置的知識。只有廠家或檢修人員可以接入可測試性接口和更新任何可編程器件。

端口連接

改善系統靈活性的一種方法是增加多個接頭到板上。具有同時連接幾個JTAG接頭的JTAG測試器能夠接入每個分立的JTAG掃描鏈路。

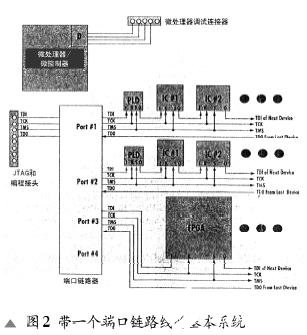

JTAG掃描鏈路可以構建進邏輯單元,而單個JTEG端口鏈路器(port Linker)示于圖2,它可以大大地簡化硬件接口,并可增加多鏈路進入邏輯單元的靈活性。

端口鏈路器是使單個物理JTAG連接器能接入幾個獨立JTAG鏈路之一鏈路的器件。端口鏈路器呈現在具有JTAG測試接入端口和1組控制寄存器的物理接頭中,控制寄存器允許獨立JTAG端口的任意互連。在物理JTAGA接頭中可見的鏈路長度,將隨鏈路PORT#1~#4的使能或斷開而增加或減少。

端口鏈路器改善了系統的JTAG能力,因為現在JTAG鏈路可以分成功能模塊。端口鏈路器也可提供每個JTAG鏈路自身的TCK和TMS線,這降低了緩沖器驅動和扇出的限制。如果需要,可編程器件也可以單獨接入另外的邏輯器件。

板設計人員為了最大功效可以選擇如何組織測試、編程和調試鏈路。

注意,在這種方案中,微處理器保持在分立鏈路,仍然對于JTAG任何邏輯都沒有接入。當設計變成產品最終到達消費者手中或處在服務中時,系統的微處理器提供重要的能力。微處理器通常與某些通信通道形式接口。這可以是Ethernet,WiFi或Bluetooth,或一些其他共同標準。假若微處理器具有到JTAG邏輯的接入,則可以利用微處理器的通信通道來執行診斷或PLD更新。

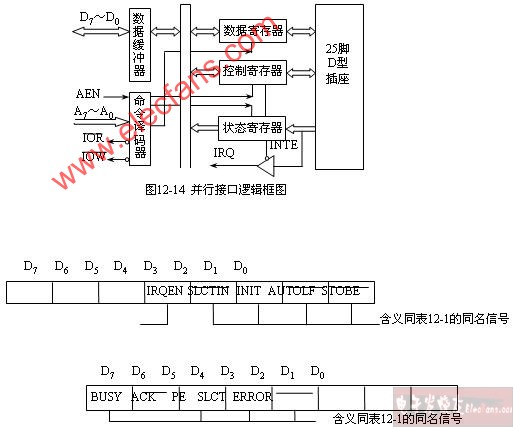

到JTAG的并行接口

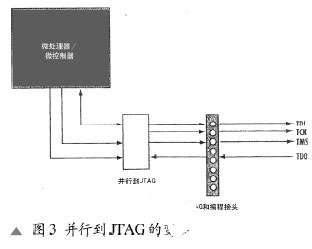

微處理接入到JTAG鏈路的一種方法是采用并行總線到JTAG串行總線接口器件。這種器件提供一組寄存器,這些寄存器與微處理之間以并存方式傳輸數據。邏輯變換并行接入為串行JTAG協議。現在微處理器具有一種與板上JTAG邏輯相互連系的手段。

圖3示出可以連接到基本JTAG鏈路的并行到JTAG的變換。此方案也必須具有斷開JTAG輸出的能力。若輸出不斷開(即處于三態),則用外接測試設備是不可能的。

此方案用一個外部變換替代控制器的端口I/O能力。設計人員必須權衡用固件控制執行,此功能比直接尋址外部變換邏輯所需的總線開銷要少。

橋接在一起

測試系統可分為兩部分:端口鏈路器和并行到JTAG變換器。假定用分立可編程邏輯器件實現這兩部分邏輯,則必須解決如何編程這些器件的問題。這些器件的每個部分都需要另外的專門JTAG接頭或復雜開關系統的某種形式來控制TMS或TCK線。

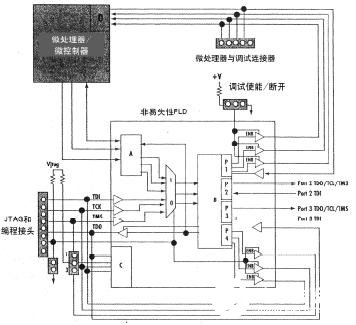

替代這些功能于兩個較小PLD器件的方法是把此邏輯置到一個較大的PLD器件中。圖4示出如何把整個設計在單個PLD中。

Lattice Semiconductor公司的Machxo PLD設計把上面所描述的元件和另外的一些性能組合在一起:

·模塊A是并行到JTAG變換模塊。

·模塊B是端口鏈接器。

·模塊C是Machxo PLD專門的JTAG端口。

此設計有幾個關鍵點。第一是用單個JTAG接頭編程PLD和連接外部制造/診斷設備。第二點是用1×3接頭控制TMS引腳的目的地到模塊C。在PCB開始裝配時,PLD是空白的,而且必須編程,在1~2引腳之間短路連接允許JTAG和編程接頭驅動PLD的TMS線。可以編程PLD板組裝之后才能進行短路。在所有其他情況下,引腳2~3之間放置跳接線。

被編程的PLD已準備好執行制造、測試、調試和維修等任務。

制造測試

制造是PLD設計的第一受益者,制造感興趣的是確認線跡沒有短路和沒有開路。用JTAG測試設備和一組可靠的JTAG鏈路是能夠確認連接是否正確。

用端口連接器把JTAG鏈路隔離為更小的子單元,可把目標定在PCB上未端的邏輯單元。測試可以執行得更快,因為可以控制邊界掃描鏈長度。也可以更快地進行初始化可編程器件。

JTAG執行測試的主要接口是JTAG和編程接頭。假若測試人員在執行測試前不需要改變板上的任何跳接線或其他設備,這就更好。JTAG和編程接頭上的備用引腳可做為使能/斷開和多路轉換器選擇。此選擇/使能引腳自動處理端口鏈路器模塊的3態port# 4并開關內部多路轉換器。多路轉換器選擇JTAG和編程接頭或并行到JTAG變換邏輯。這允許制造和測試的連接JTAG測試設備,而不需要調節PCB上的任何短接。

工程開發

用PLD控制測試過程能為工程開發提供良好的互連測試。然而,FPGA/PLD和固件設計人員現在可以開始做硬件工作。

PCB開發是一個反復的過程,工程師經常改變可編程器件的內容。工程師一般也用微處理器和調試工具。

在開發和調試過程中的早期,固件和微處理器控制可能不是完整的工作。在此期間,由于JTAG和可編程接頭接口可初始化可編程邏輯器件。

板開發早期要做的另一事情是開發微處理器控制碼。固件會有錯誤需要調試。完成調試的方法是用JTAG基調試工具。采用JTAG基調試工具引起的一個問題是這種工具要求微處理器只能有一個器件連接到微處理器的JTAG I/O。這樣要求與制造組的需要是矛盾的。然而,圖4所建議的方案早已解決了此問題。

固件工程師能夠接入調試端口,而不會干擾JTAG鏈路的邏輯。在微處理器碼調試期間獲得微處理器JTAG端口的全部控制,而能夠用JTAG調試工具。假如沒有測試工具連接到JTAG和編程接頭,則固件工程師除希望有到微處理器的鏈路外,也有在所有JTAG鏈路的接入。現在,固件工程師能夠增加板的測試能力。現在,固件工程師能夠增加板的測試能力。微處理器控制的測試程序經常是固有的或是動態下載,這取決于系統資源。測試程序可返回到制造組,允許更徹底地測試板的裝配板。

在現場JTAG所提供的全面制造和調試測試,對現場PCB提高質量和可靠性是很有價值的。

如前所述,PCB板上可有一個微處理器來執行通過/不通過測試。很多帶微處理器的系統也具有通信通道的某種形式。假若通信通道是無線或有線Internet連接,則現場工程師可以遠程初始化診斷測試。遠程初始化診斷測試與制造測試工程師所做的應具有相同的能力。甚至板不具備遠程接入,但維修人員仍從可用的編程和JTAG接頭中受益。

不管測試性能是如何接入,沒有必要為維修而接入這些性能發的系統,或需要高度可重配置分散觸發的系統。

對每個LXIA級設備,兩個觸發總線連接器是并聯接線的,以方便菊鏈分段的實現,在此場合,硬件觸發總線在每段的端點處需一個端接器,每段總線最多可連接16個LXI設備。

每條觸發總線有1個驅動器和幾個接收器,具體配置由觸發總線模式決定。A級支持兩種觸發配置:

·驅動模式:此配置將觸發事件傳輸至連接在同一條總線上的一個或多個接收器。

·線或模式:此配置支持多點至多點觸發傳輸模式。在此模式,可讓多個觸發源啟動觸發,多個接收器接收生成的觸發事件。當配置成線或模式時,與LXI觸發接收器相關聯的一個觸發器配置成基本觸發源,每個觸發源使用并聯的驅動器來驅動。

LXI觸發總線的附加功能要求有:

·8條觸發器全部路由至模塊內設置的每個觸發功能,當為每個特定功能分配觸發線時,可達到最大的靈活性。

·在每條觸發器線上同時驅動/檢測。

·為每條觸發線設置邊沿檢測或電平檢測。

A級設備為用戶和儀器供應商提供了用硬件觸發連接創建儀器分系統的能力,其典型應用是合成儀器系統,這類系統是由幾個源/測量構件組成的,由LXI觸發線提供模塊內固有的時鐘和觸發。此外,在幾個遠地放置的分系統間通信,可用消息通信方式實現。A級設備允許使用硬件或LAN觸發來啟動測量事件,為分布式測量或數據采集系統提供了更高的靈活性。

結語

定義3種不同的LXI產品等級為生產和部署產品提供更多的靈活性,既能滿足特定的要求而又不增加系統的復雜性和成本。同時,無IEEE1588PTP功能的LAN基產品有助于加速標準的推廣,促進LXI產品的研發。一旦條件成熟,不僅能迅速地將現有Ethernet基儀器更新為C級設備,還能創建更多功能齊備的A級或B級設備。

責任編輯:gt

-

pcb

+關注

關注

4324文章

23153瀏覽量

399092 -

接口

+關注

關注

33文章

8684瀏覽量

151629 -

微處理器

+關注

關注

11文章

2272瀏覽量

82634

發布評論請先 登錄

相關推薦

未來誰主沉浮:串行和并行接口SRAM對比

嵌入式微處理器和接口詳技術詳解

8255A可編程并行接口

嵌入式微處理器JTAG接口中TAP控制器的設計

計算機的并行接口,計算機的并行接口大全

SRAM存儲器的并行接口和串行接口對比

微處理器與板上JTAG邏輯相互連系的并行接口研究

微處理器與板上JTAG邏輯相互連系的并行接口研究

評論