TMS320DM6437的性能很高,但是開發的費用卻很廉價,這樣就可以面向更多的市場,主頻600 MHz,32位定點,采用達芬奇(DaVinci(TM))技術。該器件采用TI第3代超長指令集結構(VelociTI.3)的TMS320C64x+DSP內核,主頻可達600 MHz,支持8個8位或4個16位并行MAC運算,峰值處理能力高達4 800MIPS。

DSP的McBSP接口可由內部時鐘發生器或外部器件提供收/發時鐘信號(CLKR/CLKX)及收/發幀同步信號(FSR/FSX)。EN_IN、EN_OUT為DSP控制FPGA中McBSP接口的使能信號,它們均與DSP的GPIO相連。當EN_IN為高時,FPGA接收DSP的數據;當EN_OUT為高時,FPGA開始向DSP發送數據。

McBSP接口是全雙工串行接口,提供收發數據雙緩沖以處理連續的數據流,并可獨立配置收發部分,接收和發送都可使用獨立的幀信號和時鐘源。接收數據時,FPGA的數據通過McBSP傳到DSP的DRR寄存器中,觸發McBSP接收同步事件,EDMA將數據搬入DSP內存。發送數據時,當EDMA從DSP內存中將數據搬入DSP的DXR寄存器時,利用McBSP發送同步事件,將數據傳輸給FPGA。

2 軟件程序設計

傳統的C6000型DSP對McBSP和EDMA進行操作時,多使用CSL(Chip Support Library)進行編程操作,由于TMS320DM6437不支持CSL,而是改用PSP(Proeessor Support Package),所以對TMS320DM6437 McBSP接口采用PSP提供的McBSP Driver,主要用McBSP Driver提供的LLC層API進行編程。以方便實驗程序的運行。

在很多實踐中實現DSP和FPGA通信時,McBSP所需的幀同步信號以及時鐘信號均由FPGA產生,McBSP發送過來32 bit的數據,DSP內部采用EDMA方式接收數據,McBSP接收同步事件觸發EDMA傳輸。將數據放入DSP片內二級存儲器的緩沖區,等待DSP處理。為了寫入的數據不被覆蓋掉,片內二級存儲器緩沖區采用乒乓緩沖結構,就有McBSP發送同步事件觸發EDMA傳輸。

2.1 McBSP配置

2.1.1 接收數據格式配置

McBSP接收數據格式在數據結構LLC_RcvDataSetup中設置,該數據結構在McBSP Driver提供的頭文件llc_mcbsp Type.h中定義,在編譯工程文件的時候需包含此頭文件。接收數據為單幀數據,一個數據幀長度為4個字節,采用幀同步信號檢測模式,不進行壓縮,數據傳輸延遲一個比特,采用McBSP同步事件產生中斷。McBSP發送數據格式在數據結構LLC_XmitDatasetup中設置,具體參數和接收數據格式保持一致。M-cBSP幀同步和時鐘參數在數據結LLC_mcbspClkSetup中設置,該結構同樣在頭文件llc_mcbspType.h中定義。

2.1.2 啟動McBSP

首先調用MeBSP LLC層API對McBSP接口進行設置,準備接收FPGA傳輸過來的信號。先調用函數LLC_mcbspOpen,該函數在llc_mcbsp.c中定義,函數原型為LLC_mcbspOpen(LLC_McbspObj*const pMcbspObj,Uint32InstanceId,Int32*pMcbspParam,CSL_Status*pStatus),所需參數分別為用戶定義的McBSP通道對象,McBSP通道ID,用戶定義的配置參數及狀態信息,返回參數為指向該通道的句柄hMcbsp。該句話就最為API的函數。

然后設置McBSP通道0,調用函數LLC_mcbspHwSetup(LLC_McbspHandle hMcbsp,const LLC_McbspHwSetup*setup)。第1個參數即為剛才返回的指向McBSP通道0的句柄,第2個參數為一個結構體,包含了前面定義的接收和發送數據結構以及幀同步和時鐘參數結構,這樣就按照實際應用的要求完成了對McBSP0通道的設置。

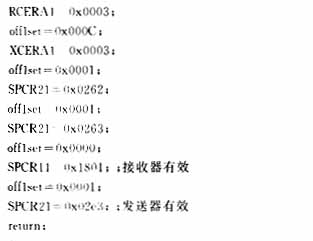

最后利用函數LLC_mcbspHwControl使能McBSP接收和發送功能。函數原型為LLC_mcbspHwControl(LLC_McbspHandle hMcbsp,LLC_Mcbsp ControlCmd cmd,const void*arg)。第1個參數為指向McBSP通道0的句柄,第2個參數為硬件控制命令,第3個為對特定命令的補充說明。開啟McBSP接收發送功能時,硬件控制命令為LLC_MCBSP_CMD_RESET_CONTROL,使能發送功能時,命令補充說明為LLC_MCBSP_CTIRL_RX_ENABLE,使能接收功能時,命令補充說LLC_MCBSP_CTRL_TX_ENABLE。

2.2 EDMA配置

2.2.1 EDMA配置原理

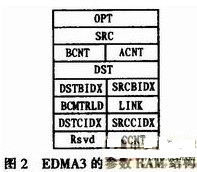

EDMA中傳輸的數據種類有3種:ARRAY,BLOCK,FRAME,分別對應3種不同類型的傳輸。首先是一維傳輸,即每一個EDMA事件觸發的傳輸只傳輸一個ARRAY,該ARRAY所包含的字節數由參數RAM里的參數ACNT決定。然后是二維傳輸,每一個EDMA事件觸發傳輸一個FRAME,每個FRAME里包含的ARRAY數由參數BCNT決定。就像這樣在類推先去,三維傳輸即每次傳輸一個BLOCK,每個BLOCK里包含的FRAME數由參數CCNT決定。這樣的數據就更加有嚴密性。

一個參數RAM的長度為32個字節。首先是32 bit的可選參數OPT,對于可選參數,通過對各個位置0或1設置事件優先級,數據單元大小,源地址/目的地址變更模式,傳輸結束代碼,是否使能傳輸參數鏈接(LINK)功能,同步傳輸方式等。SRC和DST為EDMA傳輸所需的源地址和目的地址。SRCBIDX和DSTBIDX用于二維傳輸中,表示一個ARRAY的開始到下個ARRAY的開始所跨越的字節數。SRCCIDX和DSTCIDX用于三維傳輸中,一個FRAME的開始到下個FRAME的開始所跨越的字節數。

在有些日常生活中采用的雙緩沖結構,即在DSP緩沖區內開辟2塊緩沖用于并行處理FPGA通過McBSP傳過來的數據。當EDMA往PingBuffer里傳輸數據時,CPU即可處理PongBuffer里的數據,當工作完成后,彼此又交換緩沖區,EDMA往PongBuffer里寫數據,CPU處理PingBuffer里的數據。為了實現雙緩沖結構,采用了EDMA提供的LINK功能,即將不同的EDMA傳輸參數RAM鏈接起來,組成一個傳輸鏈,在傳輸鏈中,一個傳輸的結束會導致自動從參數RAM中裝載下一個傳輸需要的事件參數。在具體程序中,只需將Ping通道的參數RAM LINK到Pong通道,同時將Pong通道的參數RAMLINK到Ping通道即可。

2.2.2 EDMA接收數據配置實現

在使用EDMA3 Driver之前必須首先對其進行初始化。EDMA3 LLD提供了2個API進行相關工作。EDMA3_DRV_create和EDMA3_DBV_open。前者用于創建一個EDMA3 Driver對象,后者用于開啟對應的EDMA3 Driver通道。

創建并開啟EDMA3 Driver通道后,即可為此通道分配資源以及初始化其配置。首先調用EDMA3_DRV_requestChannel請求分配一個DMA通道,隨后對該通道的參數RAM進行配置,以滿足傳輸需要。EDMA3_DRV_setSrcParams用于設置該EDMA通道接收數據源地址為McBSPO的DRR寄存器,地址為0x01D00000,地址計數模式為遞增模式。EDMA3_DRV_setDestParams設置該EDMA通道接收數據目的地址為DSP片內存儲區PingBuf-fer首地址,確保第一次傳輸數據是到PingBuffer,地址計數模式同樣為遞增模式。EDMA3_DRV_setSrcIndex用于配置源地址計數索引值,由于源地址為McBSPO的DRR寄存器,固定不變,所以srcBidx=0,srcCidx=0。接著調用EDMA3_DRV_setDestIndex配置目的地址計數索引值,由于接收數據為32 bits,所以sreBidx=srcCidx=4,這是因為DSP內的最小計數單元為一個字節,8bit。EDMA3_DRV_setTransferPamms配置剩余的參數RAM傳輸參數,包括設置ACNT=4,BCNT=2 048,CCNT=1,采用一維傳輸A-SYNC。

接下來是Ping/Pong傳輸的程序實現。需再調用EDMA3_DRV_requestChannel兩次,替Ping/Pong各自分配一個通道,于是,一共有3個通道,對應3個參數RAM。Ping通道的參數RAM與主通道的參數RAM完全一致,Pong通道的參數RAM與主通道相比,只需將Pong通道接收數據目的地址改為PongBuffer首地址。隨后調用EDMA3_DRV_linkChannel 3次,分別將主通道和Ping通道LINK,Ping通道和Pong通道相互LINK。

2.2.3 EDMA中斷實現

TMS320DM6437中,EDMA的128個通道只產生一種中斷,當一個通道傳輸完成后,IPR(Interrupt Pending Register)寄存器里的相應位會被置1,EDMA中斷處理器通過查詢IPR寄存器確定是哪個通道完成了傳輸,并調用相應的中斷服務程序。

EDMA LLD中中斷的設置通過調用EDMA3_DRV_requestChannel實現。該函數的參數中跟中斷有關的為eventQ(與通道優先級相關),tceCb(回調函數,即通道傳輸完成后所調用的中斷服務程序)。設置eventQ=0,保證最高優先級,tceCb=edma_isr,該函數的作用是在通道傳輸完成后發送一個旗語信號給信號處理程序,通知其對收到的數據進行處理。此外,還需調用EDMA3_DRV_setOptField將參數RAMOPT參數中TCINTEN位置1,以使能EDMA中斷。隨后,利用DSP/BIOS將EDMA中斷源和DSP的可屏蔽中斷5連接起來。

3 實現結果

配置好MeBSP和EDMA后,啟動FPGA傳輸數據,DSP做好接收和發送數據的準備,實驗中,FPGA連續不斷地發送自加地數給DSP,而DSP只發送2048個32 bit的從0開始的自加數據給FPGA。該結果如圖5所示。著可以表明DSP內部的PingBuffer區和PongBuffer區能連續不斷的收到FPGA傳輸過來的數據。

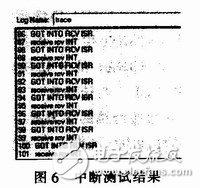

本例中設置傳完2 048個數據后EDMA發送事件觸發一次中斷,調用的中斷服務程序主要作用是發送一個旗語信號給信號處理程序,并打印出“GOT INTO RCV ISR”,進入中斷服務程序,隨后已被阻塞的信號處理程序線程收到旗語信號后,開始運行,并打印信息“receive rcv int”,中斷測試結果如圖6所示,可以看出中斷在連續不斷的被觸發!

4 結論

經過以上的測試和實驗過程,TMS320DM6437的McBSP和EDMA實現了異步串口通信,在其測試中軟硬件的實施都很正常,并且切合實際的應用和實施。可以看出該發放硬件部分容易實現,而且非常簡單放心,且采用EDMA方式,很好的節約了資源,大大的提高了工作的效率和資源的利用。

-

FPGA

+關注

關注

1629文章

21748瀏覽量

603882 -

發生器

+關注

關注

4文章

1368瀏覽量

61712 -

串口通信

+關注

關注

34文章

1626瀏覽量

55560

發布評論請先 登錄

相關推薦

McBSP EDMA例程

兩路McBSP的數據輸出存在相對位移的問題,猜測可能與EDMA event Queue有關?

關于mcbsp模塊打開FIFO功能收不到EDMA中斷的情況

使用mcbsp EDMA AD數據采集請問ad中斷后怎么啟動mcbsp?

McBSP和McASP怎么同時使用edma3?

6748的mcbsp edma3 pingpong傳輸不進入中斷

mcbsp edma3 只能采集一個數據并且進不去中斷

基于TMS320DM6437的McBSP與EDMA實現串口通

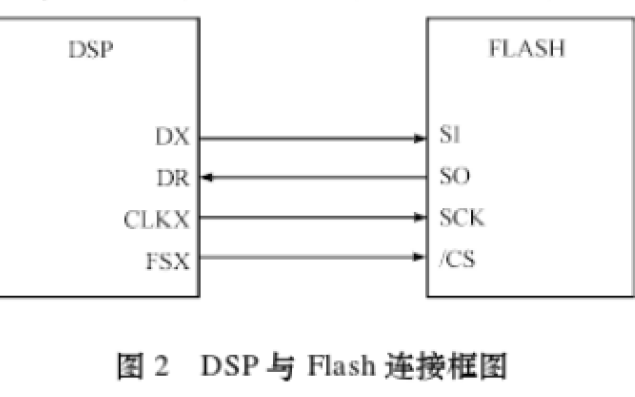

一種通過SPI接口協議實現DSP與其它設備通信的方法

McBSP在語音信號處理中的應用與實現

使用McBSP實現DSP與串行Flash的接口通訊

采用McBSP接口與EDMA配置實現異步串口通信,提高工作的效率

采用McBSP接口與EDMA配置實現異步串口通信,提高工作的效率

評論