引言

現(xiàn)代硬件程序設(shè)計(jì)規(guī)模越來越大,功能越來越復(fù)雜,當(dāng)多個(gè)應(yīng)用程序同時(shí)在一個(gè)硬件平臺(tái)上實(shí)現(xiàn)時(shí),各個(gè)程序的資源使用和數(shù)據(jù)通路可能會(huì)沖突,這增加了控制電路設(shè)計(jì)的復(fù)雜程度,給開發(fā)人員增加了工作量和開發(fā)難度。通過多重配置,可以將多個(gè)應(yīng)用程序根據(jù)需要分時(shí)加載到FPGA 中,不僅精簡了電路設(shè)計(jì),而且使系統(tǒng)更加靈活。FPGA 多重配置的特點(diǎn)可以讓特定條件下的用戶選擇片上資源不多的FPGA 去實(shí)現(xiàn)需要很多資源FPGA 才能實(shí)現(xiàn)的功能,這大大降低了開發(fā)費(fèi)用,同時(shí)提高了FPGA的利用率。

Xilinx 公司Virtex5 系列的FPGA 具有多重配置的特性,允許用戶在不掉電重啟的情況下,根據(jù)不同時(shí)刻的需求,可以從FLASH 中貯存的多個(gè)比特文件選擇加載其中的一個(gè),實(shí)現(xiàn)系統(tǒng)功能的變換。

1 總體設(shè)計(jì)

當(dāng)FPGA完成上電自動(dòng)加載初始化的比特流后,可以通過觸發(fā)FPGA內(nèi)部的多重啟動(dòng)事件使得FPGA從外部配置存儲(chǔ)器(SPI FLASH)指定的地址自動(dòng)下載一個(gè)新的比特流來重新配置。FPGA 的多重配置可以通過多種方式來實(shí)現(xiàn)。本文采用的是基于ICAP核的狀態(tài)機(jī)編碼方式。通過調(diào)用Xilinx 自帶的ICAP 核,編寫狀態(tài)機(jī)按照一定的指令流程對ICAP核進(jìn)行不斷的配置,可以控制FPGA 重新配置。這種方式可以在源代碼中加很多注釋,讓后來的開發(fā)者很清楚地明白ICAP核指令流順序,以及多重配置地址計(jì)算方法,是一種簡單實(shí)用的實(shí)現(xiàn)方法。

1.1 硬件電路

多重配置的硬件主要包括FPGA 板卡和貯存配置文件的FLASH 芯片。FPGA 選用XILINX 公司Virtex-5系列中的ML507,該產(chǎn)品針對FPGA多重配置增加了專用的內(nèi)部加載邏輯。FLASH 芯片選用XILINX 公司的SPI FLASH 芯片M25P32,該芯片存貯空間為32 Mb,存貯文件的數(shù)量與文件大小以及所使用的FPGA 芯片有關(guān)。實(shí)現(xiàn)多重配置首先要將FPGA 和外部配置存儲(chǔ)器連接為從SPI FLASH 加載配置文件的模式。配置電路硬件連接框圖如圖1所示。

在FPGA配置模式中,M2,M1,M0為0,0,1,這種配置模式對應(yīng)邊界掃描加上拉,F(xiàn)PGA在這種模式下所有的I/O只在配置期間有效。在配置完成后,不用的I/O將被浮空[5].M2,M1,M0 三個(gè)選擇開關(guān)對應(yīng)于ML507 開發(fā)板上的SW3開關(guān)中的4,5,6位,在FPGA上電之前將上述開關(guān)撥為0,0,1狀態(tài)。

1.2 軟件設(shè)計(jì)

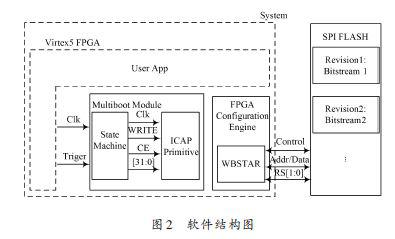

從軟件設(shè)計(jì)的角度可以將FPGA 多重配置主要分為兩個(gè)部分。第一部分是用戶自己開發(fā)的程序,這一部分包括用戶要在FPGA上邊實(shí)現(xiàn)的功能,同時(shí)也包括為重載模塊提供時(shí)鐘信號(hào),以及觸發(fā)信號(hào),本文觸發(fā)信號(hào)是通過用戶程序編寫串口通信協(xié)議棧來接收PC端傳輸?shù)臄?shù)字作為觸發(fā)信號(hào)。第二部分是FPGA 重載配置模塊。FPGA多重配置首先要調(diào)用ICAP核,當(dāng)滿足觸發(fā)條件后,采用狀態(tài)機(jī)編碼的方式對ICAP 核進(jìn)行賦值配置。FPGA多重配置的軟件結(jié)構(gòu)圖如圖2所示。

FPGA多重配置的軟件結(jié)構(gòu)圖如圖2所示。

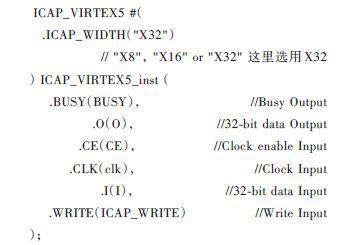

重載模塊首先要調(diào)用ICAP核。ICAP原語在Xilinx的編譯軟件ISE 中調(diào)用,調(diào)用路徑為Edit → LanguageTemplates,VHDL/Verilog → Device Primitive Instantia-tion→Virtex5FPGA → Config/BSCAN Components→ In-ternal Config Access Por(t ICAP_VIRTEX5)。

ICAP_VIRTEX5調(diào)用接口如下:

ICAP 核支持X8,X16,X32 三種數(shù)據(jù)帶寬模式。在整個(gè)FPGA 重配置的過程中并沒有用到ICAP核的輸出,因此在重載模塊的狀態(tài)機(jī)控制程序中不關(guān)注BUSY,O 信號(hào)的值,可以不對它們賦值。用戶程序在使用接口時(shí)只需對CE,CLK,I,WRITE4個(gè)信號(hào)不斷賦值來發(fā)送命令。

在調(diào)用了ICAP核接口之后,通過Verilog編碼的方式實(shí)現(xiàn)狀態(tài)機(jī)。通過狀態(tài)機(jī)發(fā)送IPROG指令給ICAP 核,ICAP 核在接收到這些指令后會(huì)根據(jù)指定的地址自動(dòng)加載配置文件。

IPROG 指令的作用是對FPGA 芯片進(jìn)行復(fù)位操作,該復(fù)位操作對FPGA 內(nèi)部的應(yīng)用程序進(jìn)行復(fù)位,復(fù)位過程中除專用配置管腳和JTAG 管腳,其他輸入/輸出管腳均為高阻態(tài)。完成復(fù)位操作后,將默認(rèn)的加載地址用熱啟動(dòng)地址寄存器(Warm Boot Start Address,WB-STAR)中的新地址替換。

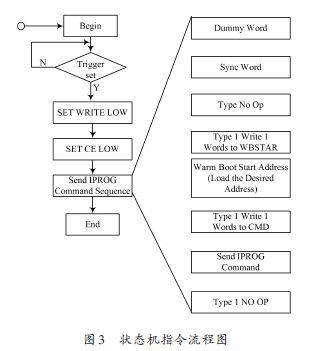

在發(fā)送IPROG 指令之前,需要對ICAP核進(jìn)行預(yù)配置。重載控制模塊在收到觸發(fā)信號(hào)后,第一個(gè)時(shí)鐘周期將ICAP 核的WRITE 信號(hào)和CE 信號(hào)置高,第二個(gè)周期將WRITE 信號(hào)置底,CE 信號(hào)置高,第三個(gè)周期將WRITE信號(hào)置底,CE信號(hào)也置底。接著在下面的8 個(gè)時(shí)鐘周期里,將指令隊(duì)列中的控制命令逐個(gè)發(fā)出。狀態(tài)機(jī)指令流程如圖3所示。

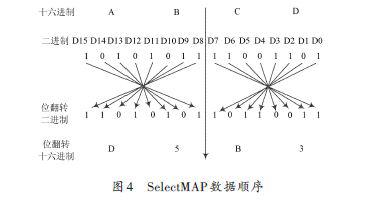

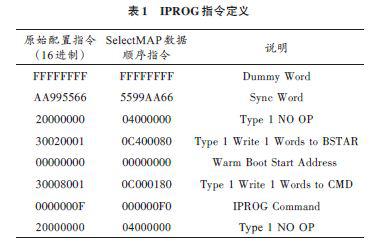

在狀態(tài)機(jī)發(fā)送IPROG 指令的過程中,為了保證ICAP 核接收到正確的指令,每一個(gè)發(fā)送出去的命令和數(shù)據(jù)必須遵循SelectMAP數(shù)據(jù)順序。SelectMAP數(shù)據(jù)順序是將每個(gè)指令都按字節(jié)劃分,劃分后每個(gè)字節(jié)的數(shù)據(jù)都按比特位翻轉(zhuǎn)。如果為“X32”模式,則劃分為4個(gè)字節(jié),每個(gè)字節(jié)進(jìn)行位翻轉(zhuǎn)。圖4 以“X16”為例說明Se-lectMAP數(shù)據(jù)順序。

當(dāng)狀態(tài)機(jī)從用戶程序接收到一個(gè)觸發(fā)條件后,會(huì)發(fā)送一系列如圖3所示的IPROG 命令。Verilog編碼實(shí)現(xiàn)狀態(tài)機(jī)的過程中,必須按照圖3給出的指令順序發(fā)送這些IPROG命令,否則無法正確的與ICAP核通信。同時(shí)這些指令都具有自己特殊的定義而且必須服從Select-MAP 數(shù)據(jù)順序,否則無法通信。IPROG 指令的具體定義及說明如表1所示。

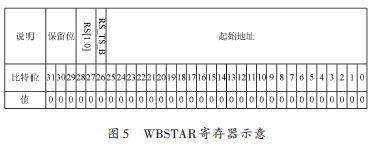

在上述配置指令過程中,第五步Warm Boot StartAddress Register(WBSTAR)指定了滿足觸發(fā)條件的比特流在SPI FLASH中的起始地址,WBSTAR被賦值的地址必須和即將配置的bit流在SPI FLASH中的物理位置相同,否則FPGA就無法從外部讀取bit流。WBSTAR被賦值的數(shù)值都是提前根據(jù)程序的要求計(jì)算好的。計(jì)算WBSTAR值的時(shí)候需要了解WBSTAR寄存器每一位的具體含義,如圖5所示。

WBSTAR寄存器共31位,高三位是保留位,RS[1:0]

兩位指定了可以多重配置的bit流的個(gè)數(shù)。RS_TS_B是RS[1:0]的使能信號(hào):0 表示Disabled,1 表示Enabled.

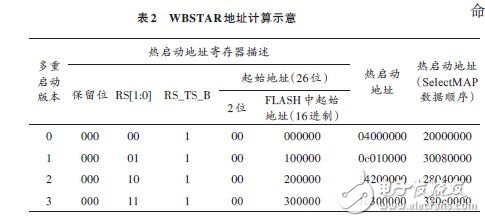

START_ADDR表示要回讀的比特流在外部配置存儲(chǔ)器的起始地址。狀態(tài)機(jī)在對WBSTAR 進(jìn)行賦值時(shí),要根據(jù)自己選擇的bit流個(gè)數(shù)以及對應(yīng)各個(gè)bit流在外部配置存儲(chǔ)器貯存的地址自行計(jì)算WBSTAR地址。這里以4個(gè)bit流為例說明WBSTAR地址的計(jì)算方法,如表2所示。狀態(tài)機(jī)使用的地址是服從SelectMAP數(shù)據(jù)順序的地址。FPGA 專用配置邏輯在收到IPROG 指令后,開始執(zhí)行內(nèi)部復(fù)位操作(JATG 管角和重載控制部分不進(jìn)行復(fù)位操作),擦除板卡上原有的程序,從FLASH 芯片中WBSTAR 所指向的起始地址開始讀取新配置文件完成FPGA的重配置。

2 多重配置的實(shí)現(xiàn)

Xilinx系列的FPGA 需要將后綴名為mcs的內(nèi)存鏡像文件固化到外部配置存儲(chǔ)器中,F(xiàn)PGA上電后才能自動(dòng)加載配置文件。一般的mcs文件只包含一個(gè)bit流文件,多重啟動(dòng)的固化文件(。mcs)包含多bit流文件。在將多個(gè)bit流整合到mcs 文件的過程中,需要指定每個(gè)bit流的起始地址,這樣FPGA專用配置邏輯才能根據(jù)地址找到對應(yīng)的bit流。首先將用戶開發(fā)的應(yīng)用程序和重載控制模塊添加到一個(gè)工程當(dāng)中,利用ISE編譯軟件生成位流文件(。bit)。由于Virtex5 系列器件本身的特性,一般情況下生產(chǎn)的bit 流文件大約為3 300 KB,而SPIFLASH 的容量為32 Mb 即4 MB,這個(gè)容量無法滿足在一個(gè)SPI FLASH 上貯存多個(gè)bit流文件,需要對生成的bit流進(jìn)行壓縮。在用ISE 軟件生成bit流文件時(shí),當(dāng)完成了Synthesize-XST以及Implement Design后,執(zhí)行到最后一步Generate Programming File時(shí),在Process Proper-ties 中General Options 選項(xiàng)中勾選Enable BitstreamCompression.通過這個(gè)壓縮設(shè)置可以對bit 流進(jìn)行壓縮,壓縮后的bit流大約在500~600 KB 之間,可以滿足在一個(gè)容量為32 Mb的SPI FLASH上貯存多個(gè)bit流文件。其次將需要進(jìn)行重配置的多個(gè)位流文件拷貝至一個(gè)工程目錄下,有兩種方法可以將多個(gè)bit流整合為一個(gè)mcs文件。第一種方法是通過ISE 編譯軟件的命令行窗口,使用命令行命令將多個(gè)位流文件合并為一個(gè)FLASH 存貯芯片M25P32 中燒寫的內(nèi)存鏡像文件(。mcs)。第二種方法是用Impact 軟件創(chuàng)建MultibootSPI FLASH,選擇相應(yīng)的FPGA 型號(hào)和FLASH 的容量以及要包含的bit 流的個(gè)數(shù)(版本的個(gè)數(shù))。本文使用第一種方法來將多個(gè)bit 流文件形成一個(gè)內(nèi)存鏡像文件(。mcs)。使用promgen 命令的具體格式為:

promgen -spi -pmcs -oMulitBoot.mcs-s4096 -u0rev0.bit -u100000rev1.bit -u200000rev0.bit -u300000rev0.bit命令中各參數(shù)的說明如下所述。-spi:表示生成的mcs文件要固化到SPI FLASH中;-p mcs:生成文件的格式是mcs格式;-o ML507.mcs:要生成的文件名,可以根據(jù)需要修改;-s 4096:定義了外部存儲(chǔ)器的容量,4096 表示32 Mb;- u 0rev0.bit:表示名字為rev0 的比特流文件在外部存儲(chǔ)器的起始地址為0;-u 100000 rev1.bit:表示名字為rev1的比特流文件在外部貯存的起始地址為100000.在生成mcs 文件后,通過IM-PACT 軟件將mcs 文件固化到SPI FLASH 中。

FPGA 上電自動(dòng)從外部SPI FLASH 加載一個(gè)初始化的bit流,當(dāng)需要執(zhí)行新的程序時(shí),會(huì)根據(jù)觸發(fā)條件以及啟動(dòng)地址重新配置。在實(shí)驗(yàn)中,通過PC機(jī)串口終端發(fā)送指令當(dāng)做觸發(fā)條件實(shí)現(xiàn)多重配置。在實(shí)際應(yīng)用中,還可以根據(jù)具體硬件實(shí)現(xiàn),采用其他通信方式傳送控制指令來進(jìn)行觸發(fā)。

3 結(jié)語

本文通過硬件電路和軟件設(shè)計(jì)兩個(gè)方面對FPGA的多重配置方法進(jìn)行了詳細(xì)介紹,本文所介紹的多重配置方法靈活方便、易于操作、電路簡單,在工程中有很高的應(yīng)用價(jià)值,同時(shí)關(guān)于bit流壓縮的方法也值得參考。

-

FPGA

+關(guān)注

關(guān)注

1643文章

21975瀏覽量

614421 -

存儲(chǔ)器

+關(guān)注

關(guān)注

38文章

7637瀏覽量

166482 -

Xilinx

+關(guān)注

關(guān)注

73文章

2183瀏覽量

124405

發(fā)布評(píng)論請先 登錄

基于SPI FLASH的FPGA多重配置

揭秘FPGA多重配置硬件電路設(shè)計(jì)方案

中端FPGA開發(fā)板

誰有Virtex5 FPGA到TI公司64系列的EMIF設(shè)計(jì)文檔??

求xilinx virtex5例程

IDDR最大速度為virtex5 sx95t

Virtex5無法正確讀取XCF32P是為什么?

求virtex5與部分重新配置教程?

Virtex5 FPGA在ISE + Planahead上部分可重構(gòu)功能的流程和技術(shù)要點(diǎn)

FPGA多重配置硬件電路的原理及其設(shè)計(jì)方案的介紹

FPGA開發(fā)板使用和配置方式

fpga開發(fā)板是什么?fpga開發(fā)板有哪些?

【GD32F303紅楓派開發(fā)板使用手冊】第二十講 SPI-SPI NAND FLASH讀寫實(shí)驗(yàn)

評(píng)論