只有最初級的邏輯電路才使用單一的時鐘。大多數與數據傳輸相關的應用都有與生俱來的挑戰,即跨越多個時鐘域的數據移動,例如磁盤控制器、CDROM/DVD 控制器、調制解調器、網卡以及網絡處理器等。當信號從一個時鐘域傳送到另一個時鐘域時,出現在新時鐘域的信號是異步信號。

在現代 IC、ASIC 以及 FPGA 設計中,許多軟件程序可以幫助工程師建立幾百萬門的電路,但這些程序都無法解決信號同步問題。設計者需要了解可靠的設計技巧,以減少電路在跨時鐘域通信時的故障風險。

基礎

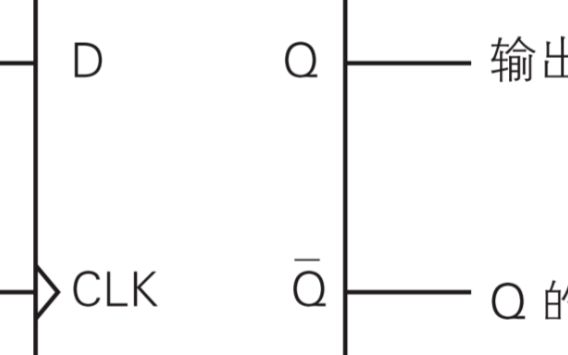

從事多時鐘設計的第一步是要理解信號穩定性問題。當一個信號跨越某個時鐘域時,對新時鐘域的電路來說它就是一個異步信號。接收該信號的電路需要對其進行同步。同步可以防止第一級存儲單元(觸發器)的亞穩態在新的時鐘域里傳播蔓延。

亞穩態是指觸發器無法在某個規定時間段內達到一個可確認的狀態。當一個觸發器進入亞穩態時,既無法預測該單元的輸出電平,也無法預測何時輸出才能穩定在某個正確的電平上。在這個穩定期間,觸發器輸出一些中間級電平,或者可能處于振蕩狀態,并且這種無用的輸出電平可以沿信號通道上的各個觸發器級聯式傳播下去。

對任何一種觸發器,在時鐘觸發沿前后的一個小時間窗口內,輸入信號必須穩定。這一時間窗口是多種因素的函數,包括觸發器設計、實現技術、運行環境以及無緩沖輸出上的負載等。輸入信號陡峭的邊沿可以將此窗口減至最小。隨著時鐘頻率的升高,會出現更多有問題的時間窗口,而隨著數據頻率的提升,這種窗口的命中概率則會增加。

FPGA 制造商和 IC 晶片廠用“MTBF”來標識合格的觸發器,并且確定它們的特性。“MTBF”(平均無故障時間)用統計方法描述了一個觸發器的亞穩態特性,即確定某個觸發器出現故障的概率。在計算 MTBF 時,制造商部分基于輸入信號改變導致觸發器不穩定期間的時間窗口長度。另外,MTBF 的計算還使用了輸入信號的頻率以及驅動觸發器的時鐘頻率。

在一個 ASIC 或 FPGA 庫中,每種觸發器都有時序要求,以幫助你確定容易出問題的窗口。“建立時間”(Setup time)是指在時鐘沿到來之前,觸發器輸入信號必須保持穩定的時間。“保持時間”(Hold time)則是指在時鐘沿之后,信號必須保持穩定的時間。這些指標通常比較保守,以應對電源電壓、工作溫度、信號質量以及制造工藝等各種可能的差異。如果一個設計滿足了這些時序要求,則觸發器出現錯誤的可能性可以忽略不計。

現代 IC 與 FPGA 設計中使用的綜合工具可以保證設計能滿足每個數字電路觸發器對建立與保持時間的要求。然而,異步信號卻給軟件提出了難題。對新的時鐘域來說,從其它時鐘域傳來的信號是異步的。大多數綜合工具在判定異步信號是否滿足觸發器時序要求時遇到了麻煩。因為它們不能確定觸發器處于非穩態的時間,所以它們也就不能確定從一個觸發器通過組合邏輯到達下一個觸發器的總延遲時間。所以,最好的辦法是使用一些電路來減輕異步信號的影響。

信號同步

信號同步的目的是防止新時鐘域中第一級觸發器的亞穩態信號對下級邏輯造成影響。簡單的同步器由兩個觸發器串聯而成,中間沒有其它組合電路。這種設計可以保證后面的觸發器獲得前一個觸發器輸出時,前一個觸發器已退出了亞穩態,并且輸出已穩定。設計中要注意將兩個觸發器放得盡可能近,以確保兩者間有最小的時滯(clock skew)。

IC 制造廠提供同步單元,幫助完成信號同步工作。這些單元通常包括一個有非常高增益的觸發器,它比普通觸發器耗電更高,也比較大。這種觸發器降低了對輸入信號建立-保持時間的要求,并且當輸入信號導致亞穩態時,它可以防止出現振蕩。另一種同步器單元包括兩個觸發器,省去了將兩個單獨觸發器靠近放置的工作,也防止設計人員誤在兩個觸發器間加入任何其它的組合邏輯。

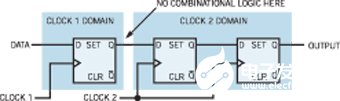

為了使同步工作能正常進行,從某個時鐘域傳來的信號應先通過原時鐘域上的一個觸發器,然后不經過兩個時鐘域間的任何組合邏輯,直接進入同步器的第一個觸發器中(圖 1)。這一要求非常重要,因為同步器的第一級觸發器對組合邏輯所產生的毛刺非常敏感。如果一個足夠長的信號毛刺正好滿足建立-保持時間的要求,則同步器的第一級觸發器會將其放行,給新時鐘域的后續邏輯送出一個虛假的信號。

圖1,在一個全同步器電路中,從某個時鐘域傳來的信號應先通過原時鐘域上的一個觸發器,然后不經過原觸發器和同步器的第一個觸發器兩個時鐘域間的任何組合邏輯,直接進入同步器的第一個觸發器中。

一個經同步后的信號在兩個時鐘沿以后就成為新時鐘域中的有效信號。信號的延遲是新時鐘域中的一到兩個時鐘周期。一種粗略的估算方法是同步器電路在新時鐘域中造成兩個時鐘周期的延遲,設計者需要考慮同步延遲將對跨時鐘域的信號時序造成的影響。

同步器有許多種設計方法,因為一種同步器不能滿足所有應用的

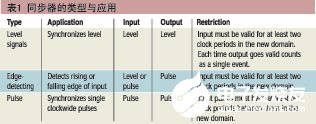

需求。同步器的類型基本上有三種:電平、邊沿檢測和脈沖(表 1)。雖然還存在著其它類型的同步器,但這三種類型的同步器可以解決設計者遇到的多數應用問題。在電平同步器中,跨時鐘域的信號在新時鐘域中要保持高電平或低電平兩個時鐘周期以上。這種電路的要求是,在再次成為有效信號前,信號需要先變成無效狀態。每一次信號有效時,接收邏輯都會把它看作一個單個事件,而不管信號的有效狀態保持了多久。這種電路是所有同步器電路的核心。

表 1

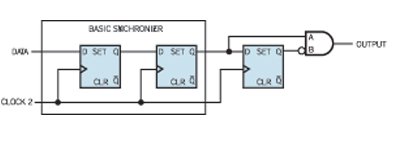

邊沿檢測同步器在電平同步器的輸出端增加了一個觸發器(圖 2)。新增觸發器的輸出經反相后和電平同步器的輸出進行與操作。這一電路會檢測同步器輸入的上升沿,產生一個與時鐘周期等寬、高電平有效的脈沖。如果將與門的兩個輸入端交換使用,就可以構成一個檢測輸入信號下降沿的同步器。將與門改為與非門可以構建一個產生低電平有效脈沖的電路。

圖2,邊沿檢測同步器在電平同步器的輸出端增加了一個觸發器。

當一個脈沖進入更快的時鐘域中時,邊沿檢測同步器可以工作得很好。這一電路會產生一個脈沖,用來指示輸入信號上升或下降沿。這種同步器有一個限制,即輸入脈沖的寬度必須大于同步時鐘周期與第一個同步觸發器所需保

持時間之和。最保險的脈沖寬度是同步器時鐘周期的兩倍。如果輸入是一個單時鐘寬度脈沖進入一個較慢的時鐘域,則這種同步器沒有作用,在這種情況下,就要采用脈沖同步器。

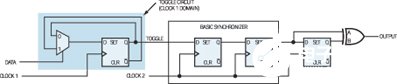

脈沖同步器的輸入信號是一個單時鐘寬度脈沖,它觸發原時鐘域中的一個翻轉電路(圖 3)。每當翻轉電路接收到一個脈沖時,它就會在高、低電平間進行轉換,然后通過電平同步器到達異或門的一個輸入端,而另一個信號經一個時鐘周期的延遲進入異或門的另一端,翻轉電路每轉換一次狀態,這個同步器的輸出端就產生一個單時鐘寬度的脈沖。

圖3,脈沖同步器的輸入信號是一個單時鐘寬度脈沖,它觸發原時鐘域中的一個翻轉電路

脈沖同步器的基本功能是從某個時鐘域取出一個單時鐘寬度脈沖,然后在新的時鐘域中建立另一個單時鐘寬度的脈沖。脈沖同步器也有一個限制,即輸入脈沖之間的最小間隔必須等于兩個同步器時鐘周期。如果輸入脈沖相互過近,則新時鐘域中的輸出脈沖也緊密相鄰,結果是輸出脈沖寬度比一個時鐘周期寬。當輸入脈沖時鐘周期大于兩個同步器時鐘周期時,這個問題更加嚴重。這種情況下,如果輸入脈沖相鄰太近,則同步器就不能檢測到每個脈沖。

握手與 FIFO

在許多應用中,跨時鐘域傳送的不只是簡單的信號,數據總線、地址總線和控制總線都會同時跨域傳輸。工程師們用一些其它的手段來處理這些情況,如握手協議和 FIFO 等。

當幾個電路不能預知相互的響應時間時,握手方法能讓數字電路間實現有效的通信。例如,仲裁總線結構可以讓一個以上的電路請求使用單個的總線,用仲裁方法來決定哪個電路可以獲得總線的訪問權,例如 PCI 或 AMBA(高級微控制器總線架構)。每個電路都發出一個請求信號,由仲裁邏輯決定誰是“贏家”。獲勝的電路會收到一個應答,表示它可以訪問總線。該電路于是中斷請求,開始使用總線。

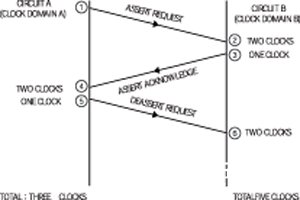

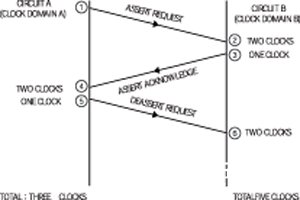

不同時鐘域電路使用的握手協議有兩種基本類型:全握手(Full-handshake)和部分握手(partial-handshake)。每種類型的握手都要用同步器,每種都各有自己的優缺點。對全握手信號,雙方電路在聲明或中止各自的握手信號前都要等待對方的響應(圖 4)。首先,電路 A 聲明它的請求信號,然后,電路 B 檢測到該請求信號有效后,聲明它的響應信號。當電路 A 檢測到響應信號有效后,中止自己的請求信號。最后,當電路 B 檢測到請求無效后,它中止自己的響應信號。除非電路 A 檢測到無效的響應信號,否則它不會再聲明新的請求信號。

圖4,對全握手信號,雙方電路在聲明或中止各自的握手信號前都要等待對方的響應。

這種類型的握手使用了電平同步器。設計人員將這種技術用在如下情況:響應電路(電路 B)需要告知請求電路(電路 A)它可以處理請求。這種握手方法要求請求電路延遲它的下一個請求,直到它檢測到響應信號無效。可以用經驗估算法判斷這個協議的時序:信號跨越一個時鐘域要花兩個時鐘周期的時間,信號在跨越多個時鐘域前被電路寄存。全部的時間序列是:A 時鐘域中最多五個周期加上 B 時鐘域最多六個周期。全握手類型很強健,因為通過檢測請求與響應信號,每個電路都清楚地知道對方的狀態。這種方式的不足之處是完成所有交互的整個過程要花費很多時鐘周期。

另一種類型是部分握手,它可以縮短這些事件的過程。使用部分握手信號時,通信雙方的電路都不等對方的響應就中止各自的信號,并繼續執行握手命令序列。部分握手類型比全握手類型在健壯性方面稍弱,因為握手信號并不指示各自電路的狀態,每一電路都必須保存狀態信息(在全握手信號里這個信息被送出去)。但是,由于無需等待其它電路的響應,完整的事件序列花費時間較少。

當使用部

分握手信號方式時,響應的電路必須以正確的時序產生它的信號。如果響應電路要

求先處理完一個請求,然后才能處理下一個請求,則響應信號的時序就很重要。電路用它的響應信號來指示它的處理任務何時完成。一種部分握手方法混合了電平與脈沖信號,而其它的方法則只使用脈沖信號。

在第一種部分握手方法中,電路 A 以有效電平聲明其請求信號,電路 B 則以一個單時鐘寬度脈沖作為響應。此時,電路 B 并不關心電路 A 何時中止它的請求信號。但為了使這種方法成立,電路 A 中止請求信號至少要有一個時鐘周期長,否則,電路 B 就不能區別前一個請求和新的請求。在這種握手方式下,電路 B 為請求信號使用一個電平同步器,電路 A 為響應信號使用一個脈沖同步器。只有當電路 B 檢測到請求信號時才發出響應脈沖。這種情況可以使電路 A 通過控制其請求信號的時序,控制同步器接收到的脈沖間隔(圖 5)。同樣可以用經驗估算法確定時序,即信號跨越一個時鐘域要花兩個時鐘周期并且在跨越時鐘域前被電路寄存。

圖5,在一種部分握手方法中,電路 A 發出它的請求信號,電路 B 則以一個單時鐘寬度脈沖作為響應。

全部的序列為 A 時鐘域最多三個周期加上 B 時鐘域最多五個周期。這種部分握手方法比全握手方法在 A、B 兩個時鐘域分別少用了兩個和一個時鐘周期。如果采用第二種部分握手方法可以再減少一些時鐘周期,此時電路 A 用一個單時鐘寬度脈沖發出它的請求,而電路 B 也用一個單時鐘寬度脈沖響應這個請求。這種情況下,兩個電路都需要保存狀態,以指示請求正待處理。

圖6,這種握手類型使用的是脈沖同步器,但如果其中一個電路時鐘比另一個電路時鐘快兩倍,則可以用邊沿檢測同步器來代替。

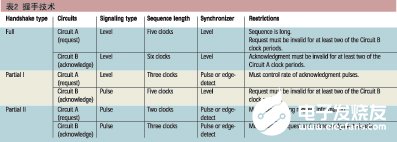

這種握手類型使用的是脈沖同步器,但如果其中一個電路時鐘比另一個電路時鐘快兩倍,則可以用邊沿檢測同步器來代替(圖 6)。完整的時序是:A 時鐘域最多兩個周期加上 B 時鐘域最多三個周期。所以這種部分握手技術與全握手方法相比,在 A 時鐘域少用三個時鐘周期,在 B 時鐘域也少用三個時鐘周期。同時,也比第一種部分握手方法分別在 A、B 時鐘域快了一個和兩個周期(表 2)。這些握手協議針對的都是跨越時鐘域的單一信號。但當幾組信號要跨越時鐘域時,設計人員就需要使用更加復雜的信號傳送方法。

表 2

數據路徑設計

在進行信號同步時有一個重要的規則,那就是不應當在設計中的多個地方對同一信號進行同步,即單個信號扇出至多個同步器。因為同步要花一到兩個時鐘周期,設計者不能確切地預測到每個信號何時跨越一個時鐘域。此外,在新時鐘域中一組經同步后的信號其時序是不定的,因為同步延遲可以是一到兩個時鐘周期,這與輸入信號到達同步器的時間有關。這種情況會在各個同步信號間形成一種“競爭狀況”。這種競爭狀況在需要跨越時鐘域傳輸的多組信號間也會發生,例如數據總線、地址總線和控制總線等。因此,不能對組中的每個信號單獨使用同步器,也不能對數據或地址總線的每一位單獨使用同步器,因為在新的時鐘域中,要求每個信號同時有效。

一種解決總線同步問題的方法是使用一個保持寄存器和握手信號。這種電路包括一個保持信號總線的寄存器,以及一個握手機制(圖 7)。握手信號指示新時鐘域的電路何時可以對總線采樣,以及源電路何時可以更換當前寄存器中保存的內容。

圖7,一種數據路徑同步器設計使用一個保持寄存器和握手信令。

在這種設計中,傳輸電路將數據(信號總線)存儲在保持寄存器,同時發出請求信號。這兩個動作可以同時發生,因為請求信號至少要花一個時鐘周期才能讓接收電路檢測到它(最小的握手-同步延遲)。當接收電路采樣到數據(信號總線)時,它發出一個響應信號。這種設計使用了全握手方法,所以要花較長時間才能完成整個傳輸。對接收電路而言,使用全握手信號的設計有較大的時間窗口用于對信號總線采樣,因而效率較低。如用部分握手方法代替全握手方法則可以加快傳輸速度。

用這種總線同步方式,你可以同步握手信號,但不能同步信號總線。信號總線來自于保持寄存器,它在接收電路采樣前一直保持穩定。注意,如果傳輸電路向接收電路提交數據太快以致來不及處理,則應用中的總線同步可能不起作用。

高級數據路徑設計

在許多情況下,數據在跨越時鐘域時需要“堆積”起來,因此使用單個保持寄存器無法完成工作。例如一種情況是某個傳輸電路猝發式發送數據,接收電路來不及采樣。另一種情況是接收電路采樣速度超出傳輸電路發送數據的速度,但采樣的數據寬度不夠。這些情況就要使用 FIFO 了。

基本上,設計者使用 FIFO 有兩個目的:速度匹配或數據寬度匹配。在速度匹配時,FIFO 較快的端口處理猝發的數據傳輸,而較慢的端口則維持恒定的數據流。但是,雖然訪問方式和速度不同,但進出 FIFO 的平均數據速率必須是相同的,否則 FIFO 就會出現上溢(overflow)或下溢(underflow)問題。與單寄存器設計相同,FIFO 將數據保存在寄存器或存儲器中,同時同步狀態信號,判斷何時可以把數據寫入 FIFO 或從 FIFO 中讀出。

在速度匹配應用中,每個端口(讀或寫)的時鐘不同。FIFO 中的寄存器使用寫端口時鐘,就像保持寄存器使用電路時鐘來改變寄存器內容一樣。信號同步發生在指針邏輯中,而且比握手信號要復雜得多。

現在指針邏輯的設計有多種方法。第一種方法是將讀、寫選通進行同步,同時在各個時鐘域使用計數器來跟蹤 FIFO 中可用的項。計數器反映出可用于讀寫的 FIFO 項目號,計數器也與相應的端口同步。讀計數器跟蹤包含有效數據的項數,而寫計數器則跟蹤可以存儲數據的項數。當對指針邏輯進行復位時,由于沒有數據可讀,讀計數器從零起始。寫計數器則從 FIFO 中項的總數開始計數,即所有項均可用來存儲數據。

讀選通信號累減讀計數器,并與寫時鐘域同步,因為它同時也累加寫計數器。寫選通信號則累減寫計數器,并與讀時鐘域同步,因為它同時也累加讀計數器。

這種設計需要單時鐘寬度脈沖以及用于讀、寫選通的脈沖同步器,因為當一個電平信號從一個時鐘域跨越到

另一個更快的時鐘域時,在較快時鐘域中它能在更多的時鐘周期中保持有效。由于只要讀或寫信號是有效的,每個計數器就會發生變化,因此較快的時鐘域就檢測到更多的讀、寫,超出較慢時鐘域實際發生的數量。脈沖同步器可以將一個時鐘域的時鐘寬度脈沖轉換為新時鐘域的時鐘寬度脈沖,每個脈沖都表示一次 FIFO 的讀或寫。

這種 FIFO 狀態技術對讀、寫狀態都不太有利。當 FIFO 中所有項均充滿時,寫端口狀態指示為滿,并在讀選通觸發后繼續指示 FIFO 滿,因為同步過程會使選通信號延遲送給寫計數器。讀端口為空時也會出現這種情況,因為同步過程會使寫選通信號延遲到達讀計數器。

這種設計的另一種考慮是及時檢測全滿/全空狀態。如果 FIFO 還有一項可用,并且有寫選通觸發,則 FIFO 必須立即置為全滿狀態。這樣才能提前一個時鐘給出全滿標志,使 FIFO 有足夠時間防止下一個數據寫入而產生溢出。對 FIFO 的讀端口也是這樣。這種情況下,如果 FIFO 里只有一個數,并且有讀選通觸發,則必須置全空狀態,以給讀電路足夠的時間防止讀空 FIFO。

這種指針邏輯限制電路在每個時鐘周期中訪問 FIFO,即使在慢速時鐘域中也是這樣。這一功能的優點在于訪問 FIFO 的電路至少有一個時鐘周期來評估 FIFO 的狀態。FIFO 可以將所有項都填滿數據,而不會出現數據被覆蓋或全空無數據可讀的情況。這種設計的另一個優點是每一端都可以讀其相應的計數器,來判斷 FIFO 中還有多少項可用。設計者可以將這種 FIFO設計用在進行多次數據讀/寫的電路中,而不會造成上溢或下溢的情況。

這種設計的不足之處是由計數器來判斷狀態,而不是直接比較讀、寫指針。對大型 FIFO 來說,這些計數器也很大。而且,由于使用脈沖同步時,來自較快時鐘域的讀、寫脈沖在較慢時鐘域的脈沖間至少必須有兩個時鐘周期,因此平均數據速率為最低時鐘頻率的一半。解決這些問題的一種方法是采用直接指針比較法。

在這種 FIFO 設計中,讀、寫指針的比較決定了 FIFO 的狀態。異步設計中的指針比較更富有挑戰性,因為每個指針位于不同的時鐘域中,對信號總線的同步要求在同步握手信號期間總線不發生改變。將這種技術用于指針同步的 FIFO 設計可能會很慢。要解決這個問題,FIFO 指針邏輯使用了格雷碼,代替指針使用的二進制碼。

格雷碼在每一次計數增減時只改變其中的一位(表 3)。你可以在格雷碼總線上使用同步器,因為每一次總線改變時只有一根信號線有變化,于是就消除了格雷碼總線各位通過不同同步器時的競爭情況。這種設計的指針為格雷碼計數器。使用二進制指針時需要將其變換成格雷碼后的同步指針,而使用變換邏輯會違反對同步信號的限制,即同步的信號在跨越時鐘域前要來自觸發器。

表 3

格雷碼計數器是一個二進制累加器,在累加器前、后各帶有一個轉換器,分別用于格雷碼轉換為二進制碼,和二進制碼轉換為格雷碼(圖 8)。格雷碼與二進制碼的轉換是一個異或運算,所以只需比一個二進制計數器多幾個邏輯電平。在格雷碼轉換成二進制碼時,使用:BN=GN;BN-1=BN+GN-1;BN-2=BN-1+GN-2 . B1=B2+G1;B0=B1+G0。而將二進制碼轉換成格雷碼時,使用:GN=BN;GN-1=BN+BN-1;GN-2=BN-1+BN-2 . G1=B2+B1;G0=B1+B0。在設計中可以采用同樣的技術來比較格雷碼指針的值,即在各個指針與二進制比較邏輯之間增加轉換器。

圖8,格雷碼計數器是一個二進制累加器,在累加器前、后各帶有一個轉換器。

用這種指針邏輯的 FIFO 很快,每個時鐘周期中電路都可以讀寫 FIFO。但是,在每個周期都訪問 FIFO 意味著 FIFO 狀態要包括“將滿”和“將空”兩種指示,這樣讀寫 FIFO 的電路才能有停止時間。“將滿”表示只能再寫入一項,“將空”則表示只有一項可讀。這種情況描述了一個要求最少的可能狀態信號的設計,以及一個需要更多指示的設計,如果在固定的最小尺寸情況下用猝發方式訪問 FIFO 的電路的話。

這種 FIFO 狀態技術會給讀、寫帶來不良狀態。當 FIFO 滿時,寫端口的狀態指示已滿,而在電路從 FIFO 中讀出一項后,該狀態仍為滿,因為同步機制使讀指針相對寫入一側的比較邏輯有個延遲。同樣,在讀出一側的空狀態指示也有這個問題,因為同步機制使寫指針相對讀出一側的比較邏輯有延遲。

如果你在設計跨不同時鐘域電路時,使用一些技術來降低通信失敗的風險,則處理跨時鐘域的信號就不再是艱巨的任務。同步機制可以防止接收跨時鐘域信號的觸發器出現亞穩態,從而避免導致不可預知的電路行為。對于在多個時鐘周期內一直保持有效的信號來說,電平同步器的效果很好。對于要轉換成新時鐘域脈沖的較慢時鐘域電平信號,要采用邊沿檢測同步器。最后,對跨時鐘

域的脈沖信號應使用脈沖同步器。還要記住,當一個信號總線跨越時鐘域時,整個總線要在同一個時鐘周期內到達新的時鐘域。不要分別同步每一個信號,而要采用一個保持寄存器和握手方式。握手用來表示寄存器中的信號何時有效,何時可以采樣。對數據總線來說,握手和一個保持寄存器很有用,但每次向新時鐘域傳送的數據字不超過一個。

責任編輯:gt

-

FPGA

+關注

關注

1630文章

21761瀏覽量

604385 -

控制器

+關注

關注

112文章

16402瀏覽量

178605 -

觸發器

+關注

關注

14文章

2000瀏覽量

61226

發布評論請先 登錄

相關推薦

FPGA電路設計的一些技巧

FPGA/CPLD 數字電路設計經驗和一些設計方法

我想學習一些接口電路設計

數字電路一些經典問答

PLD設計技巧—采用同步電路設計

硬件設計——關于電路設計的一些知識

在電路設計中采用一些技巧解決信號同步問題

在電路設計中采用一些技巧解決信號同步問題

評論