由于線路速率繼續(xù)增長(zhǎng),DDR SDRAM在網(wǎng)絡(luò)應(yīng)用中正在被廣泛地采用。不斷增加的系統(tǒng)帶寬要求正在推動(dòng)存儲(chǔ)器接口速度提高,而成本仍不斷壓低。LatticeEC FPGA系列的專門而靈活的DDR能力使設(shè)計(jì)者擁有滿足下一代存儲(chǔ)器控制器需求的低成本解決方案。

存儲(chǔ)器已廣泛地應(yīng)用于當(dāng)今的電子系統(tǒng)。由于系統(tǒng)帶寬的不斷增加,存儲(chǔ)器技術(shù)針對(duì)更高的速度和性能進(jìn)行了優(yōu)化。結(jié)果,下一代存儲(chǔ)器接口的設(shè)計(jì)變得越來(lái)越具有挑戰(zhàn)性。在諸如FPGA的可編程器件中實(shí)現(xiàn)高速、高效的存儲(chǔ)器接口對(duì)于設(shè)計(jì)者來(lái)說(shuō)一直是一個(gè)主要的挑戰(zhàn)。以往,只有少數(shù)FPGA持能可靠地與下一代高速器件接口的構(gòu)建模塊,這些FPGA通常是高端的昂貴器件。不過(guò),現(xiàn)在LatticeEC FPGA系列也提供在低成本FPGA結(jié)構(gòu)中實(shí)現(xiàn)下一代DDR2、QDR2以及RLDRAM控制器所需的構(gòu)建模塊、高速FPGA結(jié)構(gòu)、時(shí)鐘管理資源和I/O結(jié)構(gòu)。

存儲(chǔ)器應(yīng)用

存儲(chǔ)器是各種系統(tǒng)的組成部份之一,不同的應(yīng)用有不同的存儲(chǔ)器要求。對(duì)于網(wǎng)絡(luò)基礎(chǔ)設(shè)施應(yīng)用,所需的存儲(chǔ)器通常為高密度、高性能和高帶寬,并具有高可靠性;在無(wú)線應(yīng)用中,特別是手機(jī)和移動(dòng)設(shè)備,低功率存儲(chǔ)器是很重要的;而對(duì)于基站應(yīng)用,高性能很關(guān)鍵。寬帶應(yīng)用要求存儲(chǔ)器在成本和性能方面有很好的平衡;計(jì)算與消費(fèi)類應(yīng)用則需要諸如DRAM模塊、閃存卡和其它對(duì)成本很敏感的存儲(chǔ)器解決方案,同時(shí)要滿足這些應(yīng)用的性能目標(biāo)。本文主要討論在網(wǎng)絡(luò)和通信中的存儲(chǔ)器應(yīng)用。

網(wǎng)絡(luò)和通信應(yīng)用需要大的、快速存儲(chǔ)器,完成從小的地址查找到流量修整/監(jiān)控再到緩沖器管理等各種任務(wù)。用于消費(fèi)應(yīng)用的價(jià)格便宜、成熟的FMP和EDO DRAM通常不適用,因?yàn)樗捎昧溯^慢的異步方式,且需要時(shí)序精確的命令信號(hào)來(lái)初始化數(shù)據(jù)轉(zhuǎn)移。網(wǎng)絡(luò)系統(tǒng)架構(gòu)師一般轉(zhuǎn)向采用靜態(tài)RAM,解決時(shí)延問(wèn)題,但這導(dǎo)致較高的成本。通過(guò)去除讀和寫周期間的等待狀態(tài)和空閑周期,ZBT SRAM被廣泛地用于改進(jìn)存儲(chǔ)器帶寬。

最近,系統(tǒng)架構(gòu)師在網(wǎng)絡(luò)基礎(chǔ)設(shè)施應(yīng)用中轉(zhuǎn)向使用SDRAM,以便減少時(shí)延、滿足低成本要求。上述任務(wù)的每一個(gè)都伴隨一組獨(dú)特的需求。例如,低的和中等帶寬的應(yīng)用要求低時(shí)延的存儲(chǔ)器,因此ZBT SRAM是理想的。

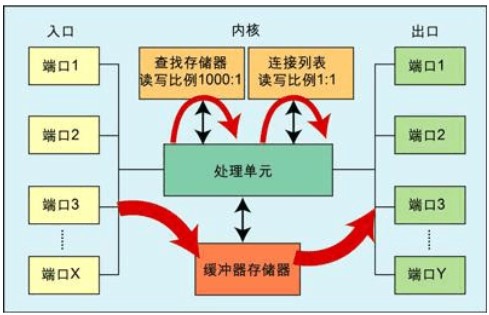

圖1:網(wǎng)絡(luò)中的存儲(chǔ)器。不同的功能需要不同的方法。

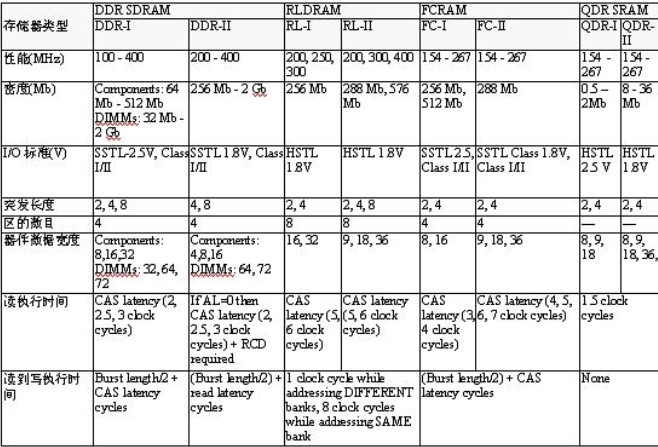

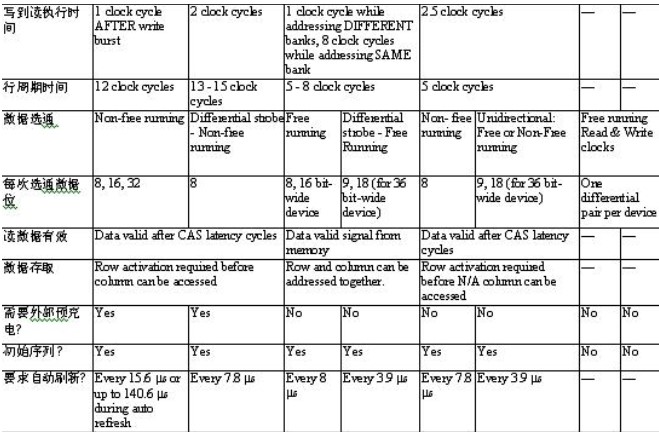

表1:為用于高速網(wǎng)絡(luò)應(yīng)用的存儲(chǔ)器綜合比較。

圖1顯示了典型的網(wǎng)絡(luò)架構(gòu)。在10Gbps,一個(gè)讀寫比為1000:1的地址查找可很容易地在DDR SRAM中得到處理。連接列表管理、流量修整、統(tǒng)計(jì)收集任務(wù)通常具有平衡的1:1讀寫比,需要較高性能的QDR SRAM。另一方面,較大的緩沖存儲(chǔ)器一般在DDR SDRAM中實(shí)現(xiàn)。作為DRAM的替代,SDRAM同步存儲(chǔ)器訪問(wèn)的處理器時(shí)鐘用于快速數(shù)據(jù)傳輸。達(dá)到快速是因?yàn)镾DRAM允許存儲(chǔ)器的一個(gè)塊被存取,而另一個(gè)塊準(zhǔn)備被存取。與DRAM不同,SDRAM采用流動(dòng)電流而不是存儲(chǔ)電荷,除去了連續(xù)刷新的需要。

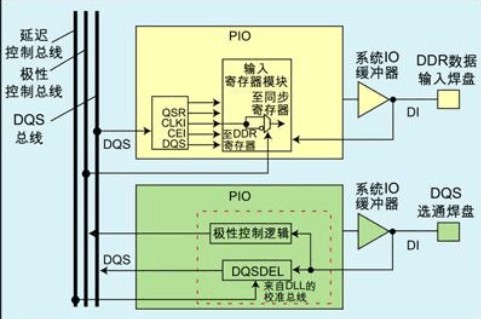

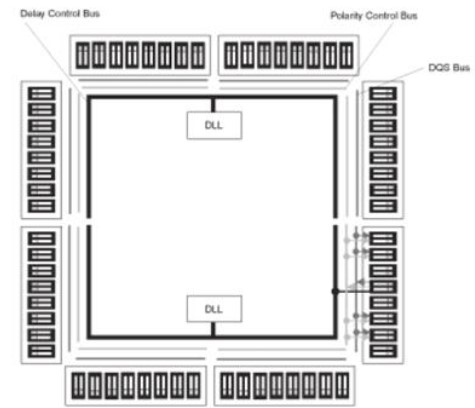

圖2:LatticeEC FPGA中的專用DQS電路。

兩個(gè)新的競(jìng)爭(zhēng)者進(jìn)入了高精度存儲(chǔ)器舞臺(tái)。快速周期隨機(jī)存取存儲(chǔ)器(FCRAM)改進(jìn)了性能,它采用了流水線操作和隱蔽的預(yù)充電技術(shù)以減少隨機(jī)存取周期時(shí)間,高度分段的存儲(chǔ)器核減少了功耗。存儲(chǔ)器核分段為較小的陣列,這樣數(shù)據(jù)可以被很快地存取并改進(jìn)執(zhí)行時(shí)間。這些特征使得FCRAM被理想地用作緩沖存儲(chǔ)器,用于諸如交換、路由和網(wǎng)絡(luò)服務(wù)器等的高速網(wǎng)絡(luò)應(yīng)用中。時(shí)延減少的DRAM(RLDRAM)提供SRAM類型的接口以及非多路復(fù)用的尋址。RLDRAM II技術(shù)提供最小時(shí)延并可減少行周期時(shí)間,這些特征很適用于要求關(guān)鍵響應(yīng)時(shí)間和快速隨機(jī)存取的應(yīng)用,例如下一代10Gbps以及更加高速的網(wǎng)絡(luò)應(yīng)用。

存儲(chǔ)器控制器的挑戰(zhàn)

目前存儲(chǔ)器接口經(jīng)常要求時(shí)鐘速度超過(guò)200MHz以滿足線卡和交換卡的吞吐量要求,這是FPGA架構(gòu)的主要挑戰(zhàn)。PLL是基本的允許控制時(shí)鐘數(shù)據(jù)關(guān)系的部件。

下一代存儲(chǔ)器控制器工作在HSTL或SSTL電壓。低電壓電平的擺動(dòng)是需要的,以便??持存儲(chǔ)器和存儲(chǔ)器控制器的輸入輸出的高速數(shù)據(jù)操作。對(duì)于高速SRAM存儲(chǔ)器來(lái)說(shuō),HSTL是實(shí)際的I/O標(biāo)準(zhǔn),而對(duì)于高速DDR SRAM存儲(chǔ)器,SSTL是實(shí)際的I/O標(biāo)準(zhǔn)。

高速差分I/O緩沖器和專用電路的組合能夠在高帶寬下進(jìn)行無(wú)縫讀寫操作,傳統(tǒng)上這屬于高級(jí)FPGA的領(lǐng)域。LatticeEC FPGA改變了那個(gè)慣例,通過(guò)低成本FPGA架構(gòu)實(shí)現(xiàn)了高帶寬存儲(chǔ)器控制器。

表2:為用于高速網(wǎng)絡(luò)應(yīng)用的存儲(chǔ)器綜合比較。

DDR存儲(chǔ)器控制器的支持

實(shí)現(xiàn)高性能的DDR存儲(chǔ)器需要在輸入端的讀操作和在輸出端的寫操作有專用的DDR寄存器結(jié)構(gòu),LatticeEC提供這個(gè)能力。除這些寄存器外,EC器件有兩個(gè)單元簡(jiǎn)化用于讀操作的輸入結(jié)構(gòu)設(shè)計(jì),這兩個(gè)單元是DQS延時(shí)塊和極性控制邏輯。這兩個(gè)塊對(duì)于實(shí)現(xiàn)可靠的高速DDR SDRAM控制器十分關(guān)鍵。由于DQS邏輯的復(fù)雜性,用FPGA實(shí)現(xiàn)高速存儲(chǔ)器控制器時(shí),設(shè)計(jì)者會(huì)遇到問(wèn)題。LatticeEC為設(shè)計(jì)者提供這些專用塊,能夠緩解這個(gè)問(wèn)題。

DLL校準(zhǔn)DQS延時(shí)塊

源同步接口通常要求調(diào)整輸入時(shí)鐘,以便用輸入寄存器正確捕獲數(shù)據(jù)。對(duì)大多數(shù)接口而言,PLL被用于這種調(diào)整。然而對(duì)于DDR存儲(chǔ)器,稱為DQS的時(shí)鐘是受約束的,因此這種方法不可行。在DDR存儲(chǔ)器接口,DQS與主時(shí)鐘的關(guān)系會(huì)有變化,這是由于PCB上走線的長(zhǎng)度和使用的存儲(chǔ)器所引起的。

圖3:DLL校準(zhǔn)總線和DQS/DQS轉(zhuǎn)移分布。

如圖2所示,Lattice DQS電路包括一個(gè)自動(dòng)時(shí)鐘轉(zhuǎn)移電路,用以簡(jiǎn)化存儲(chǔ)器接口設(shè)計(jì)和保證穩(wěn)健的操作。此外,DQS延時(shí)塊還提供用于DDR存儲(chǔ)器接口所需的時(shí)鐘對(duì)列。來(lái)自焊盤的DQS信號(hào)通過(guò)DQS延時(shí)單元送入專用的布線資源。DQS信號(hào)也送入極性控制邏輯,用于控制輸入寄存器塊中連至同步寄存器的時(shí)鐘極性。

專用DQS延時(shí)塊的溫度、電壓和工藝變化由一組校準(zhǔn)信號(hào)(6位寬的總線)進(jìn)行補(bǔ)償,它們來(lái)自器件兩側(cè)的兩個(gè)DLL。每個(gè)DLL補(bǔ)償器件一半的DQS延時(shí),如圖3所示。DLL用系統(tǒng)時(shí)鐘和專用反饋環(huán)來(lái)補(bǔ)償。這是一個(gè)重要的結(jié)構(gòu)特征,因?yàn)檫@個(gè)器件不會(huì)受到通常其它FPGA嚴(yán)格的I/O布局要求的牽制。

極性控制邏輯

對(duì)于典型的DDR存儲(chǔ)器設(shè)計(jì),延時(shí)DQS選通脈沖和內(nèi)部系統(tǒng)時(shí)鐘(在讀周期)之間的相位關(guān)系是未知的。Lattice-EC器件含有專用電路在這些域間傳遞數(shù)據(jù)。為了防止建立和保持時(shí)間發(fā)生變化,即DQS延時(shí)和系統(tǒng)時(shí)鐘間的域傳遞,它使用了一個(gè)時(shí)鐘極性選擇器,這改變了鎖存在輸入寄存器塊中同步寄存器中的數(shù)據(jù)的邊沿。這需要測(cè)定在每個(gè)讀周期的起始時(shí)刻有正確的時(shí)鐘極性。DDR存儲(chǔ)器讀操作前, DQS處于三態(tài)(由端接上拉)。起始時(shí)刻DDR存儲(chǔ)器驅(qū)動(dòng)DQS為低電平,一個(gè)專用電路用于檢測(cè)這個(gè)傳遞,這個(gè)信號(hào)用來(lái)控制至同步寄存器的時(shí)鐘極性。

-

FPGA

+關(guān)注

關(guān)注

1629文章

21735瀏覽量

603121 -

存儲(chǔ)器

+關(guān)注

關(guān)注

38文章

7487瀏覽量

163799 -

服務(wù)器

+關(guān)注

關(guān)注

12文章

9139瀏覽量

85377

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

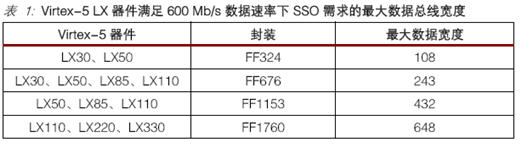

基于Xilinx 和FPGA的DDR2 SDRAM存儲(chǔ)器接口

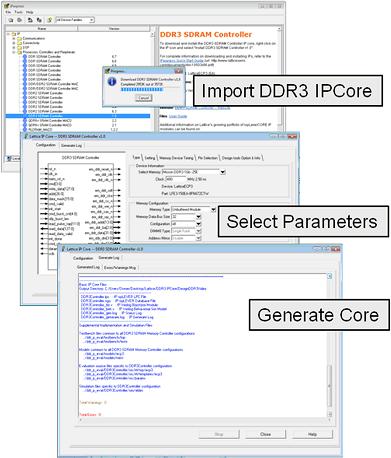

DDR3存儲(chǔ)器接口控制器IP助力數(shù)據(jù)處理應(yīng)用

基于DDR3存儲(chǔ)器的數(shù)據(jù)處理應(yīng)用

如何用中檔FPGA實(shí)現(xiàn)高速DDR3存儲(chǔ)器控制器?

如何去實(shí)現(xiàn)高速DDR3存儲(chǔ)器控制器?

利用Virtex-5 FPGA迎接存儲(chǔ)器接口設(shè)計(jì)挑戰(zhàn)

DDR3存儲(chǔ)器接口控制器IP核在視頻數(shù)據(jù)處理中的應(yīng)用

基于FPGA的DDR2 SDRAM存儲(chǔ)器用戶接口設(shè)計(jì)

基于Spartan3_FPGA的DDR2_SDRAM存儲(chǔ)器接口設(shè)計(jì)

Xilinx DDR2存儲(chǔ)器接口調(diào)試代碼

基于FPGA的DDR3多端口讀寫存儲(chǔ)管理的設(shè)計(jì)與實(shí)現(xiàn)

利用FPGA系列的DDR能力解決DDR存儲(chǔ)器的接口設(shè)計(jì)

利用FPGA系列的DDR能力解決DDR存儲(chǔ)器的接口設(shè)計(jì)

評(píng)論