引言

如果告訴便攜式電子設(shè)計(jì)人員有一種低功耗數(shù)字器件能使他們利用軟件程序來重新配置硬件工作,他們中的十個(gè)會(huì)有九個(gè)認(rèn)為這是某種微控制器。這是可以理解的。豐富的特性和封裝、大量的軟件開發(fā)工具,以及龐大的應(yīng)用代碼庫,無處不在的微控制器幾乎能夠用在所有便攜式應(yīng)用中。然而,隨著低功耗CPLD的出現(xiàn),設(shè)計(jì)人員有了新的選擇來實(shí)現(xiàn)以前由微控制器完成的功能。

本白皮書討論什么時(shí)候適合采用CPLD來替代微控制器,什么時(shí)候可以采用CPLD作為微控制器的輔助器件。根據(jù)其功能和復(fù)雜程度,本白皮書中的例子可以分成三類。第一類是I/O管理,主要針對(duì)引腳級(jí)應(yīng)用。第二類是端口管理,重點(diǎn)是器件之間的各種接口。第三類是系統(tǒng)管理,面向使用引腳或者端口來控制系統(tǒng)級(jí)功能的應(yīng)用。

第一次接觸可編程邏輯的設(shè)計(jì)人員會(huì)發(fā)現(xiàn)CPLD設(shè)計(jì)在很多方面和傳統(tǒng)的微控制器設(shè)計(jì)類似。下面簡單說明CPLD設(shè)計(jì)流程:

1 利用軟件開發(fā)工具,采用Verilog或者VHDL等高級(jí)語言編寫設(shè)計(jì)。

2 對(duì)設(shè)計(jì)進(jìn)行仿真,以驗(yàn)證功能是否正確。

3 驗(yàn)證是否滿足資源占用和時(shí)序通路等物理要求,將設(shè)計(jì)“適配”到CPLD中。

4 對(duì)設(shè)計(jì)進(jìn)行仿真,以驗(yàn)證時(shí)序是否正確。

5 設(shè)計(jì)被編程至物理器件中。

一個(gè)主要不同是復(fù)雜的在電路仿真器功能,以驗(yàn)證微控制器。然而,一旦理解了可編程技術(shù)的細(xì)微差別后,微控制器設(shè)計(jì)人員便能夠很好地進(jìn)行CPLD設(shè)計(jì)。

CPLD替代微控制器的實(shí)例

以下部分介紹了CPLD能夠有效替代微控制器的某些應(yīng)用。

I/O管理

當(dāng)考慮是使用CPLD還是微控制器來進(jìn)行I/O管理時(shí),所需要的I/O數(shù)量和類型是兩個(gè)關(guān)鍵因素。微控制器的好處是體積小而且價(jià)格低,當(dāng)然還有大量的小型低成本微控制器供設(shè)計(jì)人員選擇。然而,如果某一應(yīng)用需要大量的通用I/O,那么CPLD在成本上通常可以和微控制器相競爭。小型低成本微控制器一般受限于串口,它最多有幾個(gè)通用I/O引腳。

設(shè)計(jì)人員發(fā)現(xiàn),I/O數(shù)量較多的微控制器體積也不小,而且價(jià)格也昂貴。而另一方面,CPLD趨于有較多的I/O;小外形封裝CPLD有50多個(gè)I/O是比較常見的。例如,5mm x 5mm封裝的Altera? MAX? IIZ EPM240Z CPLD有80個(gè)I/O。除了I/O數(shù)量優(yōu)勢以外,一般情況下,CPLD要比微控制器更加靈活。除了某些例外,大部分CPLD I/O都能夠用于任意目的。

可編程電平轉(zhuǎn)換

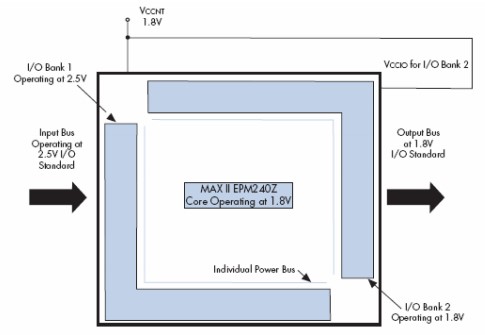

很多產(chǎn)品都需要使用電壓不同的各種邏輯器件。為支持多電壓應(yīng)用,設(shè)計(jì)人員要經(jīng)常連接不同電平的器件。而采用微控制器幾乎不可能實(shí)現(xiàn)這一切,因?yàn)槲⒖刂破鞯腎/O資源數(shù)量有限,一般采用一個(gè)電壓源工作。而CPLD有大量的I/O,并分成多個(gè)塊。相應(yīng)的為每個(gè)I/O塊分配一個(gè)電壓源。因此,開發(fā)電平轉(zhuǎn)換器只需要將一個(gè)塊中一種電壓的所有I/O分在一起,將相關(guān)的電壓參考連接到這些I/O所需的電源上(圖1)。使用CPLD不但能夠很好地完成電平轉(zhuǎn)換,它更大的優(yōu)勢在于和電平轉(zhuǎn)換相結(jié)合的可編程功能。例如,如果某一應(yīng)用需要LCD顯示器,但主處理器并不支持這種顯示器,而且電平不同,那么可以采用CPLD來實(shí)現(xiàn)主處理器和LCD顯示器之間的電平轉(zhuǎn)換時(shí)序控制功能。

圖1. 使用MAX IIZ CPLD來進(jìn)行電平轉(zhuǎn)換

脈沖寬度調(diào)制

一般而言,設(shè)計(jì)人員針對(duì)某一功能選擇一款微控制器,例如脈沖寬度調(diào)制(PWM),這些功能也可以采用CPLD來實(shí)現(xiàn)。在PWM中,方波的時(shí)間周期不變,而信號(hào)保持高電平的時(shí)間在變化或者受到調(diào)制。這樣,信號(hào)的占空比(tON)是變化的。PWM為數(shù)字系統(tǒng)中的模擬電路控制提供了有效的方法。便攜式應(yīng)用中常用的一種方法是利用PWM來調(diào)節(jié)LED的亮度。

CPLD并沒有專用PWM電路,但是實(shí)現(xiàn)PWM輸出并不難。例如,MAX IIZ CPLD的內(nèi)部振蕩器可以用作頻率源,計(jì)數(shù)器可以用于調(diào)制所產(chǎn)生的頻率。

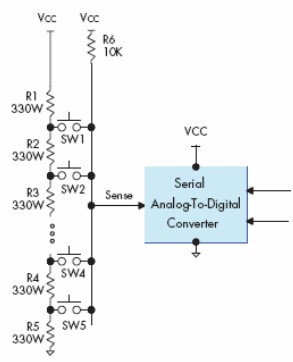

設(shè)計(jì)人員經(jīng)常選擇微控制器來實(shí)現(xiàn)模數(shù)轉(zhuǎn)換器(ADC)。然而,在某些情況下,例如鍵盤解碼,可能不需要ADC。

圖2所示為一個(gè)基本開關(guān)陣列和ADC。在VCC和GND之間串聯(lián)了一組電阻,每個(gè)電阻抽頭和公共極上連接了一個(gè)開關(guān)。如果開關(guān)接通,電路產(chǎn)生一個(gè)和電阻堆中開關(guān)位置成比例的電壓信號(hào)。要在數(shù)字系統(tǒng)中使用,模擬信號(hào)必須轉(zhuǎn)換為數(shù)字值,通常選用含有內(nèi)置ADC的微控制器來實(shí)現(xiàn)這一功能。

圖2.模擬鍵盤陣列

然而,CPLD也是一種選擇。加入一個(gè)簡單的低成本外部電容后,MAX IIZ CPLD可以利用其內(nèi)部振蕩器、施密特觸發(fā)器I/O以及高密度算法可編程邏輯架構(gòu)來完成模數(shù)轉(zhuǎn)換(1)。

上電排序

MAX IIZ器件針對(duì)大量的系統(tǒng)管理功能進(jìn)行了優(yōu)化,例如多電壓系統(tǒng)上電和系統(tǒng)復(fù)位上電排序功能,以及片選信號(hào)生成等。這兩類應(yīng)用一般集成在一個(gè)非易失、瞬時(shí)接通器件中。多電壓系統(tǒng)上電排序功能需要采用瞬時(shí)接通器件,該器件能馬上管理PCB上其他器件的上電順序。因此,相對(duì)于在毫秒量級(jí)上電的微控制器,能夠在幾微秒內(nèi)上電的CPLD是上電排序功能更好的選擇。

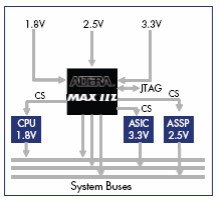

圖3所示為典型的MAX IIZ器件上電排序應(yīng)用。隨著電路板密度以及電路板電源層數(shù)的增加,上電排序變得越來越復(fù)雜。MAX IIZ CPLD能夠輕松管理系統(tǒng)復(fù)雜程度不同的上電排序。多電源供電支持不同的器件,需要采用控制邏輯來管理每一器件的上電順序。為確保在上電期間不會(huì)出現(xiàn)對(duì)總線信號(hào)的意外驅(qū)動(dòng),也需要MAX IIZ器件來控制關(guān)鍵總線信號(hào),直至上電完成。JTAG端口監(jiān)視上電順序,存儲(chǔ)上電時(shí)的錯(cuò)誤和信息。它還可以用于在調(diào)試階段設(shè)置上電排序斷點(diǎn)。

圖3. 利用CPLD實(shí)現(xiàn)上電排序

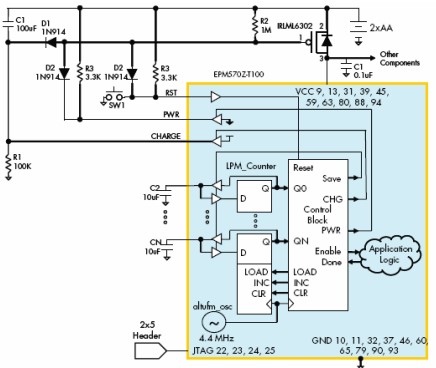

很多系統(tǒng)管理應(yīng)用需要采用定時(shí)器。設(shè)計(jì)人員可能會(huì)吃驚地發(fā)現(xiàn)CPLD可以用于實(shí)現(xiàn)通常由微控制器完成的定時(shí)器功能。利用幾個(gè)分立電容、電阻、二極管和金屬氧化物半導(dǎo)體場效應(yīng)晶體管(MOSFET),設(shè)計(jì)一個(gè)簡單但是有效的電阻電容(RC)定時(shí)器電路,周期性的對(duì)CPLD上電。在圖4的實(shí)例電路中,設(shè)置RC值來建立一個(gè)10秒定時(shí)器。可以利用三個(gè)外部電容(C1、C2和C3)來擴(kuò)展這一基本定時(shí)器,三個(gè)電容被用于建立一個(gè)簡單的非易失二進(jìn)制計(jì)數(shù)器。這樣,在MAX IIZ EPM240Z CPLD中利用19%的邏輯就可以完全實(shí)現(xiàn)從10秒到80秒的間隔周期(2)。

圖4. 為MAX IIZ CPLD開發(fā)基于定時(shí)器的上電電路

CPLD和微控制器結(jié)合使用的實(shí)例

CPLD并不總是和微控制器相競爭。在以下幾個(gè)例子中,CPLD是微控制器優(yōu)異的輔助器件。

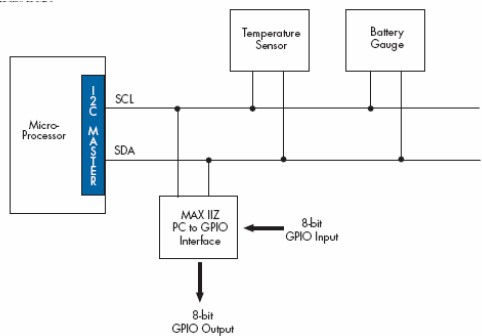

GPIO引腳擴(kuò)展

在常見的通用I/O(GPIO)引腳擴(kuò)展應(yīng)用中,設(shè)計(jì)人員把低成本小型微控制器的可編程功能和CPLD的通用IO資源結(jié)合起來使用。CPLD構(gòu)建一組內(nèi)部寄存器,微控制器通過I2C或者SPI等串口來訪問這些寄存器(圖5),使微控制器能夠使用現(xiàn)有的I/O資源來擴(kuò)展其I/O總數(shù)量。利用擴(kuò)展I/O,設(shè)計(jì)人員還可以使用CPLD進(jìn)行電平轉(zhuǎn)換,從而提高了CPLD的實(shí)用性(3)。

圖5. GPIO引腳擴(kuò)展

端口管理

便攜式應(yīng)用設(shè)計(jì)人員經(jīng)常需要連接具有不同I/O接口的器件。這一功能被稱為橋接,因?yàn)椴捎肅PLD來構(gòu)成不同接口之間的“橋”。這一節(jié)介紹三個(gè)這樣的例子:

串行至串行 - I2C至SPI

串行至并行 – SPI器件(串行)至主處理器(并行)

并行至并行 - 主處理器至CF+

在每一例子中,有幾個(gè)原因表明為什么CPLD是優(yōu)于微控制器的選擇。一個(gè)原因是微控制器不能有效地提供需要的I/O數(shù)量。采用微控制器不一定能滿足接口需要的性能。此外,在微控制器中實(shí)現(xiàn)這些功能要比在CPLD硬件中復(fù)雜得多。

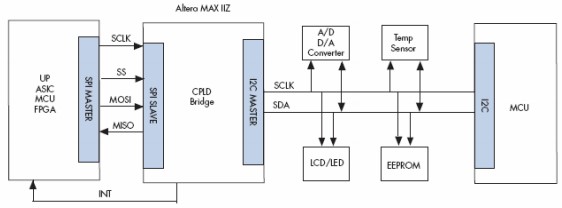

串行至串行轉(zhuǎn)換

圖6所示為采用CPLD來橋接兩種不同的串口:I2C和SPI。這一設(shè)計(jì)可以在MAX IIZ EPM240Z CPLD中實(shí)現(xiàn),使用了大約43%的邏輯和6個(gè)I/O引腳(4)。

圖6. 利用MAX IIZ CPLD實(shí)現(xiàn)I2C至SPI接口

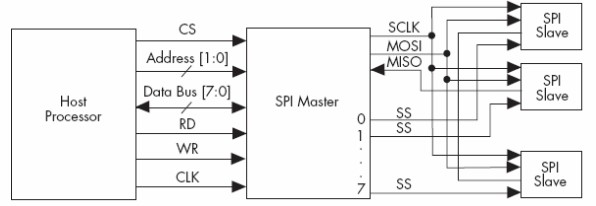

串行至并行轉(zhuǎn)換

圖7所示為主處理器和SPI主機(jī)的接口,使用CPLD來實(shí)現(xiàn)串并轉(zhuǎn)換接口。這個(gè)例子建立一個(gè)主處理器總線接口和完整的SPI主機(jī),可以在MAX IIZ EPM240Z CPLD中實(shí)現(xiàn),占用了大約30%的邏輯和25個(gè)I/O引腳(5)。

圖7. 利用MAX IIZ CPLD實(shí)現(xiàn)主處理器至SPI接口

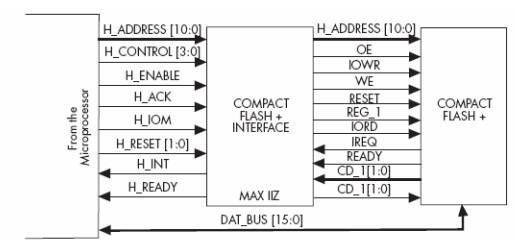

并行至并行轉(zhuǎn)換

在圖8中,CPLD被用于橋接兩種不同的并口。這一實(shí)例實(shí)現(xiàn)了Compact FLASH+器件的主處理器總線接口,在MAX IIZEPM240Z CPLD中實(shí)現(xiàn),使用了大約54%的邏輯,以及45個(gè)I/O引腳(6)。

圖8. 利用MAX IIZ CPLD實(shí)現(xiàn)主處理器至CF+接口

傳統(tǒng)上,某些微控制器一直是低功耗電子設(shè)計(jì)人員的唯一“可編程”邏輯選擇。然而,隨著低功耗CPLD的推出,設(shè)計(jì)人員在便攜式應(yīng)用上有了新的選擇。本白皮書的多個(gè)實(shí)例介紹了怎樣在便攜式應(yīng)用中使用低功耗CPLD來替代或者擴(kuò)展以前在微控制器中實(shí)現(xiàn)的多種功能。結(jié)果,低功耗電子設(shè)計(jì)人員在便攜式應(yīng)用中擁有了另一套解決問題的工具,在設(shè)計(jì)創(chuàng)新產(chǎn)品時(shí),能更好地選擇最佳器件。

-

微控制器

+關(guān)注

關(guān)注

48文章

7896瀏覽量

153589 -

cpld

+關(guān)注

關(guān)注

32文章

1257瀏覽量

170889 -

可編程邏輯

+關(guān)注

關(guān)注

7文章

524瀏覽量

44534

發(fā)布評(píng)論請(qǐng)先 登錄

微控制器(MCU)架構(gòu)介紹

如何利用MSP430FR2676TPTR和MAX32660等微控制器來促進(jìn)可穿戴式設(shè)計(jì)?

LPC2194微控制器替代品有哪些?

采用可定制微控制器來優(yōu)化算法的設(shè)計(jì)

PLD和數(shù)據(jù)通路來釋放微控制器中CPU資源

利用CPLD來替代微控制器的設(shè)計(jì)

評(píng)論