引 言

網絡化運動控制是未來運動控制的發展趨勢,隨著高速加工技術的發展,對網絡節點間的時間同步精度提出了更高的要求。如造紙機械,運行速度為1 500~1 800m/min,同步運行的電機之間1μs的時間同步誤差將造成30 μm的運動誤差。高速加工中心中加工速度為120 m/min時,伺服電機之間1μs的時間同步誤差,將造成2 μm的加工誤差,影響了加工精度的提高。

分布式網絡中節點的時鐘通常是采用晶振+計數器的方式來實現,由于晶振本身的精度以及穩定性問題,造成了時間運行的誤差。時鐘同步通常是選定一個節點時鐘作為主時鐘,其他節點時鐘作為從時鐘。主節點周期性地通過報文將主時鐘時間發送給從節點,從節點接收到報文后,以主時鐘為基準進行延遲補償,然后將計算出的新時鐘值賦給從時鐘。這種同步方法造成了從時鐘計數值的不連續,即會出現重復(從時鐘晶振頻率快于主時鐘)或跳躍(從時鐘晶振頻率慢于主時鐘),而且這種方法并沒有從根本上解決時鐘頻率的不同步問題,因此要進一步提高同步精度很困難。本文研究了一種可對頻率進行動態調整的時鐘,通過對時鐘頻率的動態修正,實現主從時鐘頻率的同步,進而實現時間同步。

1 時鐘同步原理

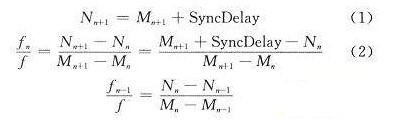

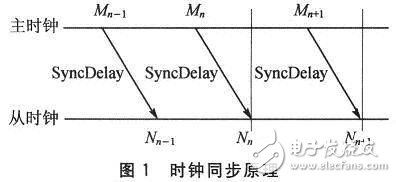

要實現兩個時鐘的同步,一是時鐘的計數值要相同,二是計數增長速率要相同。如圖1所示,設主時鐘的頻率為f,從時鐘頻率在Nn-1到Nn時間段為fn-1,在Nn到Nn+1為fn,SyncDelay為同步報文從主站到從站的延遲時間,可以通過延時測量幀采用往返法測量得到,從時鐘要在Nn+1時刻達到與主時鐘相等,那么有:

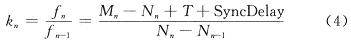

因為主時鐘是周期性發出同步報文,所以有Mn+1-Mn=Mn-Mn-1=T,由式(2)和(3)可得:

kn就是時鐘頻率調整系數。在每個同步周期可以計算出頻率調整系數,然后通過相應的硬件電路來實現頻率調節。

2 可調頻率的時鐘設計

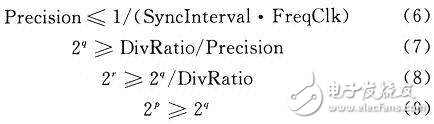

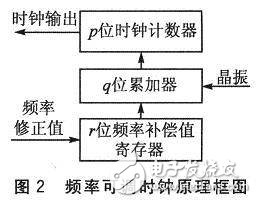

可調頻率時鐘是一種完全由數字電路組成的時鐘計數器,構造簡單,可以很方便地在FPGA中實現,原理如圖2所示。該頻率可調時鐘由一個戶位時鐘計數器,q位累加器和r位頻率補償值寄存器組成。每個晶振周期,累加器與頻率補償寄存器中的FreqCompValue相加,并將結果保存到累加器。如果累加器發生溢出,時鐘計數器的值就增加1;反之,時鐘計數器保持不變。由此可以看出,晶振頻率和頻率補償值FreqCompValue的大小決定了累加器的溢出速率,也決定了時鐘計數器的計數頻率。所以可以通過調整FreqCompValue來調節時鐘頻率。為了實現高精度時鐘,晶振頻率要比時鐘頻率高。設晶振頻率為FreqOsc,時鐘計數頻率為FreqClk,分頻比為DivRatio,同步周期為SyncInterval,補償精度為Precision,p、q、r可由下列公式得出:

DivRatio=FreqOsc/FreqClk (5)

在本系統中,取FreqClk為50 MHz,FreqOsc為60MHz,則DivRatio為1.2。當同步周期為1 s時,補償精度Precision可選10-9,由公式可選擇r=q=32,p=64。頻率補償初值由下式求出:

FreqCompValue=2q/DivRatio=232/1.2=32d3579139413

在時鐘輸出算法中,該值由頻率調整系數動態調整:

FreqCompValuen=kn·FreqCompValuen-1 (10)

3 頻率補償算法在FPGA中的實現

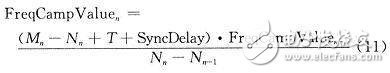

由式(4)和式(10)可得:

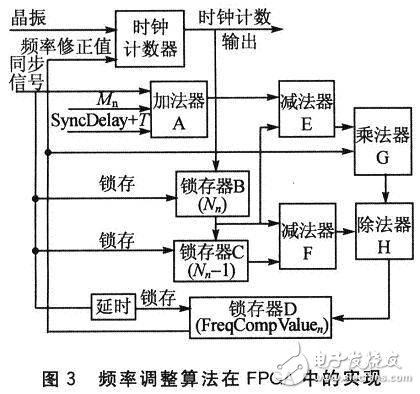

頻率補償就是在每個同步周期計算FreqCompValuen,FPGA提供了參數化的乘法器兆函數(1pm_mult)和除法器兆函數(1pm_divide),可以快速實現上述算法。原理如圖3所示,在每個同步周期同步信號的驅使下,鎖存器B和C分別鎖存當前時鐘讀數和上個同步周期時鐘讀數,同時將主時鐘讀數輸入到加法器A中,經過減法器E、F和乘法器G,以及除法器H后計算出新的FreqCompValuen,并在同步信號的驅動下,將其鎖存到鎖存器D中。由于中間的計算結果要經過一定的時鐘周期,所以鎖存器D的鎖存信號要延時一定的晶振周期。在本設計中延時50個FreqOsc,即在《1μs的情況下就可以得到新的頻率補償值。

同步報文的傳輸延遲SyncDelay理論上是不變的,而實際上報文在傳輸過程中有抖動。參考文獻[3]對此進行了分析,并指出同步周期越長,報文傳輸延遲抖動的影響就越小,因此可以忽略不計。

4 實驗驗證

主時鐘采用50 MHz的有源晶振來實現,并將其作為固定時鐘;從時鐘采用30 MHz有源晶振,通過FPGA的鎖相環PLL將其頻率倍頻到60 MHz,然后1.2分頻,實現可調頻率的50 MHz時鐘。

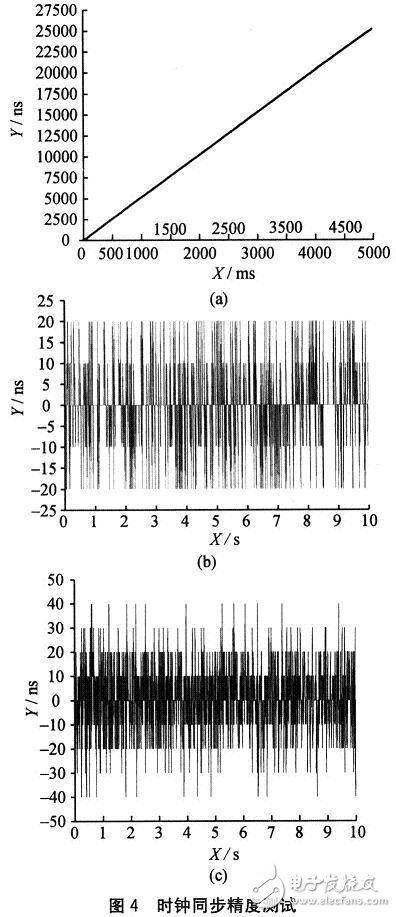

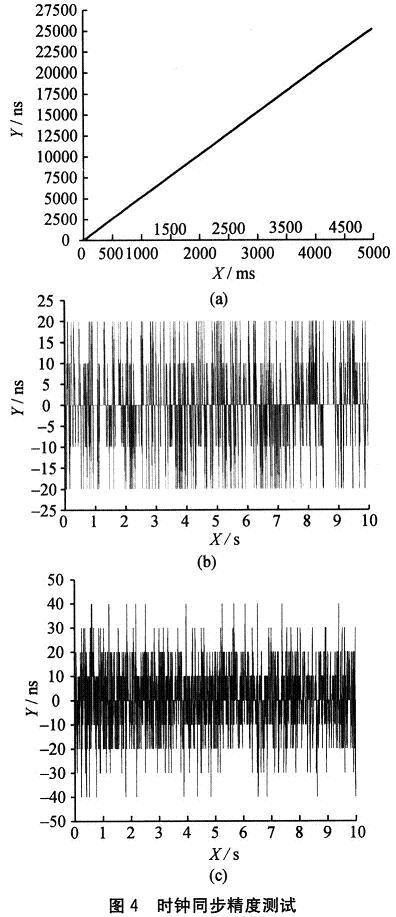

讓主時鐘和從時鐘以一定的時間間隔產生中斷,并通過邏輯分析儀采樣中斷信號分析其偏差。由于系統時鐘的分辨率為20 ns,采用廣州致遠電子有限公司的邏輯分析儀LA1532,其最大采樣頻率為100 MHz,所以偏差測量精度可以達到10 ns。圖4(a)是未進行同步前兩個時鐘的偏差分析,X軸表示主時鐘和從時鐘的計時長度,Y軸表示主時鐘和從時鐘的計時偏差。從圖中可以看出兩個時鐘的偏差大概為5×10-6,即1 s內的偏差可以達到5μs。圖4(b)為同步后主時鐘和從時鐘偏差測量結果,共測量1 000次,其10 ms內同步偏差在±20 ns。X軸表示測量時間,Y軸表示主從時鐘同步偏差。圖4(c)為同步后兩個從時鐘偏差測量結果,共測量1 000次,其10 ms內同步偏差在±40 ns。X軸表示測量時間,Y軸表示從時鐘之間同步偏差。

結 語

基于時鐘頻率調整的時間同步方法,實現簡單,而且沒有復雜的軟件同步協議,占用較小的網絡帶寬就可以實現高精度的時鐘同步,在硬件上只需要低成本的FPGA支持。

-

FPGA

+關注

關注

1629文章

21748瀏覽量

603885 -

晶振

+關注

關注

34文章

2871瀏覽量

68078 -

計數器

+關注

關注

32文章

2256瀏覽量

94641

發布評論請先 登錄

相關推薦

基于NTP的高精度時鐘同步系統實現

為什么無線通信網絡需要同步?什么是頻率同步和相位同步?

一種脈沖信號載波頻率同步環及FPGA實現

基于FPGA 的高速高精度頻率測量的研究

OFDM的頻率同步算法

基于FPGA的高速高精度頻率測量的研究

如何使用FPGA實現脈沖信號載波頻率同步環

采用FPGA技術實現高精度的時鐘頻率同步的方法

采用FPGA技術實現高精度的時鐘頻率同步的方法

評論