本文分析了SPI 存儲器的結(jié)構(gòu)特點和測試難點,提出了一種基于并行轉(zhuǎn)串行邏輯的SPI 存儲器算法圖形自動產(chǎn)生的方法,并以SPI EEPROM 芯片AT25HP512 為例,實現(xiàn)了測試程序開發(fā)。實驗證實,該方法可以克服SPI 存儲器地址算法自動產(chǎn)生的困難,對該類芯片測試具有通用性。

0 引言

串行存儲器大多采用I2C 或SPI 接口進(jìn)行訪問,其中以SPI 接口的芯片最多,主要包括EEPROM、FLASH memory、FRAM等類型。與并行存儲器相比,串行存儲器引腳少、體積小、易于擴(kuò)展、與單片機(jī)或控制器連接簡單、工作可靠,而且大多擁有掉電保持?jǐn)?shù)據(jù)的特性,所以越來越多地用在各類電子產(chǎn)品和工業(yè)測控系統(tǒng)中。但SPI 存儲器所有輸入的內(nèi)容全都由一個管腳完成,通用自動測試儀無法分辨這些信息類型,因此不便于實現(xiàn)地址自動算法產(chǎn)生,這給使用通用測試儀測試該類芯片帶來了很大難度。本文首先介紹了SPI 類串行接口存儲器的結(jié)構(gòu),進(jìn)而以芯片AT25HP512 為例,講述了其工作原理及測試難點,最后提出了一種能應(yīng)用于通用自動測試儀的SPI 存儲器測試方法。

1 SPI 串行接口存儲器的基本結(jié)構(gòu)

1.1 SPI 總線的結(jié)構(gòu)

SPI 是一種通用串行接口總線,字長為8 位或16 位,SPI接口利用SCK、SI 和SO 三根線進(jìn)行數(shù)據(jù)讀/ 寫。其中,SCK 為時鐘信號,用于對數(shù)據(jù)傳輸?shù)乃俾蔬M(jìn)行同步,在每一個SCK 周期,有一位數(shù)據(jù)移入或移出串行存儲器。SI 為串行數(shù)據(jù)輸入,用于輸入命令和數(shù)據(jù)。SO 為串行數(shù)據(jù)輸出,用于輸出狀態(tài)和數(shù)據(jù)。本文將以一種典型的SPI EEPROM AT25HP512 為例分析其結(jié)構(gòu)及訪問方式。圖1 為AT25HP512 芯片的管腳定義,其他SPI存儲器通常也都有類似的管腳。

1.2 AT25HP512 的讀/ 寫方式

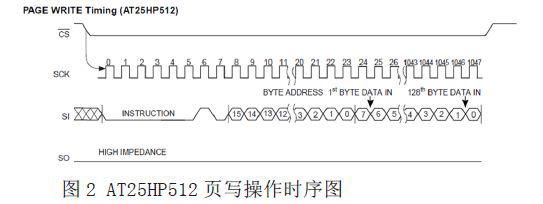

AT25HP512 容量64K 位,采取分頁存儲的結(jié)構(gòu),每頁128 位,既可隨機(jī)讀/ 寫數(shù)據(jù),又可以以序列方式連續(xù)讀/ 寫。序列讀操作一旦執(zhí)行,位地址可以自動增加,直到讀出所有單元;序列寫操作一旦執(zhí)行,可以完成一頁的128 位寫。圖2 為AT25HP512頁寫操作的時序圖,利用該特性可快速完成數(shù)據(jù)的訪問。

2 使用自動測試儀測試SPI 存儲器的難點

2.1 數(shù)字集成電路自動測試儀的特點

自動測試儀(ATE),用于檢測集成電路功能的完整性。標(biāo)準(zhǔn)的數(shù)字ATE 可針對專用及通用數(shù)字電路提供高速、高通道數(shù)字控制、測試能力。芯片的測試程序通常會有許多個功能測試向量以測試不同的功能模塊,這些向量都會被加載ATE 內(nèi)存中,以順序或并發(fā)方式被執(zhí)行。在實際生產(chǎn)過程中,由于受ATE 內(nèi)存大小(即圖形深度)的限制,如果向量過長,超過測試設(shè)備圖形深度,就要加載一段向量,測試一段向量,再加載一段向量,再測試。該做法會使測試成本大為增加,因此往往不允許多次加載,所有測試向量需要一次性加載或由算法自動產(chǎn)生,以保證測試的連續(xù)性。

2.2 存儲器測試特點

存儲器雖然邏輯結(jié)構(gòu)簡單,但容量通常較大,而且由于存儲器各個存儲單元有可能出現(xiàn)相互打擾,即某個存儲單元的數(shù)據(jù)變化可能引起其他單元的變化,因此存儲器需要反復(fù)讀/ 寫的測試,測試向量的總長度往往超過ATE 的測試圖形深度。針對存儲器這種結(jié)構(gòu)固定、可連續(xù)訪問、測試算法固定的器件,需要ATE 能根據(jù)算法自動產(chǎn)生測試圖形,用比較短的測試向量,按照固定地址產(chǎn)生邏輯自動完成有規(guī)律的地址變化,實現(xiàn)連續(xù)讀/寫操作。

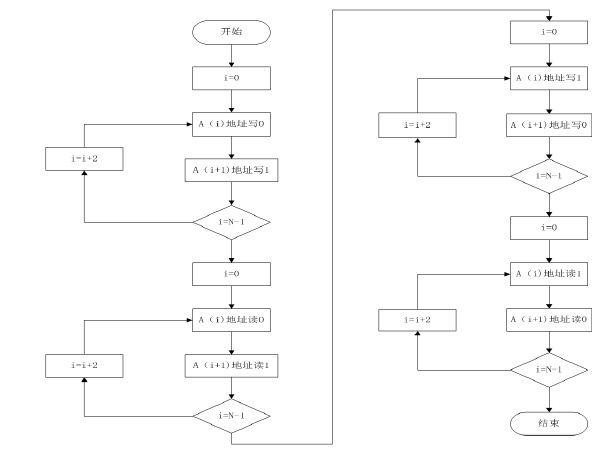

通用ATE 一般都具備一組或多組地址產(chǎn)生器(APG),該單元模塊可完成地址保持(HOLD)、自加(INC)、自減(DEC)等操作,使用這些標(biāo)準(zhǔn)邏輯,就可以實現(xiàn)絕大多數(shù)的存儲器測試算法。以最常用的棋盤格測試算法為例。

如果順序?qū)憸y試程序,需要4N 的測試向量深度(N 為存儲器容量),但是用測試算法,每一步流程只需要幾條向量,全部只需要用幾十條向量就能完成,具體方法如圖3 所示。可見利用自動地址產(chǎn)生邏輯,可以實現(xiàn)極大深度的存儲器測試。

2.3 SPI 存儲器測試難點

上述方法可用于多數(shù)并行存儲器,但難以用于SPI 存儲器。

主要原因為:

(1)SPI 存儲器沒有獨立的數(shù)據(jù)總線和地址總線,所有輸入都由SI 這一根線完成,SI 除要發(fā)送地址外,還要發(fā)送數(shù)據(jù)和指令,無法獨立應(yīng)用于地址操作,也就無法完成對地址的算法產(chǎn)生,如INC 等;

(2)SPI 總線通常應(yīng)用8 位寄存器,為完成一個數(shù)據(jù)傳輸需要在8 個時鐘周期,由8 條向量串行執(zhí)行,這就大大增加了向量的長度。因此,盡管ATE 有足夠的數(shù)據(jù)寬度,卻往往受限于數(shù)據(jù)位的深度不足,無法完成測試。

3 SPI 存儲器的測試實現(xiàn)方法

首先,SCK 信號要按測試需求產(chǎn)生測試時鐘,~CS、~WP 和~HOLD 給出相應(yīng)控制信號。

其次,為了利用了測試儀的通道寬度,減少測試向量的深度,需要將串行發(fā)送的數(shù)據(jù)以并行的方式存儲于測試儀中。多數(shù)通用測試儀都設(shè)計了并行轉(zhuǎn)串行的邏輯模塊,即在多個通道上并行輸入數(shù)據(jù),通過系統(tǒng)指令完成轉(zhuǎn)換,由一個通道將數(shù)據(jù)發(fā)送出來。如果ATE 不具備該功能,也可由外部邏輯實現(xiàn)。

最后,要最大限度地應(yīng)用測試儀的AGP 模塊地址自動產(chǎn)生邏輯,將串行程序算法并行化處理,最終給出區(qū)別存儲器地址和其他輸入信息的控制邏輯。

3.1 棋盤格算法測試

以AT25HP512 棋盤格測試為例,串行SPI 存儲器測試可分為以下步驟。

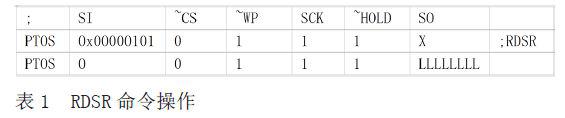

(1)并行轉(zhuǎn)串行。存儲器待收發(fā)的數(shù)據(jù)和指令都以8 位并行的方式放置在內(nèi)部寄存器中,因此要借助ATE 并行轉(zhuǎn)串行輸出功能,將8 個通道的數(shù)據(jù)從一個通道輸出。以并行轉(zhuǎn)串行指令PTOS 為例,PTOS 00000101,相當(dāng)于從SI 引腳在8 個周期串行輸出0 0 0 0 0 1 0 1 ;

(2)將指令寄存的數(shù)據(jù)以8 位并行方式連接到測試通道上。

以讀狀態(tài)寄存器命令為例,SI 要輸出的數(shù)據(jù)連接到不同通道,再由并轉(zhuǎn)串邏輯電路輸出。讀出的結(jié)果與預(yù)期值進(jìn)行比較。

表1 相當(dāng)于執(zhí)行了讀狀態(tài)寄存器命令RDSR,本例中讀回的預(yù)期結(jié)果為LLLLLLLL.

(3)設(shè)置狀態(tài)寄存器。發(fā)送寫狀態(tài)寄存器命令WRSR,設(shè)置存儲器為寫READY 狀態(tài)。

(4)將8 位地址線連接到AGP 相關(guān)的通道上。

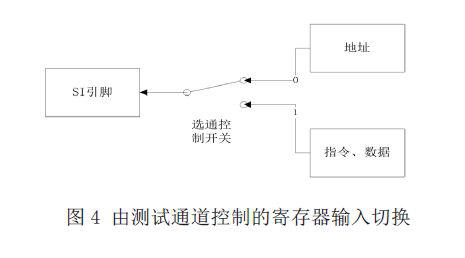

(5)為了能在SI 引腳上既能輸出地址又能輸出指令和數(shù)據(jù),要設(shè)置多路選擇單元,完成切換。切換控制位可以由通道位完成。圖4 為測試通道控制的寄存器輸入切換,控制位為0,SI引腳切換至地址線,控制位為1,SI 引腳切換至數(shù)據(jù)線和指令線。

應(yīng)用該開關(guān),就可以把需要使用算法的地址和不需要利用算法的指令和數(shù)據(jù)在通道上分開。

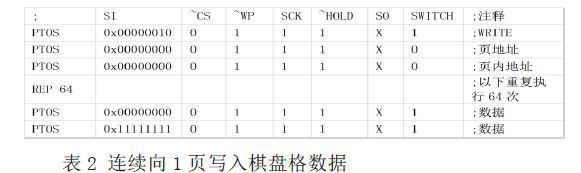

(6) 完成向存儲單元寫入數(shù)據(jù)的操作。表2 實現(xiàn)了連續(xù)寫一頁的函數(shù)PAGEWRITE 操作,從0 地址開始連續(xù)進(jìn)行128 個寫操作,把00000000 和11111111 的棋盤格數(shù)據(jù)交替寫入一頁中。

(7) 利用AGP,實現(xiàn)頁地址遞增操作。每一頁寫都調(diào)用PAGEWRITE,每完成一次頁寫操作,頁地址自動加1,執(zhí)行下一頁的寫操作,直到全部頁的寫操作完成。表3 為每調(diào)用一次單頁寫,頁地址自動加1 的操作。

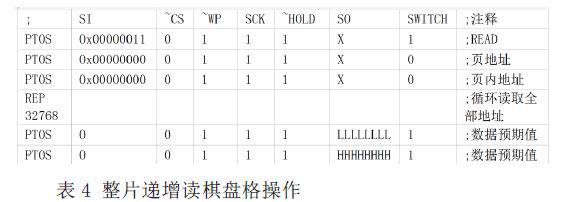

(8) 讀并檢驗結(jié)果操作。與寫操作類似,給出讀指令和起始地址后,可連續(xù)讀出所有單元。

以上方法,首先完成了逐頁的連續(xù)寫操作,頁地址可自動遞增,每完成一次正向棋盤格(按0101 格式)寫操作后,再以0 地址為起始地址,完成整個器件地址自動遞增的連續(xù)讀操作。然后再按照相同的方法執(zhí)行一次反向棋盤格(按1010 格式)的寫、讀,從而實現(xiàn)完整的棋盤格測試。

3.2 其他測試算法

在實際工程中應(yīng)用最多的是存儲器測試法算法復(fù)雜度為N的測試算法,除棋盤格測試法外,較為常用的還有齊步法、列條圖形法和前進(jìn)后退法等。應(yīng)用這些算法測試SPI 存儲器都與棋盤格測試類似,只是AGP 自動產(chǎn)生算法的方式不同,本文不再詳述。

4 結(jié)語

本文分析了SPI 串行存儲器的結(jié)構(gòu)和訪問方式,利用通用自動測試儀的并行轉(zhuǎn)串行指令,增加了選通控制邏輯,為ATMEL公司的SPI 串行存儲器AT25HP512 編寫了測試程序,該程序最終以二進(jìn)制代碼的形式順序存儲于測試儀中。實驗證明,該方法可以克服SPI 存儲器地址算法自動產(chǎn)生的困難,對該類芯片測試具有通用性。

-

芯片

+關(guān)注

關(guān)注

459文章

52243瀏覽量

436712 -

集成電路

+關(guān)注

關(guān)注

5420文章

11968瀏覽量

367315 -

存儲器

+關(guān)注

關(guān)注

38文章

7637瀏覽量

166497

發(fā)布評論請先 登錄

一種熱源自動測試儀的實現(xiàn)

PCB背板自動測試儀的設(shè)計開發(fā)

機(jī)載電子設(shè)備通用自動測試系統(tǒng)研究與實現(xiàn)

【TL6748 DSP申請】自動測試儀

伏安特性測試儀的原理和主要特點

無線設(shè)備自動測試系統(tǒng)的特點

一種大容量電纜自動測試儀的設(shè)計和實現(xiàn)

機(jī)內(nèi)通話器自動測試儀設(shè)計

繼電器自動測試儀

IPM自動測試平臺的研究及實現(xiàn)

PMU測試儀的設(shè)計與研究

評論