驗證技術的發展

在目前的集成電路設計中,芯片的規模和復雜程度正呈指數增加,為保證所設計芯片功能的正確性,需要花費比以往更多的時間和人力,困難度大幅增加。而且,目前的功能驗證能力已經遠遠落后于設計能力,功能驗證正成為大規模芯片設計的瓶頸。設計人員通常需要花費50%~70%的時間去驗證他們的設計。雖然有形式驗證等多種驗證方法可供選擇,但是設計者還是偏好基于仿真的驗證,本文中的驗證主要是指仿真。為了降低驗證的工作量和提高驗證的效率,越來越多的設計人員采用高級驗證語言(HLV)來進行芯片驗證。

驗證技術的發展主要經歷了以下幾個階段:

1. 基于HDL語言的驗證

用HDL語言來建立測試平臺和編寫測試向量,將激勵輸入給設計,然后檢查設計的輸

出。這種方法的缺點是測試平臺和測試向量的建立和編寫非常復雜和困難,并且驗證所需的激勵難以達到足夠的覆蓋率。

2. 面向對象的驗證

由于采用HDL語言進行驗證的局限性,設計人員可以使用面向對象的高級語言(如C++、Python)來建立驗證環境和編寫激勵。這種驗證方法可以使設計人員從比較抽象的設計高層,對設計的輸入和輸出進行建模,然后通過驗證環境與仿真器的通信接口,將抽象的數據模型轉換成比特形式的數據。這種驗證方法大大降低了編寫激勵的工作量,但是驗證環境的建立相對復雜,比如驗證環境與仿真器的通信接口等。

3. 隨機產生激勵

由于測試激勵編寫的工作量非常大,所以設計人員逐步采用隨機產生測試向量的方法,以減輕編寫激勵的工作量,并提高驗證的覆蓋率。但是它的缺點在于,由于激勵是隨機產生的,所以給驗證結果的檢查帶來了一定難度,并且設計者不能根據要驗證的設計屬性來產生所需的激勵,即不能根據約束來產生激勵。

4. 驗證平臺工具

由于驗證環境的建立過于復雜,因此出現了驗證平臺工具,通過這種工具可以大大減少建立驗證環境的工作量。但是這類驗證工具不能使驗證人員通過設計的抽象層來編寫激勵,而且不能實現設計時序行為的檢查。

驗證自動化系統

由于上述驗證方法都或多或少具有局限性,所以需要一種完善的驗證系統。根據上節所述,一種完善的驗證自動化系統需要具備以下幾個功能:首先它能夠定義驗證計劃;然后能夠提供接口,用高級語言從抽象的層次產生基于約束的激勵;并且能方便高效地建立驗證環境;最后能夠完成設計時序行為的驗證和基于斷言的功能覆蓋率的驗證。

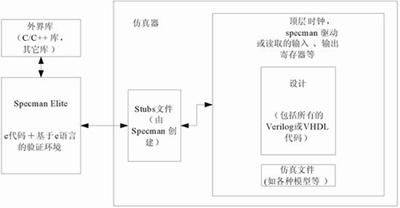

e語言是一種功能強大的驗證語言,它可以很好地實現一個驗證自動化系統,如圖1所示。在這個驗證系統中,首先可以根據驗證者的需要,用e語言來制定一些約束,根據這些約束來產生驗證需要的激勵。由于e可以很好地與Verilog和VHDL仿真器通信,因此可以將這些用e語言抽象描述的數據轉換成比特形式,然后加載給設計;再通過和仿真器的通信,對系統進行功能仿真,并將設計的輸出收集起來,這時可以將比特形式的數據轉換回e語言的抽象描述,以便于對設計行為與預期結果進行檢查。除此之外,e語言還可以實現設計時序行為的檢查。如果一個中斷必須在請求后的5個周期后發出,可以通過e語言來描述這個設計屬性,通過仿真來檢查其是否滿足。最后,e語言還可以用來進行基于斷言的功能覆蓋率驗證。

基于e語言的驗證環境與仿真器的交互

在具體介紹基于e語言的驗證環境之前,先介紹一下基于e語言的驗證環境與仿真器的通信機理。目前,Cadence公司的工具Specman Elite支持用e語言來建立驗證自動化系統,Specman Elite提供可配置、可再使用和可擴展的驗證組件,這些組件被稱為eVC。eVC采用高級驗證語言e編寫,能夠產生足夠多的測試激勵訊號,并能對設計行為與預期結果進行檢查確認。eVC可以極大地縮短驗證時間,提高產品品質。所以本文將以Specman為例來介紹基于e語言的驗證環境與仿真器是如何協同工作的。

Specman和仿真器在仿真的過程中是兩個獨立

并行的進程,它們通過通信接口(stubs文件)來進行通信,其結構如圖2所示。

圖2 仿真器結構

仿真環境包含以下各組成部分:

Specman:整個驗證環境是用e語言實現的,其中包括約束、激勵產生、驅動、檢查、覆蓋率等,所有的e文件都由Specman編譯和仿真。

仿真器:Verilog或VHDL仿真器,它通過stubs文件與Specman進行通信。

外界庫:仿真用到的一些模型可能是基于C語言的,e語言可以很好地導入這些模型來進行仿真。

設計:基于Verilog或VHDL的設計。

仿真文件:在仿真中可能用到的一些外部模型,如總線功能模型等。

頂層:包括設計和各種模型的例化和一些驅動輸入或收集輸出的寄存器。

Stubs文件:Specman讀入所有的e文件,然后用一個命令來生成所需要的Stubs文件,這個文件在仿真過程中是由仿真器編譯和仿真的。

基于e語言的驗證環境

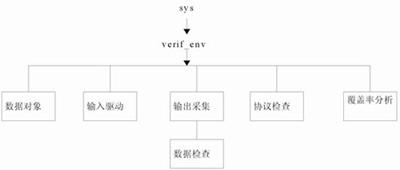

基于e語言的驗證環境包括許多組成部分,其基本結構如圖3所示。

圖3 基本結構

其中數據對象代表固定格式的測試向量,如數據包、視頻中的一幀數據,或CPU的一種指令。激勵產生

會對數據對象添加一定的約束,隨機產生基于約束的激勵。輸入驅動中包括一個輸入程序,負責將數據輸入給設計,根據設計的不同,有可能對設計進行重復多次的輸入。輸出采集中包括一個采集設計輸出的程序,并將采集到的數據轉換成數據對象定義的形式,然后送到數據檢查模塊進行檢查。數據檢查部分產生所需要的數據和存儲收集到的數據的程序,并完成數據檢查。協議檢查通過定義一些時序上的斷言來監控設計的協議,如果違反了協議將產生警告或錯誤提示。覆蓋率分析會分析設計中的斷言,給出設計的功能覆蓋率報告。

Specman提供約束解釋器和通信信道來進行e語言的仿真,界面對象(interface object)負責將數據對象驅動給設計的界面,系統對象(system object)包括各種不同的界面對象。界面對象和系統對象根據每個設計來編寫,如對CPU進行驗證時,根據設計定義輸入給CPU的數據對象(指令格式等),因此驗證環境不需要隨著設計的改變而改變,所以一個設計的環境是可以重用的。不同的測試激勵通過約束數據對象、界面對象、系統對象來產生。驗證環境的劃分框

圖如圖4所示。

圖4 驗證環境的劃分框圖

基于e語言的驗證環境的文件層次結構如圖5所示,其最頂層文件名字固定為sys,在sys下例化所有的模塊。

圖5 文件層次結構

結語

本文介紹了目前國外各大芯片設計公司所采用的最新的驗證技術——基于e語言的自動驗證系統。采用e語言建立驗證環境、編寫測試激勵,可大大降低芯片驗證人員的工作量,提高驗證效率。

-

芯片

+關注

關注

456文章

50950瀏覽量

424736 -

集成電路

+關注

關注

5389文章

11574瀏覽量

362315 -

仿真器

+關注

關注

14文章

1019瀏覽量

83807

發布評論請先 登錄

相關推薦

基于VMM驗證方法學的MCU驗證環境

基于VMM的驗證環境的驗證MCU指令實現設計

基于VMM驗證方法學的MCU驗證環境實現方法介紹

驗證方法簡介

一個優秀的SOC驗證環境應該具備哪些功能呢

Python硬件驗證——摘要

SoC驗證環境搭建方法的研究

基于SystemVerilog語言的驗證方法學介紹

基于e語言的自動驗證環境結構與優勢介紹

基于e語言的自動驗證環境結構與優勢介紹

評論