引言

隨著FPGA的設計速度、尺寸和復雜度明顯增長,使得整個設計流程中的實時驗證和調試成為當前FPGA系統的關鍵部分。獲得FPGA內部信號有限、FPGA封裝和印刷電路板(PCB)電氣噪聲,這一切使得設計調試和檢驗變成設計周期中最困難的流程。另一方面,幾乎當前所有的像CPU、DSP、ASIC等高速芯片的總線,除了提供高速并行總線接口外,正迅速向高速串行接口的方向發展,FPGA也不例外,每一條物理鏈路的速度從600Mbps到高達10Gbps,高速I/O的測試和驗證更成為傳統專注于FPGA內部邏輯設計的設計人員面臨的巨大挑戰。這些挑戰使設計人員非常容易會把絕大部分設計周期時間放在調試和檢驗設計上。為幫助您完成設計調試和檢驗流程,它需要使用新的調試和測試工具,幫助調試設計,同時支持在FPGA上全速運行。

本文重點介紹在調試FPGA系統時遇到的問題及有助于提高調試效率的技術,針對Altera和Xilinx的FPGA調試提供了最新的方法和工具。

FPGA設計流程概述

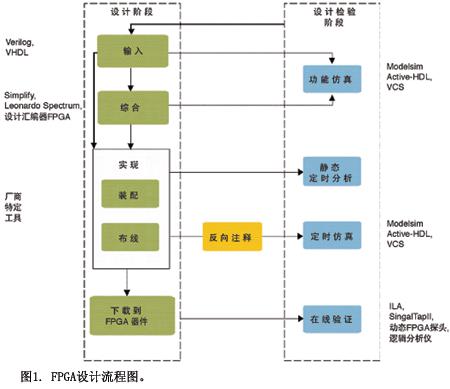

在FPGA系統設計完成前,有兩個不同的階段:設計階段,調試和檢驗階段(參見圖1)。設計階段的主要任務是輸入、仿真和實現。調試和檢驗階段的主要任務是檢驗設計,校正發現的任何錯誤。

設計階段

在這一階段不僅要設計,而且要使用仿真工具開始調試。實踐證明,正確使用仿真為找到和校正設計錯誤提供了一條有效的途徑。但是,不應依賴仿真作為調試FPGA設計的唯一工具。

在設計階段,還需要提前考慮調試和檢驗階段,規劃怎樣在線快速調試FPGA,這可以定義整體調試方法,幫助識別要求的任何測試測量工具,確定選擇的調試方法對電路板設計帶來的影響。針對可能選用的FPGA存在的高速總線,除了考慮邏輯時序的測試和驗證外,還應該充分考慮后面可能面臨的信號完整性測試和分析難題。

調試和檢驗階段

在調試階段,必需找到仿真沒有找到的棘手問題。怎樣以省時省力的方式完成這一工作是一個挑戰。

在本文的第一部分,我們將考察怎樣選擇正確的FPGA調試方法及怎樣有效利用新方法的處理能力,這些新方法可以只使用少量的FPGA針腳查看許多內部FPGA信號。如果使用得當,您可以突破最棘手的FPGA調試問題。

FPGA調試方法

在設計階段需要作出的關鍵選擇是使用哪種FPGA調試方法。在理想情況下,您希望有一種方法,這種方法可以移植到所有FPGA設計中,能夠洞察FPGA內部運行和系統運行過程,為確定和分析棘手的問題提供相應的處理能力。

基本在線FPGA調試方法有兩種:使用嵌入式邏輯分析儀以及使用外部邏輯分析儀。選擇使用哪種方法取決于項目的調試需求。

嵌入式邏輯分析儀內核

主要FPGA廠商針對器件的在線調試都提供了嵌入式邏輯分析儀內核,如Altera的SignalTap II和Xilinx的ChipScope ILA。這些知識產權模塊插入FPGA設計中,同時提供觸發功能和存儲功能。它們使用FPGA邏輯資源實現觸發電路,使用FPGA存儲模塊實現存儲功能。它們使用JTAG配置內核操作,并用來把捕獲的數據傳送到PC上進行查看。

由于嵌入式邏輯分析儀使用內部FPGA資源,因此其通常用于大型FPGA,這些大型FPGA可以更好地消化插入內核帶來的開銷。一般來說,用戶希望內核占用的FPGA邏輯資源不超過可用資源的5%。

與任何調試方法一樣,還要知道這種方法存在的部分矛盾。

針腳與內部資源

嵌入邏輯分析儀內核不使用額外的測試針腳,因為它通過現有的JTAG針腳訪問內核。這意味著即使設計受到FPGA針腳限制,您仍可以使用這種方法。矛盾在于,它使用的內部FPGA邏輯資源和存儲模塊可以用來實現設計。此外,由于使用片內內存存儲捕獲的數據,因此內存深度一般相對較淺。

探測與運行模式

嵌入式邏輯分析儀核心的探測非常簡單。它使用現有的JTAG針腳,因此不必擔心怎樣把外部邏輯分析儀連接到系統上。矛盾在于,盡管嵌入式邏輯分析儀可以查看FPGA操作,但沒有一種方式把這些信息與電路板級或系統級信息時間關聯起來。而把FPGA內部的信號與FPGA外部的信號關聯起來對解決最棘手的調試挑戰至關重要。在分析方法上,嵌入式邏輯分析儀只能進行狀態分析。

成本與靈活性

大多數FP

GA廠商提供了嵌入式邏輯分析儀內核,而其價格要低于全功能外部邏輯分析儀。雖然用戶希望更多的功能,但嵌入式邏輯分析儀內核的功能無論從通用性,分析方式,觸發能力,還是從存儲和分析能力都弱于全功能外部邏輯分析儀,而用戶通常需要這些功能,來捕獲和分析棘手的調試挑戰。例如,嵌入式邏輯分析儀只能在狀態模式下操作,它們捕獲與FPGA設計中已有的指定時鐘同步的數據,因此不能提供精確的信號定時關系。

外部邏輯分析儀

由于嵌入式邏輯分析儀方法存在的部分限制,許多FPGA設計人員已經采用外部邏輯分析儀方法,來利用FPGA的靈活性和外部邏輯分析儀的處理能力,如泰克TLA系列邏輯分析儀。

在這種方法中,感興趣的內部信號路由到FPGA沒有使用的針腳上,然后連接到邏輯分析儀上。這種方法提供了非常深的內存,適合調試那種出現故障和實際導致該故障的原因在時間上相距很遠的問題;對于需要采集大量數據進行后期分析的設計人員也非常必要。另外它還可以把內部FPGA信號與電路系統中的其它活動時間關聯起來。

與嵌入式邏輯分析儀方法一樣,也需要考慮許多矛盾。

針腳與內部資源

外部邏輯分析儀方法采用非常少的邏輯資源,不使用FPGA內存資源。它釋放了這些資源,來實現所需功能。現在的矛盾在于,必需增加專用于調試的針腳數量,而很明顯,設計要使用這些針腳。

探測與工作模式

外部邏輯分析儀探測要比嵌入式邏輯分析儀方法要求的探測復雜一些。必需確定怎樣使用邏輯分析儀探頭探測FPGA內部信號,而不能使用電路板上已有的JTAG連接器。最簡便的方式是在電路板中增加一個測試連接器,這可以簡便地把FPGA信號與系統中的其它信號關聯起來。

成本與靈活性

盡管外部邏輯分析儀的購買價格確實要高于嵌入式邏輯分析儀,但使用外部邏輯分析儀可以解決更加廣泛的問題。邏輯分析儀不僅可以用于FPGA調試,還可以用來解決其它數字設計挑戰,它被公認為進行通用數字系統硬件調試的最佳工具。外部邏輯分析儀能夠實現更加靈活的采集模式和觸發功能。通過外部邏輯分析儀,可以設置最多16個不同的觸發狀態(每一個狀態含有16個條件判斷分支),每一個通道提供256M的內存,并且可以在定時分析模式下以高達125 ps的分辨率(8GS/s采樣)捕獲數據。

選擇合適的FPGA調試方法

上述兩種方法都可以使用,采用哪種方法要視具體情況而定。挑戰在于確定哪種方法更適合您的設計。用戶可以問自己下面的問題:

預計有哪些問題?

如果您認為問題僅限于FPGA內部的功能性問題,那么使用嵌入式邏輯分析儀可以提供要求的所有調試功能。但是,如果預計有更多的調試問題,要求檢驗定時余量、把內部FPGA活動與電路板上的其它活動關聯起來、或要求更強大的觸發功能,那么使用外部邏輯分析儀更適合滿足調試需求。

當FPGA芯片針腳包含超過200M的高速總線,例如集成內存控制器的DDRI、DDRII內存總線,以及集成高速SerDes的高速串行I/O總線,信號完整性測試是保證設計成功的基礎。在本文的后半部分會介紹主流的測試工具和方法。

除狀態數據外,是否需要考察快速定時信息?

外部邏輯分析儀允許以高達125 ps的分辨率(8GS/s采樣)查看FPGA信號詳細的定時關系,這有助于檢驗設計中實際發生的事件,檢驗設計的定時余量。嵌入式邏輯分析儀只能捕獲與FPGA中已有的指定時鐘同步的數據。

需要捕獲多深的數據?

外部邏輯分析儀提供的采集內存更深。一般在嵌入式邏輯分析儀中,最大取樣深度設為128 kb,這一數字受到器件限制。而在外部邏輯分析儀中,可以捕獲最多256Mb樣點。這有助于查看和分析更多的問題及潛在原因,從而縮短調試時間。

設計中更多地受限于針腳還是受限于資源?

使用嵌入式邏輯分析儀不要求任何額外的輸出針腳,但必須使用內部FPGA資源,實現邏輯分析儀功能。使用外部邏輯分析儀要求使用額外的輸出針腳,但使用內部FPGA資源的需求達到最小(或消除了這種需求)。表1匯總了每種方法的相對優勢。

FPGAViewTM進行FPGA調試

FPGAView概述

外部邏輯分析儀方法有效利用FPGA的處理能力,并根據需要重新對設備配置,把感興趣的內部信號路由到通常很少的針腳上。這是一種非常有用的方法,但它也有一定的局限性:

—— 用戶每次需要查看一套不同的內部信號時,都必需改變設計(在RTL級或使用FPGA編輯器工具),把希望的信號組路由到調試針腳上。這不僅耗費時間,而且如果要求重新匯編設計,那么還會改變設計的定時,可能會隱藏需要解決的問題。

—— 當更改FPGA內部測試信號時,在外部邏輯分析儀上的被測信號名稱需要手工進行更新。

—— 一般來說,調試針腳數量很少,內部信號與調試針腳之間1:1的關系限制著設計查看能

力和洞察力。

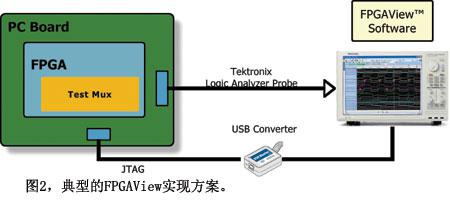

為克服這些局限性,出現了一種新的FPGA調試方法,它不僅提供了外部邏輯分析儀方法的所有優勢,還消除了主要局限性。FPGAView軟件在與泰克TLA系列邏輯分析儀配套使用時,為調試FPGA和周邊硬件電路提供了一個完整的解決方案(參見圖2)。

這種組合可以:

—— 時間關聯的查看FPGA內部活動和外部活動。

—— 迅速改變FPGA內部探點,而無需重新匯編設計。

—— 每個針腳監測多個內部信號。

—— 在TLA邏輯分析儀上自動更新切換的內部信號名稱。

此外,FPGAView可以在一臺設備中處理多個測試內核(適合監測不同的時鐘域),并可以在一個JTAG鏈上處理多臺FPGA設備。

[圖示內容:]

PC Board: PCB電路板

Test Mux: 測試復用器

Tektronix Logic Analyzer Probe: 泰克邏輯分析儀探頭

USB Converter: USB轉換器

FPGAView? Software: FPGAView?軟件

快速使用FPGAView

可以通過下面幾個簡單的步驟使用FPGAView:

第1步。 在設計中配置和插入相應的測試內核

第2步。 加載測試內核信息

第3步。 建立FPGA針腳與TLA邏輯分析儀通道的對應關系

第4步。 進行測量

下面幾節詳細介紹了每個步驟。

第1步。 插入內核

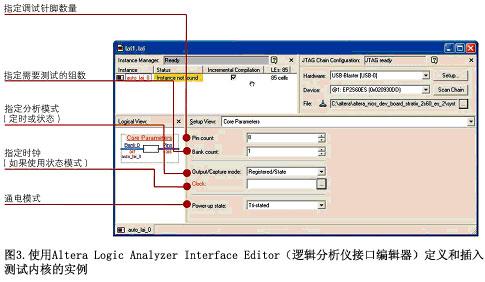

第一步是配置測試內核,把它插入到FPGA設計中。例如,在使用Altera或Xilinx器件時,可以使用FPGA開發工具提供的邏輯分析儀接口編輯器,創建最適合自己需求的測試核(參見圖3)。

[圖示內容:]

Specify number of debug pins: 指定調試針腳數量

Specify Number of Banks: 指定需要測試的組數

Specify Mode: 指定分析模式(定時或狀態)

Specify Clock (if using State Mode): 指定時鐘(如果使用狀態模式)

Power-Up Mode: 通電模式

對大多數測試內核,可以指定下述參數:

Pin Count(針腳數量) :表示希望專用于邏輯分析儀接口的針腳數量。

Bank Count(組數) :表示希望映射到每個針腳上的內部信號數量。

Output/Capture Mode(輸出/捕獲模式):選擇希望執行的采集類型。可以選擇Combination/Timing(組合邏輯/定時模式) 或Registered/State (寄存器/狀態模式)。

Clock(時鐘) :如果用戶選擇了Registered/State(寄存器/狀態)的捕獲模式,這一選項允許選擇測試內核的取樣時鐘。

Power-Up State(通電狀態) :這個參數允許指明指定用于邏輯分析儀接口的針腳的通電狀態。

第2步。 把測試內核信息加載到FPGAView中

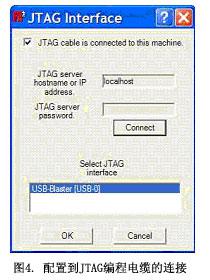

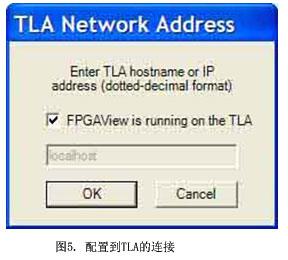

從FPGAView軟件窗口中,可以與JTAG編程電纜建立連接(參見圖4),并且連接到TLA系列邏輯分析儀(TLA邏輯分析儀使用WINDOWS平臺)或PC工作站上(參見圖5)。

在使用ALTERA FPGA芯片時,按Open (打開)工具條按鈕,調出一個文件瀏覽器,選擇Quartus II LAI Editor軟件以前生成的邏輯分析儀接口(.lai)文件。這樣就加載了與LAI核心有關的所有信息,包括每一組的信號數量、組數和信號名稱,另外如果設備中的LAI內核多于一個,那么還包括每個LAI內核的信息。

第3步。

把FPGA針腳映射到邏輯分析儀上

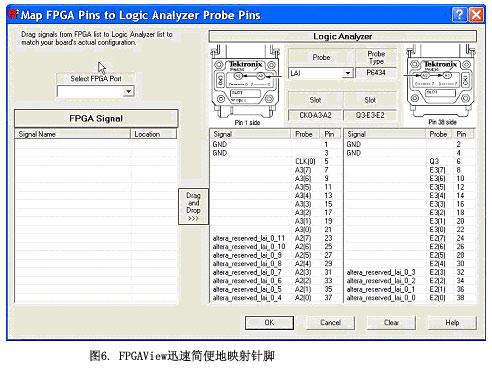

下一步是映射FPGA針腳和TLA邏輯分析儀探頭之間的物理連接。FPGAView可以自動更新邏輯分析儀上顯示的信號名稱,與測試內核當前監測的信號相匹配。

為此,簡單地點擊Probes (探頭)按鈕,將出現一個拖放窗口,把測試內核輸出信號名稱與邏輯分析儀上的相應通道連接起來(參見圖6)。。對某條目標連接,這個通道分配過程只需一次。

第4步。 進行測量

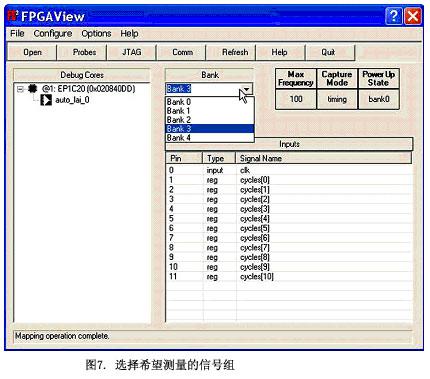

使用Bank(組)列表下拉菜單,選擇想要測量的組。一旦選擇了組,FPGAView會通過JTAG接口與FPGA通信,并配置測試內核,以便選擇希望的組。

FPGAView還將這些通道名稱通過對TLA系列邏輯分析儀的控制進行自動分配,從而可以簡便地理解測量結果。為測量不同的一套內部信號,用戶只需選擇不同的信號組(參見圖7)。全功能TLA系列邏輯分析儀會自動把這些FPGA信號與系統中的其它信號關聯起來(參見圖8)。

在TLA邏輯分析儀中,針對設計人員關心的各種時間信息,提供了業內獨有的定時參數自動測量功能,通過鼠標簡單的拖放操作,能夠得到周期、頻率、占空比、脈沖寬度、通道/通

道延遲、邊沿計數、周期計數、違規計數、周期抖動、以及周期間抖動等信息。

小結

通過在FPGA系統和設計與應用階段認真考慮調試需求,可以選擇相應的調試方法,既簡化調試流程,也有助于節約時間。嵌入式邏輯分析儀和外部邏輯分析儀這兩種方法各有優缺點,但FPGAView等新方法進一步提高了外部邏輯分析儀方法的吸引力。能夠快速方便地移動探點,而不需重新匯編設計,同時能夠把內部FPGA信號活動與電路板級信號關聯起來,直接決定著能否滿足產品開發周期的要求。

-

FPGA

+關注

關注

1629文章

21729瀏覽量

602997 -

嵌入式

+關注

關注

5082文章

19104瀏覽量

304811 -

Xilinx

+關注

關注

71文章

2167瀏覽量

121304

發布評論請先 登錄

相關推薦

有助于提高FPGA調試效率的技術與問題分析

有助于提高FPGA調試效率的技術與問題分析

評論