隨著數字通信和工業控制領域的高速發展,要求專用集成電路(ASIC)的功能越來越強,功耗越來越低,生產周期越來越短,這些都對芯片設計提出了巨大的挑戰,傳統的芯片設計方法已經不能適應復雜的應用需求了。SoC(System on a Chip)以其高集成度,低功耗等優點越來越受歡迎。開發人員不必從單個邏輯門開始去設計ASIC,而是應用己有IC芯片的功能模塊,稱為核(core),或知識產權(IP)宏單元進行快速設計,效率大為提高。CPU 的IP核是SoC技術的核心,開發出具有自主知識產權的CPU IP核對我國在電子技術方面跟上世界先進的步伐,提高信息產業在世界上的核心竟爭力有重大意義。

精簡指令集計算機RISC(Reduced Instruction Set Computer)是針對復雜指令集計算機CISC(Complex Instruction Set Computer)提出的,具備如下特征1)一個有限的簡單的指令集; 2)強調寄存器的使用或CPU配備大量的能用的寄存器;3)強調對指令流水線的使用。

2 CPU IP核的組成

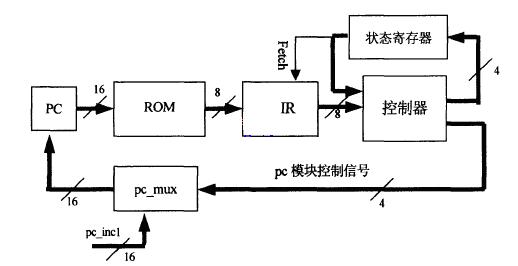

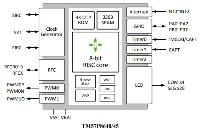

盡管各種CPU的性能指標和結構細節不同,但所要完成的基本功能相同,從整體上可分為八個基本的部件:時鐘發生器、指令寄存器、累加器、RISC CPU算術邏輯運算單元、數據控制器、狀態控制器、程序控制器、程序計數器、地址多路器。狀態控制器負責控制每一個部件之間的相互操作關系,具體的結構和邏輯關系如圖1所示。

時鐘發生器利用外部時鐘信號,經過分頻生成一系列時鐘信號給CPU中的各個部件使用。為了保證分頻后信號的跳變性能,在設計中采用了同步狀態機的方法。

指令寄存器在觸發時鐘clk1的正跳變觸發下,將數據總線送來的指令存入寄存器中。數據總線分時復用傳遞數據和指令,由狀態控制器的load_ir信號負責判別。load_ir信號通過使能信號ena口線輸入到指令寄存器。復位后,指令寄存器被清為零。每條指令為兩個字節16位,高3位是操作碼,低13位是地址線。CPU的地址總線為是13位,位尋址空間為8K 字節。本設計的數據總線是8位,每條指令取兩次,每次由變量state控制。

累加器用于存放當前的運算結果,是雙目運算中的一個數據。復位后,累加器的值為零。當累加器通過使能信號ena 口線收到來自CPU狀態控制器load_acc 信號后,在clk1時鐘正跳沿時就接收來自數據總線的數據。

圖1 CPU結構圖

算術邏輯運算單元根據輸入的不同的操作碼分別實現相應的加、與、異或、跳轉等基本運算。

數據控制器其作用是控制累加器的數據輸出,由于數據總線是各種操作傳送數據的公共通道,分時復用,有時傳輸指令,有時要傳送數據。其余時候,數據總線應呈高阻態,以允許其他部件使用。所以,任何部件向總線上輸出數據時,都需要一個控制信號的,而此控制信號的啟、停則由CPU狀態控制器輸出的各信號控制決定。控制信號datactl_ena決定何時輸出累加器中的數據。

地址多路器用于輸出的地址是PC(程序計數器)地址還是數據/端口地址。每個指令周期的前4個時鐘周期用于從ROM中讀取指令,輸出的應是PC地址,后4個時鐘周期用于對RAM或端口的讀寫,該地址由指令給出,地址的選擇輸出信號由時鐘信號的8分頻信號fecth提供。

程序計數器用于提供指令地址,以便讀取指令,指令按地址順序存放在存儲器中,有兩種途徑可形成指令地址,一是順序執行程序的情況,二是執行JMP指令后,獲得新的指令地址。

狀態機控制器接受復位信號RST,當RST有效時,能通過信號ena使其為0 ,輸入到狀態機中以停止狀態機的工作。狀態機是CPU 的控制核心,用于產生一系列的控制信號,啟動或停止某些部件,CPU何時進行讀指令來讀寫I/O端口及RAM區等操作,都是由狀態機來控制的。狀態機的當前狀態,由變量state記錄,state的值就是當前這個指令周期中已經過的時鐘數。指令周期是由8 個時鐘組成,每個時鐘都要完成固定的操作。

3 系統時序

RISC CPU的復位和啟動操作是通過rst引腳的信號觸發執行的,當rst信號一進入高電平,RISC CPU就會結束現行操作,并且只要rst停留在高電平狀態,CPU就維持在復位狀態,CPU各狀態寄存器都設為無效狀態。當信號rst回到低電平,接著到來的第一個fetch 上升沿將啟動RISC CPU開始工作,從ROM的000處的開始讀取指令并 執行相應的操作。

讀指令時序,每個指令的前3個時鐘周期用于讀指令,4~6周期讀信號rd有效,第7 個周期讀信號無效,第8個周期地址總線輸出PC地址,為下一個指令作準備。

寫指令時序,每個指令的第3.5個時鐘周期建立寫地址,第四個周期輸出數據,第5個時鐘周期輸出寫信號,第6個時鐘結束,第7.5個時鐘周期輸出為PC地址,為下個指令做準備。

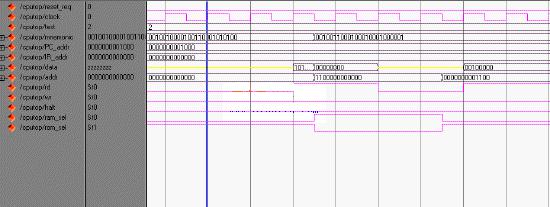

如圖2 所示,這是ModelSim SE6.0進行波形仿真的結果。

4 微處理器指令

數據處理指令:數據處理指令完成寄存器中數據的算術和邏輯操作,其他指令只是傳送數據和控制程序執行的順序.因此,數據處理指令是唯一可以修改數據值的指令,數據處理指令一般需兩個源操作數,產生單個結果.所有的操作數都是8位寬,或者來自寄存器,或者來自指令中定義的立即數.每一個源操作數寄存器和結果寄存器都在指令中獨立的指定。

圖2 讀寫指令時序

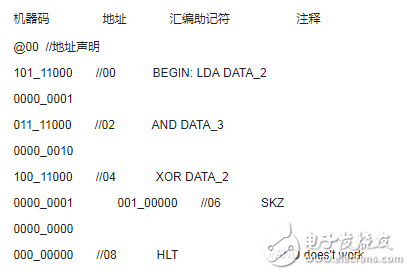

數據傳送和控制轉移類指令:共有17條,不包括按布爾變量控制程序轉移的指令。其中有全存儲空間的長調用、長轉移和按2KB分塊的程序空間內的絕對調用和絕對轉移;全空間的長度相對轉移及一頁范圍內的短相對轉移;還有條件轉移指令。這類指令用到的助記符有ACALL, AJMP, LCALL, LJMP, SJMP, M, JZ, JNZ, ONE,DJNZ。控制轉移類指令主要用來修改1x指針從而達到對程序流的控制,所用到的寄存器主要有sp, pc, ir等寄存器。指令由操作碼和操作數組成,取指令電路的目的就是把指令碼和操作數分開。組成電路由如圖3所示。取指令電路由程序指針,程序指針解析模塊、ROM, IR(指令寄存器),控制器狀態寄存器組成。取指令指令的過程如下:PC指針的值經過pc_mux模塊賦值,把ROM中的指令取出來,送到指令寄存器的數據輸入口。指令寄存器受狀態寄存器的控制,當取指令信號有效時,ROM中的指令碼被保存在指令寄存器中,然后經控制器譯碼,產生控制信號,對PC指針的增量加以控制取出下一條指令。

?

6 調試

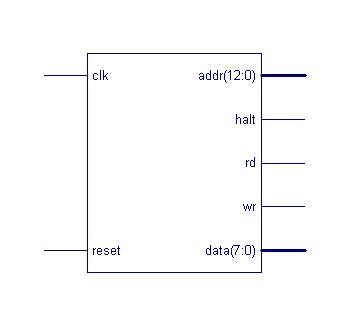

最基本的調試手段 是基于FPGA 廠商提供的開發和仿真環境,用硬件描述語言編寫TESTBENCH,構成一個最小運行環境。TESTBENCH產生對目標軟核的激勵,同時記錄軟核的輸出,和預期值進行比對,可以確定核的設計錯誤。這種方法的好處是實現容易,結果準確,但硬件描述語言編碼量較大。為了仿真結果的準確性,無論功能仿真還是時序仿真,仿真的步長都不能太小,結果導致整個系統仿真時間太長。本設計中先對RISC CPU的各個子模塊進行了分別綜合,檢查正確性,如果發現錯誤可以在較小的范圍內來檢查并驗證。子模塊綜合完畢后,把要綜合的RISC CPU的模塊與外圍器件以及測試模塊分離出來組成一個大模塊,綜合后的的RISC CPU模塊如圖4所示,這是Xilinx ISE7.1 所綜合生成的技術原理圖。

綜合的結果只是通用的門級網表,只是一些與、或、非門的邏輯關系,和芯片實際的配置情況還有差距。此時應該使用FPGA/CPLD廠商提供的實現與布局布線工具,根據所選芯片的型號,進行芯片內部功能單元的實際連接與映射。這種實現與布局布線工具一般要選用所選器件的生產商開發的工具,因為只有生產者最了解器件內部的結構,如在ISE的集成環境中完成實現與布局布線的工具是Flow Engine。

圖4 CPU技術原理圖

STA(Static Timing Analysis)靜態時序分析,完成FPGA設計時必須的一個步驟。在FPGA加約束、綜合、布局布線后,在ISE中可以運行Timing Analyzer生成詳細的時序報告,本設計中Minimum period: 12.032ns (Maximum Frequency: 83.112MHz),Minimum input arrival time before clock: 6.479ns,Maximum output required time after clock: 9.767ns。然后,設計人員檢查時序報告,根據工具的提示找出不滿足Setup/Hold time的路徑,以及不符合約束的路徑,進行修改保證數據能被正確的采樣。在后仿真中將布局布線的時延反標到設計中去,使仿真既包含門延時,又包含線延時信息。這種后仿真是最準確的仿真,能真實地反映芯片的實際工作情況。

7 結 論

復雜的RISC CPU設計是一個從抽象到具體的過程,本文根據FPGA的結構特點,圍繞在FPGA上設計實現八位微處理器軟核設計方法進行探討,研究了片上系統的設計方法和設計復用技術,并給出了指令集和其調試方法,提出了一種基于FPGA的微處理器的IP的設計方法。本文作者創新點是:根據Spartan II 的內部結構,在編碼階段實現了地址和數據的優化,實現階段對內部布局布線進行重新配置,設計實現的微處理器僅占用78個slices,1個Block RAM,在10萬門的芯片實現,占用6%的資源。

:

-

FPGA

+關注

關注

1629文章

21729瀏覽量

603044 -

cpu

+關注

關注

68文章

10855瀏覽量

211606 -

RISC

+關注

關注

6文章

462瀏覽量

83714

發布評論請先 登錄

相關推薦

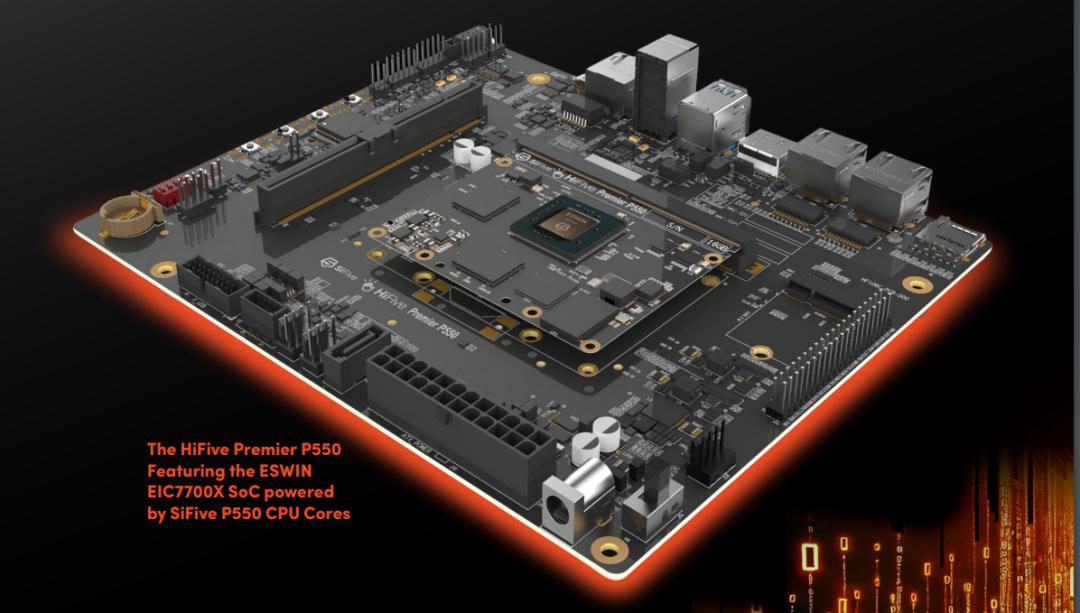

SiFive 推出高性能 Risc-V CPU 開發板 HiFive Premier P550

risc-v與esp32架構對比分析

對INA226的配置寄存器0x00回讀,低八位始終為0xFF,為什么?

Imagination CPU 系列研討會 | RISC-V 平臺的性能分析和調試

電磁軌跡預測分析系統設計方案

adxl359的offset寄存器是16位,再進行設置時只有高八位生效,低八位不生效,為什么?

瑞薩電子推出采用自研RISC-V CPU內核的通用32位MCU

瑞薩率先在業內推出采用自研CPU內核的通用32位RISC-V MCU

瑞薩電子推出采用自研CPU內核的通用32位RISC-V微控制器

瑞薩推出采用自研CPU內核的通用32位RISC-V MCU 加強RISC-V生態系統布局

芯來科技正式發布基于RISC-V處理器的HSM子系統解決方案

Imagination:RISC-V CPU的重要力量

基于八位RISC 的CPU設計方案分析

基于八位RISC 的CPU設計方案分析

評論