1.引言

隨著集成電路復雜度越來越高,測試開銷在電路和系統總開銷中所占的比例不斷上升,測試方法的研究顯得非常突出。目前在測試源的劃分上可以采用內建自測試或片外測試。內建自測試把測試源和被測電路都集成在芯片的內部,對于目前SOC級的芯片測試如果采用內建自測試則付出的硬件面積開銷則是很大的,同時也增加了芯片設計的難度:因此片外測試便成為目前被普遍看好的方法。由于FPGA具有可重構的靈活性,利用FPGA來作為測試源實現片外測試就是一種非常有效的手段。

由于偽隨機模式測試只需要有限個數的輸入向量便可達到很高的故障覆蓋率因而在作為測試源設計中得到了廣泛應用,采用CPLD來實現偽隨機測試序列生成器的設計[1]為提供了電子系統測試信號提供了一種簡單的方法。在可測試設計中同時也要考慮低功耗的問題,考慮功耗的主要原因是在測試模式下電路的功耗要遠遠高于正常模式。因為采用完全的單輸入跳變測試序列所需要的測試序列長度太長而沒有實際應用價值,這樣獲得準單輸入跳變測試序列的測試生成器一直是低功耗設計中一種非常有效的方法,本文針對一種產生準單輸入跳變測試序列的低功耗測試生成器的缺點提出了改進設計方案,并且利用EDA技術在FPGA芯片上進行了設計實現。

2.低功耗測試生成器的設計

本文給出的低功耗測試產生器改進方案是在文獻[2]的測試產生器的基礎上再利用ROM中的種子對LFSR的再播種實現的。因為原有低功耗測試產生器是以LFSR為基礎的,其產生的準單輸入跳變測試序列只能覆蓋被測電路中的易測故障;要達到1 0 0%的故障覆蓋率,就必須對被測電路中剩余的抗偽隨機故障和難測故障采用少量的確定模式測試集來覆蓋;折疊集[3]就是其中一種有效的確定模式測試集,利用存儲在ROM中的折疊種子對LFSR多次再播種就可以產生所需要的折疊測試序列。由于在折疊集內部各個測試向量之間由于存在相關性,按照一定規律排序后就可以將南一個折疊種子產生的折疊集變換成單輸入跳變測試序列:這樣由不同的折疊種子產生的測試向量序列就是準單輸入跳變測試序列。

設LFSR的級數為n,開始由LFSR產生一定長度的準單輸入跳變測試序列,具體產生原理和改進前的低功耗測試產生器[2]原理一樣;然后開始由折疊控制器裝入一個折疊種子,然后產生單輸入跳變測試序列,折疊控制器由圖1中的計數器與解碼器組成,解碼器完成對由一一個折疊種子產:生的原始折疊集的排序產生單輸入跳變測試序列。然后再裝入下一個折疊種子,折疊控制器接著產生下一個單輸入跳變測試序列,這樣直到所有的折疊種子都被裝入為止。整個的由不同的折疊種子產生的測試向量序列就是準單輸入跳變測試序列。

3.FPGA的設計實現

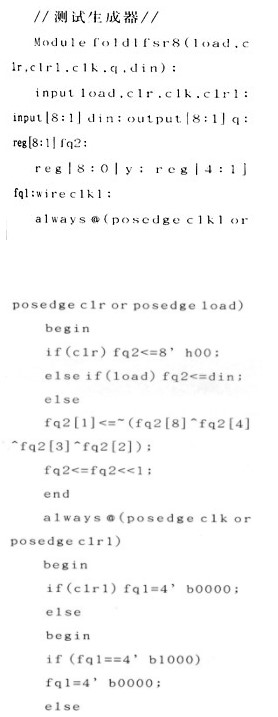

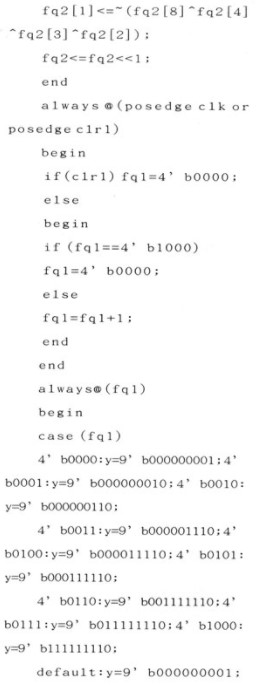

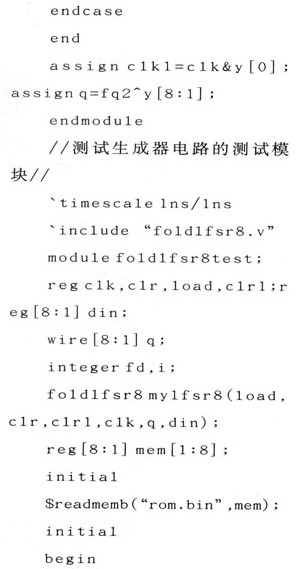

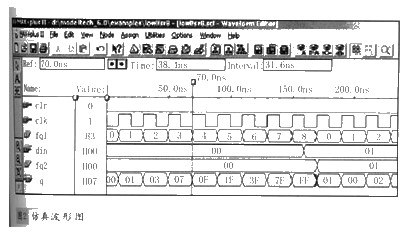

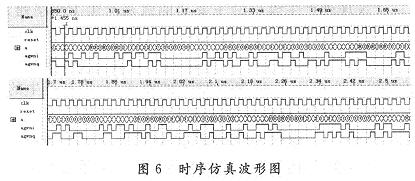

在FPGA的設計輸入時采用Verilog HDL語言來設汁所要求的測試生成器模塊,我們以n=8的LFSR為例,以下給出了設計源碼。通過使用MaxplusII1 0.2軟件在ALTERA公司的FPGA芯片FLEX EPF1OK 10LC84-4進行了仿真,圖2給出了仿真波形,驗證了設計的正確性。

-

FPGA

+關注

關注

1629文章

21734瀏覽量

603099 -

cpld

+關注

關注

32文章

1248瀏覽量

169342 -

eda

+關注

關注

71文章

2757瀏覽量

173224

發布評論請先 登錄

相關推薦

如何在Xilinx創建序列生成器

榮小菜補鈣記第52期:報文序列生成器1

榮小菜補鈣記第54期:報文序列生成器3

python生成器

漢語句子聯想生成器

基于FPGA的AGWN信號生成器

利用EDA技術在FPGA芯片上實現了準單輸入調變序列生成器的設計

利用EDA技術在FPGA芯片上實現了準單輸入調變序列生成器的設計

評論