互聯(lián)網(wǎng)的繁榮和無線通訊及存儲行業(yè)的發(fā)展使得實時數(shù)據(jù)通訊量成指數(shù)級增長。數(shù)據(jù)通訊量的急劇增加使系統(tǒng)可用性顯得更加關(guān)鍵,因為系統(tǒng)即使停一秒鐘也意味著將產(chǎn)生巨大的影響,并將減少運營商的收入。為了使系統(tǒng)的宕機時間為零,可以將系統(tǒng)設(shè)計成可熱插拔的形式。熱插拔是指系統(tǒng)在正常運行時可以從背板上插入或取出電路板,而不會對主系統(tǒng)的正常工作產(chǎn)生影響。熱插拔也稱為熱切換(hot swap)或熱插入。

快速發(fā)展的半導(dǎo)體工藝技術(shù)使支持熱插拔的設(shè)計更趨復(fù)雜,因為工藝尺寸越來越小,IC的工作電壓也越來越低,而且不同的I/O標(biāo)準(zhǔn)需要不同的電平。當(dāng)前的PCB板上大多都有工作電壓分別為5.0V、3.3V、2.5V、1.8V、1.5V和1.2V的器件,要使系統(tǒng)能正常工作必須保證每個器件正確的加電順序,然而這通常具有一定難度。

由于FPGA能提供更多邏輯、更高復(fù)雜程度以及成本降低,在系統(tǒng)級可編程芯片(SoPC)應(yīng)用中,可編程邏輯器件(PLD)在市場上得到了廣泛的認(rèn)同。FPGA已經(jīng)融入到通訊、網(wǎng)絡(luò)和存儲應(yīng)用的數(shù)據(jù)通道中。由于熱插拔對保證系統(tǒng)的不間斷工作很重要,因此這些系統(tǒng)在使用PLD時,也要求可以進行熱插拔。

要支持熱插拔,PLD器件的設(shè)計必須滿足以下要求:

1. 器件在加電以前可以被驅(qū)動,并且不能對器件本身造成損害。

2. 在加電以前及加電的過程中不能排斥器件。

3. 外部輸入到器件I/O管腳的信號不能通過器件的內(nèi)部通道對器件的VCCIO和VCCINT電源產(chǎn)生激勵。

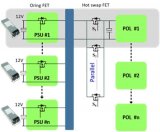

PLD熱插拔的基本原理是在加電(VCCINT或任何VCCIO電源)或關(guān)電過程中關(guān)斷輸出緩沖。當(dāng)VCCINT或VCCIO低于閾值電壓時,熱插拔電路都會產(chǎn)生一個內(nèi)部的HOTSCKT信號,HOTSCKT信號將關(guān)斷輸出緩沖,以便確保沒有直流電流通過管腳(不包括通過弱上拉電阻的漏電流)(見圖1)。

當(dāng)VCC非常緩慢地升高時,在發(fā)出加電復(fù)位(POR)信號和FPGA器件配置完成后,VCC電壓甚至還相對較低。如果熱插拔電路在管腳CONF_DONE、nSTATUS和nCEO上實現(xiàn)時,它也不會有響應(yīng),因為在這樣低的VCC電壓下,輸出緩沖不會從熱插拔電路設(shè)定的狀態(tài)翻轉(zhuǎn)。要解決這個問題,需要去除這些管腳的熱插拔特性,確保管腳CONF_DONE、nSTATUS及nCEO在配置的過程中可以工作。

圖1所示是Altera PLD熱插拔的實現(xiàn)原理框圖:POR電路監(jiān)測VCCINT的電壓,并保持I/O管腳的三態(tài),直至器件進入用戶模式;I/O管腳到VCCIO的弱上拉電阻防止I/O管腳的電壓漂移;電壓誤差控制電路允許I/O腳在VCCIO和/或VCCINT加電前被驅(qū)動,同時還防止器件不在用戶模式時I/O腳被排斥。熱插拔電路還可以在器件加電以前阻止I/O腳外部信號加到內(nèi)部VCCIO和VCCINT上來。

圖2是FPGA器件I/O緩沖器晶體管級圖示。Stratix、Stratix GX及Cyclone FPGA系列I/O腳的CMOS輸出驅(qū)動器提供內(nèi)在的靜電釋放(ESD)保護。對于ESD電壓的沖擊需要考慮兩種情形:正電壓沖擊和負(fù)電壓沖擊。當(dāng)I/O管腳上具有一個正電壓時,由于ESD充電事件而發(fā)生ESD沖擊。這將造成N溝道漏極的N+(漏極)/P襯底之間的結(jié)擊穿,然后N+(漏極)/P-襯底/N+ (源極)內(nèi)在雙極晶體管導(dǎo)通,這樣將ESD電流從I/O腳到GND釋放。當(dāng)I/O腳的電壓小于-0.7V(0.7V為二極管的壓降)受到負(fù)的ESD沖擊時,內(nèi)部的P-襯底/N+漏極二極管為正偏壓。因此建立了從GND到I/O管腳釋放ESD電流的通道。

最新的FPGA器件嵌入了高速串行收發(fā)器以滿足通訊、網(wǎng)絡(luò)和存儲設(shè)備的要求,這些設(shè)備在它們的背板結(jié)構(gòu)中采用了串行數(shù)據(jù)傳輸技術(shù)。嵌入收發(fā)器支持熱插拔的特點很關(guān)鍵,這樣在熱切換的過程中背板才不會對數(shù)據(jù)連接產(chǎn)生影響。Stratix GX系列FPGA上都具有高速片上串行接收器,它們設(shè)計成支持熱插拔的形式。

對于不需要熱插拔的多電壓系統(tǒng),PLD的熱插拔和上電順序保護功能依然很重要。在這些系統(tǒng)中,由于采用穩(wěn)壓器來提供不同的電壓,因此難于預(yù)測加電順序,要求預(yù)定加電順序的器件將可能不能正常工作。

由于通常PLD的功能不會受系統(tǒng)加電順序的影響,因此PLD片上熱插拔特征可以用來緩解多電壓系統(tǒng)設(shè)計中加電的順序問題。這對于那些復(fù)雜的多電壓系統(tǒng)很重要,在這些系統(tǒng)中可以采用例如MAX 3000A和MAX 7000AE這些CPLD器件來控制其它器件的加電順序。

通過采用嵌入式的專門電路,先進的PLD能夠為那些需要多重電壓和熱切換功能的應(yīng)用提供簡單的支持和加電順序保護。對于需要熱插拔的系統(tǒng),熱插拔PLD的可編程I/O管腳不會影響與PLD連接的系統(tǒng)總線。此外,設(shè)計工程師在利用熱插拔PLD時,不必考慮不同的加電順序是否會影響PLD的正常功能。

-

FPGA

+關(guān)注

關(guān)注

1629文章

21729瀏覽量

603044 -

驅(qū)動器

+關(guān)注

關(guān)注

52文章

8228瀏覽量

146269 -

PLD

+關(guān)注

關(guān)注

6文章

224瀏覽量

59380

發(fā)布評論請先 登錄

相關(guān)推薦

面向熱插拔應(yīng)用的MOSFET

熱插拔是什么?熱插拔有哪些特點?

即插即用和熱插拔的區(qū)別

示波器的計算功能分析熱插拔電路

如何對BMS單元連接進行熱插拔

空間受限應(yīng)用中的PMBus熱插拔電路基礎(chǔ)介紹

理想二極管和熱插拔功能的實現(xiàn)

基于TPS2491的熱插拔保護電路設(shè)計

使用NCP45521進行熱插拔開關(guān)的典型應(yīng)用熱插拔電路

LTC4218演示電路-采用并聯(lián)MOSFET的12V 100A熱插拔設(shè)計

在大電流熱插拔應(yīng)用中通過有保證的SOA實現(xiàn)低導(dǎo)通電阻

基于IC的熱插拔電路保護的優(yōu)勢

采用PLD器件實現(xiàn)電路中的熱插拔設(shè)計

采用PLD器件實現(xiàn)電路中的熱插拔設(shè)計

評論