線性調(diào)頻信號可以獲得較大的壓縮比,有著良好的距離分辨率和徑向速度分辨率,所以線性調(diào)頻信號作為雷達(dá)系統(tǒng)中一種常用的脈沖壓縮信號,已經(jīng)廣泛應(yīng)用于高分辨率雷達(dá)領(lǐng)域。直接數(shù)字頻率合成(Digital DirectFrequency Synthesis,DDS)技術(shù)是解決這一問題的最好辦法。在雷達(dá)系統(tǒng)中采用DDS技術(shù)可以靈活地產(chǎn)生不同載波頻率、不同脈沖寬度以及不同脈沖重復(fù)頻率等參數(shù)構(gòu)成的信號,為雷達(dá)系統(tǒng)的設(shè)計(jì)者提供了全新的思路。

1設(shè)計(jì)思路

利用專用DDS芯片是目前比較流行的信號產(chǎn)生方法。專用DDS芯片把所有功能集中在一塊芯片上,需要設(shè)計(jì)者以此為平臺進(jìn)行開發(fā)。而基于FPGA的DDS軟件編程則根據(jù)DDS技術(shù)的基本原理,充分利用了FPGA作為大規(guī)模芯片的資源優(yōu)勢和高速運(yùn)算能力,除了能產(chǎn)生專用DDS芯片所具備的單頻連續(xù)波、非連續(xù)波、各種形式的線性調(diào)頻信號以外,還可以借助FPGA的龐大的資源優(yōu)勢和內(nèi)部存儲(chǔ)器,使非線性調(diào)頻等更復(fù)雜的信號更容易實(shí)現(xiàn)。

2硬件系統(tǒng)的構(gòu)成

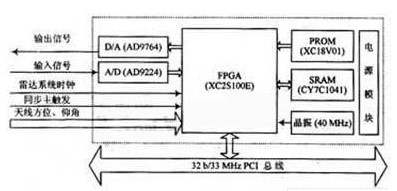

在具體實(shí)現(xiàn)過程中主要采用一塊基于FPGA的雷達(dá)信號處理卡,既可以采集來自雷達(dá)接收機(jī)的中頻、視頻信號并對其進(jìn)行數(shù)字信號處理,又可以自身模擬產(chǎn)生雷達(dá)中頻、視頻信號進(jìn)行數(shù)字信號處理或不處理直接送往雷達(dá)信號處理機(jī)。雷達(dá)信號處理卡的硬件電路結(jié)構(gòu)框圖如圖1所示。

FPGA采用的是Xilinx公司的10萬門FPGA芯片XC2S100E,其配置芯片為Xilinx公司的1 Mb容量PROM芯片XC18V01,以主動(dòng)串行方式對FPGA進(jìn)行上電配置。A/D,D/A分別為ADI公司12位高速模數(shù)轉(zhuǎn)換芯片AD9224與14位高速數(shù)模轉(zhuǎn)換芯片AD9764。SRAM采用Cypress公司的256k×16 bSRAM芯片CY7C1041。

結(jié)合本處理卡的結(jié)構(gòu)特點(diǎn),硬件上采用FPGA與高速D/A方案產(chǎn)生線性調(diào)頻信號。在FPGA內(nèi)部實(shí)現(xiàn)DDS電路,F(xiàn)PGA輸出全數(shù)字的線性調(diào)頻信號送往高速D/A得到最終的模擬線性調(diào)頻信號。由于本處理卡采用PCI總線結(jié)構(gòu),因此可通過計(jì)算機(jī)實(shí)時(shí)修改線性調(diào)頻信號的參數(shù)設(shè)置,改善了人機(jī)接口,提高了系統(tǒng)的靈活性。

3 FPGA軟件編程實(shí)現(xiàn)線性調(diào)頻信號

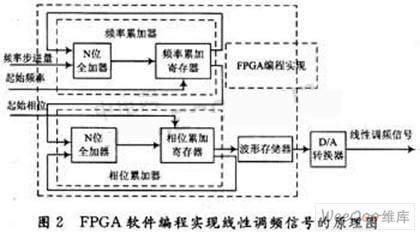

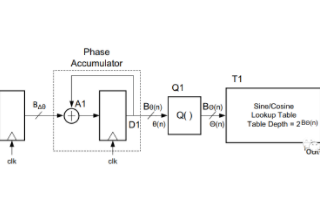

DDS芯片電路產(chǎn)生的是固定頻率的正弦波信號,信號頻率受相位增量△Phase控制,若要產(chǎn)生線性調(diào)頻信號,則必須實(shí)時(shí)改變△Phase,使△Phase根據(jù)頻率步進(jìn)量fstep而線性變化。因此基于FPGA軟件編程實(shí)現(xiàn)線性調(diào)頻信號時(shí),需要在FPGA內(nèi)部實(shí)現(xiàn)頻率累加器、相位累加器、正弦波形ROM存儲(chǔ)器等電路,F(xiàn)PGA軟件編程實(shí)現(xiàn)線性調(diào)頻信號的原理圖如圖2所示。

在產(chǎn)生線性調(diào)頻信號時(shí),每來一個(gè)時(shí)鐘脈沖,軟件編程控制頻率累加器產(chǎn)生線性增加的瞬時(shí)頻率,然后經(jīng)過相位累加器運(yùn)算輸出線性調(diào)頻信號的瞬時(shí)相位,以此相位值尋址正弦值存儲(chǔ)表,通過查表得到與相位值對應(yīng)的幅度量化值;在下一個(gè)周期來臨時(shí),頻率累加寄存器一方面將在上一時(shí)鐘周期作用后所產(chǎn)生的新的頻率數(shù)據(jù)反饋到頻率加法器的輸入端,以使頻率加法器繼續(xù)累加,頻率累加的瞬時(shí)值與上個(gè)周期相位累加器反饋到相位加法器輸入端的數(shù)據(jù)累加,然后再依此周期累加的相位值重新尋址正弦值存儲(chǔ)表,得到對應(yīng)的幅度量化值,依此循環(huán),幅度量化值經(jīng)過累加,并經(jīng)D/A轉(zhuǎn)換器得到連續(xù)的階梯波,經(jīng)低通濾波器濾除其中的高頻分量,最后即可得到所需線性調(diào)頻信號。

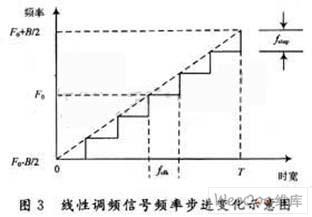

已知系統(tǒng)工作時(shí)鐘fclk、頻率累加器與相位累加器位數(shù)N,要產(chǎn)生中頻為F0、帶寬為B、時(shí)寬為T的線性調(diào)頻信號,其頻率步進(jìn)變化如圖3所示,在FPGA軟件編程時(shí)只需計(jì)算出起始頻率fstart和頻率步進(jìn)量fstep卸即可。

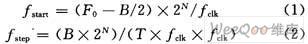

起始頻率fstart和頻率步進(jìn)量fstep的計(jì)算公式如式(1),式(2)所示,因?yàn)樵赩HDL語言中,數(shù)值的表示方法都是二進(jìn)制的,所以通過式(1),式(2)計(jì)算的結(jié)果都是二進(jìn)制的,是無量綱的。

經(jīng)過頻率累加器輸出的是嚴(yán)格線性增長的瞬時(shí)頻率。在實(shí)際過程中相位累加器的輸出是經(jīng)過相位截?cái)嘣龠M(jìn)行尋址,從而引入了一定的相位誤差,雖然這一誤差會(huì)影響到線性調(diào)頻信號的線性度,但是調(diào)頻斜率為相位的二次導(dǎo)數(shù),相位截?cái)嗾`差本身已很小,所以對調(diào)頻線性度的影響就更小了。

4 實(shí)驗(yàn)結(jié)果

基于上述原理,首先對VHDL代碼進(jìn)行了時(shí)序仿真,然后將編譯綜合后的BIT文件下載到FPGA芯片中進(jìn)行系統(tǒng)聯(lián)調(diào)。實(shí)驗(yàn)表明,采用FPGA軟件編程技術(shù)較好地實(shí)現(xiàn)了線性調(diào)頻信號的產(chǎn)生,而且信號波形比較穩(wěn)定。

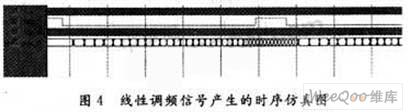

圖4為利用Modelsim軟件對本設(shè)計(jì)所產(chǎn)生的信號進(jìn)行仿真得到的時(shí)序仿真圖,從中可以看出在每個(gè)觸發(fā)周期內(nèi),所產(chǎn)生信號的變化頻率在不斷線性增加,可以較明顯地看出產(chǎn)生的是線性調(diào)頻信號。若要產(chǎn)生更低頻率及更精確的波形,可以提高分辨率并相應(yīng)減小基準(zhǔn)時(shí)鐘,這在FPGA中實(shí)現(xiàn)起來相對比較容易。

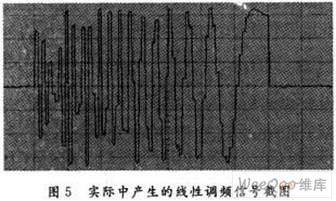

圖5為在實(shí)際調(diào)試過程中模擬產(chǎn)生一個(gè)脈寬7 μs、周期為700 μs、帶寬為5 Mb/s,中頻為7.5 MHz的線性調(diào)頻脈沖信號在示波器上的截圖。從圖中可以看出,本系統(tǒng)所產(chǎn)生的線性調(diào)頻信號基本達(dá)到了預(yù)定的指標(biāo),能夠滿足實(shí)際工程中的應(yīng)用,在雷達(dá)系統(tǒng)中有著較好的應(yīng)用前景。本文原理以及本系統(tǒng)亦可用于構(gòu)成產(chǎn)生相位編碼脈沖信號等其他形式的復(fù)雜雷達(dá)信號形式,具有較大的可擴(kuò)展性。

-

FPGA

+關(guān)注

關(guān)注

1629文章

21744瀏覽量

603618 -

芯片

+關(guān)注

關(guān)注

455文章

50851瀏覽量

423920 -

DDS

+關(guān)注

關(guān)注

21文章

634瀏覽量

152684

發(fā)布評論請先 登錄

相關(guān)推薦

求助C8051單片機(jī)控制DDS芯片AD9854產(chǎn)生一個(gè)線性調(diào)頻信號的程序

請問基于DDS技術(shù)能輸出線性調(diào)頻信號的單通道芯片嗎?

基于FPGA的雷達(dá)線性調(diào)頻信號實(shí)現(xiàn)

如何實(shí)現(xiàn)基于DDS芯片AD9858的線性調(diào)頻信號的設(shè)計(jì)?

基于FPGA的DDS調(diào)頻信號的研究與實(shí)現(xiàn)

基于STM32和FPGA的可控線性調(diào)頻信號源的設(shè)計(jì)

線性調(diào)頻信號干擾仿真分析

線性調(diào)頻信號特征分析及其在現(xiàn)代雷達(dá)中的應(yīng)用

線性調(diào)頻信號特征分析及其在現(xiàn)代雷達(dá)中的應(yīng)用

基于FPGA的線性調(diào)頻雷達(dá)各體制信號源的設(shè)計(jì)與實(shí)現(xiàn)

通過Matlab軟件實(shí)現(xiàn)對DSP/FPGA線性調(diào)頻信號仿真

如何基于DDS IP實(shí)現(xiàn)線性調(diào)頻信號

基于FPGA的DDS IP實(shí)現(xiàn)線性調(diào)頻信號的設(shè)計(jì)方案

基于FPGA的DDS芯片實(shí)現(xiàn)雷達(dá)線性調(diào)頻信號系統(tǒng)的設(shè)計(jì)

基于FPGA的DDS芯片實(shí)現(xiàn)雷達(dá)線性調(diào)頻信號系統(tǒng)的設(shè)計(jì)

評論