引言

雷達目標檢測與信息錄取是雷達系統與雷達信號處理系統的重要組成部分,超大規模集 成電路的發展,特別是高性能的信號處理器(DSP)架構的提升和大規模可編程邏輯器件的 出現,為雷達信號數字化處理帶來了新的突破。在高速數據采集方面,目前流行的方式是采 用高速A/D 轉換器件,主要的優點是信號精確度高,但高精度的同時不可避免的帶來了大 量實時數據流,對后端的信號處理系統將提出嚴格的要求,本系統采用了目標信號前言采集 的方式,與A/D 采集相比本方法雖然存在一定的采集精度差異,但該方法的數據采集量相 較前者有非常顯著減少。本文利用現代最新發展的大規模集成電路技術和數字處理技術,將 FPGA 和PC/104 相結合實現對原雷達原始信號的采集與處理。

1 系統總體設計方案

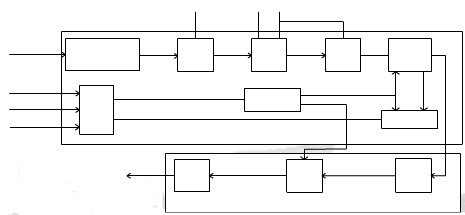

本文設計了一種基于船載導航雷達的船舶防碰撞系統。通過對原雷達的適應性改裝,為 雷達增加目標威脅度*判單元,提高雷達對目標的自動識別能力,系統通過實時監視全方位 的目標并計算運動參數以確定目標威脅等級,當檢測到危險目標時,輸出報警信號。該系統 實現了對原雷達的功能的延伸與擴展。系統的組成框圖如圖1 所示。

圖1 系統組成框圖

系統主要由數據實時采集模擬電路單元模塊、信息采集數字電路單元、RAM 存儲單元、 目標航跡處理分系統等組成。數據采集模塊通過引入探測雷達的船首信號、角度信號與距離 探測信號,對雷達視頻回波信號進行同步采集,在本系統中采用了目標前言采集;FPGA 內 部通過軟件設計主要完成對采集到的信號進行門限檢測角度、距離坐標定位形成雷達點跡數據;存儲模塊主要完成對錄取的目標坐標信息的實時存儲,由于該系統數據采集部分的數據 量并不大,故該存儲模塊則可以直接在FPGA 內部實現,不需要外接存儲設備。數據處理 分系統通過對點跡數據進行目標識別、目標跟蹤處理獲得目標航跡,并計算目標航跡參數, 根據所設定的參數對目標威脅度進行動態*判,并輸出報警信號。

2 系統主要工作過程

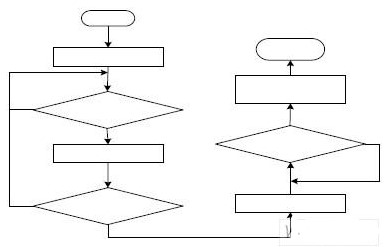

系統的基本處理過程如下圖2 所示 視頻信號展寬、放大:輸入視頻信號為未經任何處理的雷達信號,由于發射脈沖寬度為 0.8μs,實際回波的脈沖寬度在1~2μs 水平(由于接收機的通帶特性和目標縱深引起),為 保證抽樣不會漏信號,可考慮展寬到2μs 以上,輸入視頻信號的幅度在0.5V 左右的水平, 可通過放大使之便于信號處理(3V 左右)。

圖2 系統主要工作過程

同步整形:對輸入的探測信號和船首信號進行整形,使其幅度、寬度、脈沖形狀符合信 號處理要求;門限電路:根據輸入的門限設定值(預設可調量),在輸入視頻信號(前言) 超過門限而且滿足一定寬度(預設可調量)時,輸出一個計數控制信號到計數器1;計數器 1 將計數控制信號輸出到計數器2,同時開始計數,計數頻率為5MHZ。在計到寬度限定值(預 設可調量)之前,如果有新的計數控制信號輸入,重新開始計數,但不向計數器2 輸出;計 數器2 在距離起始脈沖到達時開始計數,計數的頻率為5MHZ,每輸入一個計數控制信號, 它輸出當前計數值作為目標距離數據到緩存器;計數器3 用于角度信號計數,開始標志為探 測雷達船首信號,每到達一個角度信號脈沖,計數一次,并將數據寫入RAM 存儲器,作為方 位計數值。

距離起始脈沖是由同步器根據探測信號產生的,同步器還產生一個距離結束信號,距 離起始與結束信號分別標志距離測量的開始與結束,初步考慮開始距離設定為2 海里(可設 定),結束距離設定為36 海里,間隔34 海里(可設定)。其中起始距離的設定主要基于減小 近距離強雜波對處理系統的影響。RAM 存儲器對目標距離數據和方位計數值進行存儲,每個 距離周期,在距離計數信號的觸發下,向PC 機輸出并清除存儲數據。如果存儲器內沒有目 標距離數據,則不輸出。

3 系統硬件實現

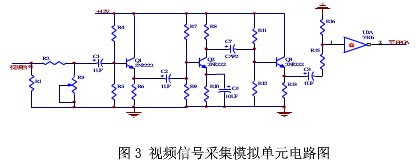

系統硬件部分有PC/104CPU板、數據采集板數字單元、數據采集板模擬單元三部分組組 成。PC/104CPU板采用主頻200M、內存64M、集成顯卡的基本硬件配置;數據采集數字單 元采用ALTERA公司的Cyclone系列FPGA 芯片EP1C6 ,其配置芯片為ALTERA公司的 4Mbits 容量PROM 芯片EPCS4,以主動串行方式對FPGA 進行上電配置;數據采集的模擬 單元主要由ULN2803、DM7406、2N2222等集成芯片。視頻信號處理部分硬件設計如圖3所 示。

圖3 視頻信號采集模擬單元電路圖

圖中C1、C2、C3 實現對信號的耦合作用。可調電阻R3 實現對信號放大幅度的調節。 經該電路轉換后的視頻信號為適合于數字處理的單個數字脈沖信號。實現了對回波信號的實 時采集。

4 系統軟件實現

4.1 FPGA 程序的設計

在FPGA 內部主要完成目標坐標信息的提取,實時存儲與傳輸控制模塊工作流程圖如圖 4 所示。

圖4 FPGA 工作流程圖

采集系統與PC104 之間的數據交換采用PCI 總線實現。具體方法為:在FPGA 內部配 置一片2K×16bits 的雙口RAM。當檢測到回波目標時,將此時刻的距離、方位計數值存入 RAM 存儲器,作為該目標的坐標信息。當檢測到距離結束信號時則將該段時間內所有目標 的信息數據打包發送至PC104 進行后續的信號處理,如果再探測周期內沒有回波目標則不 傳送數據。

4.2 用戶程序設計

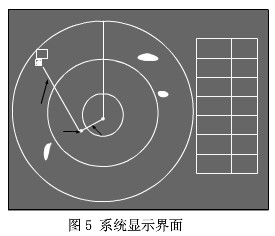

用戶程序主要完成雷達采集信號的航跡處理、參數計算、實時顯示和實時存盤。本系統 的用戶程序采用VC++作為開發工具,在WINDOWS操作系統下完成。工作過程如下:首先 通過PC機通過PCI總線接口,將信號采集的參數進行設置并存入FPGA內的存儲單元,FPGA 則根據這些設定的參數對目標信號進行采集;PC機在接收到中斷信號后,對RAM存儲器內的 距離、方位數據進行讀取并處理。然后用戶可以通過顯示器觀察目標回波信號,同時將目標 數據以二進制格式實時保存在PC機上的磁盤陣列上,供Matlab等軟件進一步分析和對交通事 故重現使用。系統的顯示界面如圖5所示。

圖5 系統顯示界面

5 總結

本文通過FPGA+PC/104 相結合,對來自雷達接收機的原始視頻信號進行采集、與數字 化處理,使雷達具備了目標威脅等級*判功能,且全程無需人工干預。實現了原雷達功能的 功能擴展與延伸。大規模可編程邏輯器件與工控PC機相結合的方案,整個系統具有體積小、 實時數據處理、以及方便的進行在線系統的改進與升級的特點。 作者的創新點:該系統運用FPGA+PC/104及其擴展模塊實現數據采集、處理。系統克服了 傳統PC機的缺點,具有體積小、功耗低、可靠性高等特點。

-

dsp

+關注

關注

553文章

8027瀏覽量

349253 -

FPGA

+關注

關注

1629文章

21752瀏覽量

604140 -

報警系統

+關注

關注

5文章

647瀏覽量

75213

發布評論請先 登錄

相關推薦

基于FPGA+PC104實現新型防碰撞報警系統的數據處理功能

基于FPGA+PC104實現新型防碰撞報警系統的數據處理功能

評論