1.引言

LED點(diǎn)陣顯示屏具有醒目、動(dòng)態(tài)效應(yīng)好、省電節(jié)能、亮度較高、用途廣等優(yōu)點(diǎn),是現(xiàn)代 化城市的主要標(biāo)志之一。利用VHDL硬件描述語(yǔ)言設(shè)計(jì)了以CPLD器件為核心的控制電路, 在LED點(diǎn)陣屏上實(shí)現(xiàn)了音頻信號(hào)的頻譜型電平動(dòng)態(tài)顯示, 而且具有顯示模式多樣化、易編程 修改,顏色可變、動(dòng)態(tài)效果好等優(yōu)點(diǎn)。

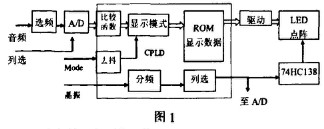

2.系統(tǒng)組成

本設(shè)計(jì)所用的EPM570T100C5采用了Altera公司的MAXII (Multiple Array Matrix II) 系列器件作為目標(biāo)CPLD,采用雙色8*8LED點(diǎn)陣作為終端顯示器件,配合一些必需的外圍器件 和電路,實(shí)現(xiàn)了對(duì)音頻信號(hào)的選頻、AD轉(zhuǎn)換、各頻段的電平顯示模式控制、最終實(shí)現(xiàn)了音頻 信號(hào)的頻譜型電平的動(dòng)態(tài)顯示。本系統(tǒng)的基本組成如圖1所示:

2.1 音頻輸入與預(yù)處理模塊

由于本設(shè)計(jì)采用8個(gè)頻段電平顯示,因此,筆者對(duì)音頻信號(hào)進(jìn)行了8個(gè)中心頻率分別為 100Hz、200Hz、500Hz、1000Hz、1500Hz、3000Hz、6000Hz、12000Hz的帶通電路的選頻處理, 經(jīng)電壓保持電路后送至以ADC0809為核心的八通道8位輸出數(shù)模轉(zhuǎn)換電路,由于ADC0809具有 八個(gè)輸入通道,受CPLD輸出的列選信號(hào)控制,從而實(shí)現(xiàn)了LED的八根列選線(共陰極)分別 對(duì)應(yīng)音頻信號(hào)的8個(gè)中心頻率,為頻譜型電平顯示實(shí)現(xiàn)了列選掃描控制。

由于列選信號(hào)的切換頻率設(shè)定為200Hz,即頻段切換周期為5ms,ADC0809 完全能夠勝 任音頻信號(hào)各頻段直流電平的A/D 轉(zhuǎn)換處理,因此,ADC0809 一直處于主動(dòng)轉(zhuǎn)換狀態(tài),無(wú)需 接受CPLD 芯片的轉(zhuǎn)換控制。

2.2 核心控制模塊

本設(shè)計(jì)的核心模塊采用Altera公司的CPLD器件,型號(hào)為EPM570T100C5,它基于突破性的 CPLD架構(gòu),提供業(yè)界所有CPLD系列中單個(gè)I/O管腳最低成本和最小功耗。這些器件采用新的 查表(LUT)體系,采用TSMC的0.18μm嵌入Flash工藝,使其裸片尺寸僅為同樣工藝器件的1/4, 而且包括非易失性Flash存儲(chǔ)模塊和JTAG控制電路。

本電路采用12MHz的有源晶振,為CPLD提供主時(shí)鐘。EPM570T100C5芯片主要集成了分頻、 列選掃描、按鍵去抖、數(shù)字電平信號(hào)的線性比較、顯示模式控制、顯示數(shù)據(jù)ROM等功能模塊。

分頻電路對(duì)12MHz時(shí)鐘信號(hào)進(jìn)行分頻處理后得到200Hz的列選計(jì)數(shù)脈沖,送至74HC138譯 碼器的輸入端和ADC0809的通道地址選擇控制端,實(shí)現(xiàn)8*8LED點(diǎn)陣的列掃描動(dòng)態(tài)控制和 ADC0809的通道選擇控制。

按照人眼的視覺(jué)習(xí)慣,線性比較電路主要負(fù)責(zé)將A/D轉(zhuǎn)換后的8位數(shù)據(jù)電平信號(hào)(共256 個(gè)組態(tài))轉(zhuǎn)換為8個(gè)梯級(jí)的數(shù)據(jù)信號(hào),經(jīng)顯示模式控制電路處理后作為地址數(shù)送至顯示數(shù)據(jù) ROM,從而直接調(diào)用ROM中寄存的顯示模式數(shù)據(jù)。

2.3 輸出與顯示模塊

本設(shè)計(jì)采用雙色(紅色和綠色)8*8LED 點(diǎn)陣作為終端顯示器件,在CPLD 的ROM 數(shù)據(jù)控 制下,8*8LED 點(diǎn)陣的每個(gè)像素點(diǎn)能產(chǎn)生紅色、綠色、$(紅綠混合色),能夠再現(xiàn)顏色 的多樣化。

由于一般的I/O 的驅(qū)動(dòng)能力是有限的,CPLD 中的ROM 輸出的顯示數(shù)據(jù)需要經(jīng)過(guò)驅(qū)動(dòng)電 路后送至8*8LED 點(diǎn)陣的行選端(陽(yáng)極),列選線(陰極)則受74HC138 輸出的低電平譯碼 信號(hào)的控制。

3.軟件設(shè)計(jì)

本設(shè)計(jì)采用Altera 公司的Quartus II 7.0 (32-Bit)集成開(kāi)發(fā)系統(tǒng),它具有簡(jiǎn)潔、合 理的操作界面,多語(yǔ)言支持的環(huán)境及其高效代碼生成編譯內(nèi)核使得所有的設(shè)計(jì)輸人、編譯、 綜合和仿真都可以在項(xiàng)目管理器中完成。另外,QuartusⅡ7.0 (32-Bit)支持幾乎所有的FPGA 和CPLD 芯片,與MATLAB 和DSP Builder 結(jié)合可以進(jìn)行基于FPGA 的DSP 系統(tǒng)開(kāi)發(fā),是DSP 硬件系統(tǒng)實(shí)現(xiàn)的關(guān)鍵EDA 工具,與SOPC Builder 結(jié)合,可實(shí)現(xiàn)SOPC 系統(tǒng)開(kāi)發(fā),是一款較受 用戶歡迎的開(kāi)發(fā)工具。

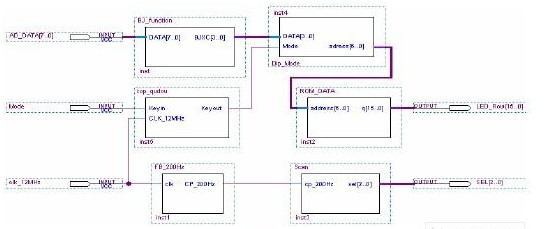

本文采用VHDL 語(yǔ)言作為硬件描述語(yǔ)言,采用自頂向下的層次化設(shè)計(jì)方法。為了突出各 模塊之間的連接關(guān)系,頂層模塊(Top.tdf)采用原理圖方式對(duì)各個(gè)功能模塊進(jìn)行綜合和調(diào) 用,如圖2 所示。

可以看出,軟件設(shè)計(jì)的功能模塊與系統(tǒng)組成中的核心模塊非常接近。

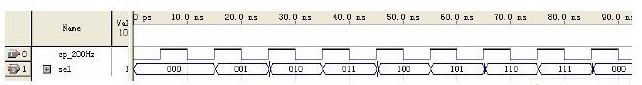

3.1 分頻與列選 掃描控制模塊

分頻模塊的作用是將12MHz的有源晶振時(shí)鐘信號(hào)通過(guò)軟件設(shè)計(jì)的方法分頻得到200Hz的 列選掃描時(shí)鐘信號(hào)。 列選掃描控制模塊的作用是設(shè)計(jì)一軟件計(jì)數(shù)器,將200Hz內(nèi)部信號(hào)轉(zhuǎn)換為列選掃描信號(hào) (SEL[2 downto 0]),仿真波形如圖3所示。該信號(hào)送至74HC138以后能夠動(dòng)態(tài)選中LED點(diǎn)陣的 某一列(共陰極),送至A/D0809以后能夠選擇相應(yīng)中心頻率的音頻信號(hào)進(jìn)行數(shù)模轉(zhuǎn)換。

3.2 按鍵去抖模塊

去抖的基本思路是設(shè)計(jì)一個(gè)移動(dòng)寄存器,移位脈沖的周期約為5ms,當(dāng)按鍵輸入的低電 平信號(hào)持續(xù)三個(gè)以上的脈沖周期時(shí)才輸出一個(gè)低電平脈沖,達(dá)到去抖的目的。部分程序如下:

--****設(shè)計(jì)一個(gè)3位移位D寄存器****--

process(CLK_200Hz)

begin

IF(CLK_200Hz'EVENT AND CLK_200Hz='1')THEN

Q<=Keyin&Q(2 downto 1);

END IF;

end process;

flag<=Q(2) or Q(1) or Q(0);

Keyout<='0'when flag='0' else--如果連續(xù)3個(gè)CLK后Q仍為低電平,則輸出低電平'1';

END a;

3.3 線性比較模塊

由于A/D轉(zhuǎn)換后的8位數(shù)據(jù)電平信號(hào)共有256個(gè)組態(tài),而終端顯示模塊為8*8LED點(diǎn)陣, 8*8LED點(diǎn)陣的每列顯示梯級(jí)最多為8級(jí),若加上全滅狀態(tài),8*8LED點(diǎn)陣的顯示梯級(jí)狀態(tài)共有9 種,因此,需要將A/D轉(zhuǎn)換后的8位數(shù)據(jù)電平信號(hào)按照人眼的視覺(jué)習(xí)慣轉(zhuǎn)換為9個(gè)梯級(jí)的數(shù)據(jù) 信號(hào),本設(shè)計(jì)采用函數(shù)(function)的方法實(shí)現(xiàn)了信號(hào)轉(zhuǎn)換功能,部分程序如下:

function DATA_YM (indata :std_logic_vector(7 downto 0))

return integer is

variable result :integer range 0 to 8;---比較函數(shù)輸出begin

if indata<16 then result :=0;

elsif indata>=16 and indata<48 then

result :=1;

elsif indata>=48 and indata<80 then

result :=2;

elsif indata>=80 and indata<112 then

result :=3;

elsif indata>=112 and indata<144 then

result :=4;

elsif indata>=144 and indata<176 then

result :=5;

elsif indata>=176 and indata<208 then

result :=6;

elsif indata>=208 and indata<240 then

result :=7;

else

result :=8;

end if;

return result;

end function;

3.4 顯示控制模塊

本模塊由顯示模式控制、顯示數(shù)據(jù)ROM模塊組成。顯示模式控制模塊采用一個(gè)Process 進(jìn)程語(yǔ)句循環(huán)定義了12種顯示模式,具體顯示的模式由按鍵按下的次數(shù)決定,即按鍵次數(shù)作 為內(nèi)部計(jì)數(shù)信號(hào),每種計(jì)數(shù)狀態(tài)則對(duì)應(yīng)一種ROM地址的起始值,從而實(shí)現(xiàn)了ROM地址能隨按鍵 次數(shù)而變化的確定關(guān)系。

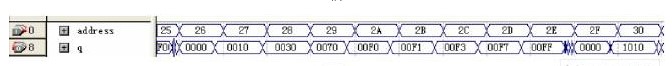

顯示數(shù)據(jù)ROM模塊將所有的顯示模式數(shù)據(jù)以ROM表格數(shù)據(jù)的形式進(jìn)行片內(nèi)存儲(chǔ),以便根據(jù) A/D轉(zhuǎn)換后的數(shù)據(jù)信號(hào)直接調(diào)用該表格數(shù)據(jù)。本模塊的功能仿真如圖4所示:

結(jié)果表明,該模塊能夠根據(jù)不同的地址值輸出相應(yīng)的顯示模式數(shù)據(jù),經(jīng)驅(qū)動(dòng)電路后送至 LED點(diǎn)陣的16個(gè)陽(yáng)極,能實(shí)現(xiàn)相應(yīng)的顯示模式的自動(dòng)切換或按鍵輸入切換。

4.實(shí)物調(diào)試

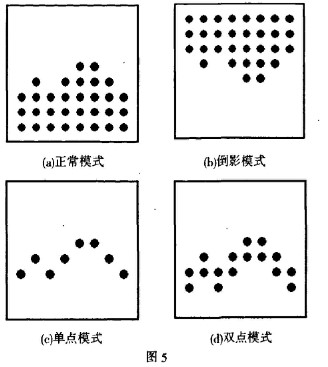

筆者利用北京R&C百科融創(chuàng)公司的EDA實(shí)驗(yàn)箱,通過(guò)擴(kuò)展導(dǎo)線與外部電路進(jìn)行連接,將程 序下載到芯片EPM570T100C5進(jìn)行實(shí)物模擬調(diào)試,得到如圖5所示的顯示模式位圖。

結(jié)果表明,本系統(tǒng)達(dá)到了設(shè)計(jì)要求,完成了音頻信號(hào)的頻譜型電平動(dòng)態(tài)顯示,具有正常 顯示、倒影顯示、單點(diǎn)顯示、雙點(diǎn)顯示等四大類顯示模式,每一大類顯示模式又能實(shí)現(xiàn)單紅 色、單綠色、$(紅綠混合色)三種顏色的自動(dòng)切換,動(dòng)態(tài)視覺(jué)效果好等特點(diǎn)。

5.結(jié)論

本文基于VHDL硬件描述語(yǔ)言,利用CPLD器件EPM570T100C5和LED點(diǎn)陣屏實(shí)現(xiàn)了對(duì)音頻信 號(hào)的頻譜顯示,并在電子設(shè)計(jì)的各個(gè)階段、各個(gè)層次進(jìn)行計(jì)算機(jī)模擬驗(yàn)證,保證設(shè)計(jì)過(guò)程的 正確性,拓展了CPLD在顯示領(lǐng)域的應(yīng)用。若將設(shè)計(jì)思路進(jìn)一步深入和擴(kuò)展,則能完成更大屏 幕、更多像素的LED頻譜顯示,能夠方便地應(yīng)用于商店、商場(chǎng)、卡拉OK等公共場(chǎng)所的LED顯示 區(qū)域,從而強(qiáng)化視覺(jué)效果。

-

led

+關(guān)注

關(guān)注

242文章

23252瀏覽量

660591 -

cpld

+關(guān)注

關(guān)注

32文章

1248瀏覽量

169336 -

vhdl

+關(guān)注

關(guān)注

30文章

817瀏覽量

128121

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

基于CPLD和FPGA的VHDL語(yǔ)言電路優(yōu)化設(shè)計(jì)

基于CPLD的頻譜電平顯示電路設(shè)計(jì)與實(shí)現(xiàn)

基于CPLD的頻譜電平顯示電路設(shè)計(jì)與實(shí)現(xiàn)

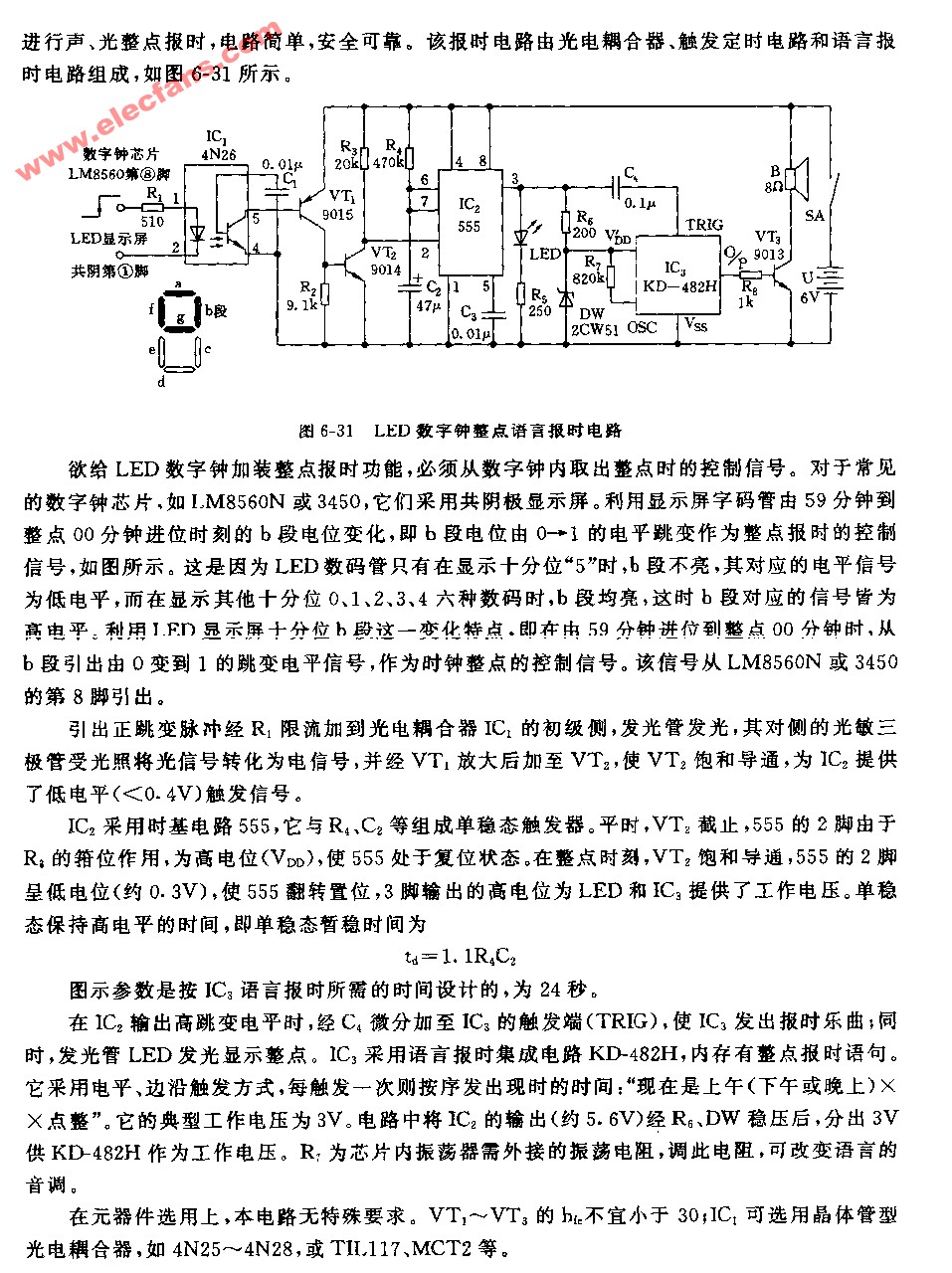

555動(dòng)態(tài)顯示LED整點(diǎn)語(yǔ)言報(bào)時(shí)電路

VHDL語(yǔ)言在FPGA/CPLD開(kāi)發(fā)中的應(yīng)用?

采用CPLD/FPGA的VHDL語(yǔ)言電路優(yōu)化原理設(shè)計(jì)

基于CPLD的VHDL語(yǔ)言數(shù)字鐘(含秒表)設(shè)計(jì)

基于VHDL語(yǔ)言和CPLD器件實(shí)現(xiàn)頻譜電平動(dòng)態(tài)顯示電路的設(shè)計(jì)

基于VHDL語(yǔ)言和CPLD器件實(shí)現(xiàn)頻譜電平動(dòng)態(tài)顯示電路的設(shè)計(jì)

評(píng)論