1 引言

多次重觸發技術應用于多種場合,如一個30齒的齒輪,設齒輪嚙臺系數為1.2,若測量其中1齒多次嚙合時的應力,則1齒的嚙合時間只占齒輪轉l圈時間的1.2/30,其余28.8/30的時間為空閑態,而空閑態記錄無意義。為此開發多次重觸發技術,以齒應力作為內觸發信號,只記錄每次觸發后的有用信號,并具有負延遲,而不記錄空閑狀態.直到占滿記錄裝置存儲空間,這樣可有效利用存儲空間,記錄更多的有用信號。

2 多次重觸發存儲測試系統總體設計

2.1 多次重觸發存儲測試系統工作原理

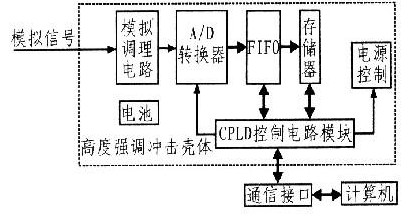

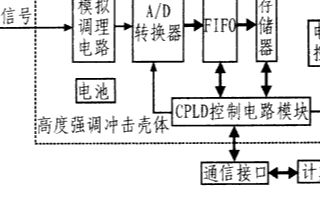

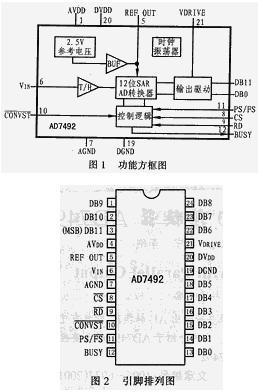

圖1為多次重觸發存儲測試系統原理框圖,其工作原理:被測信號經傳感器變為電信號后,輸入至模擬調理電路,再經放大濾波后輸入至A/D轉換器,將模擬信號轉換為數字信號,然后經過FIFO傳輸給存儲器,計算機通過通信接口讀取數據。其中,該存儲測試系統的A/D轉換器的轉換和讀時鐘、FIFO及存儲器的讀寫時鐘、推地址時鐘均由CPLD控制產生。

2.2 負延遲的實現

動態信息存儲要求真實有效地記錄有用信號,根據被測信號特點,需記錄下觸發前信號在極短時間內的數據,這就要使用負延遲技術。負延遲也稱為提前傳輸,即將觸發信號的觸發采集時刻提前一段時間作為傳輸數據的起始點。該系統設計采用FIFO存儲器實現負延負延遲。觸發信號未到來時,A/D轉換器輸出的數據不斷寫入FIFO存儲器中,A/D轉換器轉換的數據不斷刷新FIFO存儲器的內容。一旦觸發信號到來,數據則開始從FIFO寫入存儲器。

2.3 主要器件選型

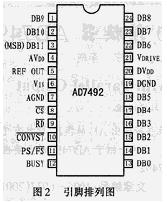

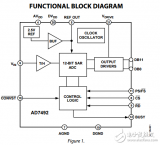

該系統設計選用AD7492型A/D轉換器。該器件為12位高速、低功耗、逐次逼近式A/D轉換器。在5 V電壓,速率為1 MS/s時,其平均電流僅1.72 mA,功耗為8.6 mW;在5 V電壓和500 kS/s數據傳輸速率下,消耗電流1.24 mA,因此,該器件能夠滿足系統低功耗要求。由于該系統設計的存儲器總體容量為512 KB,因此選用l片容量為512 KB的N08T163型存儲器。并通過靜態存儲器時序配合實現自制的FIFO存儲器,功耗約為同類FIFO存儲器的1/10。系統設計的負延遲記錄l KB,選用128 KB容量的N02L163WC2A型存儲器。針對存儲測試系統功耗低,體積小,且控制邏輯較復雜的因素,MAX7000B系列的EPM7128BTCl44-4型CPLD作為控制器。該器件是高性能,低功耗的CMOS型CPLD,2500個可用邏輯門電路,引腳到引腳的傳輸延時為4.0 ns,系統工作頻率高達243.9 MHz。

3 CPLD控制電路的設計

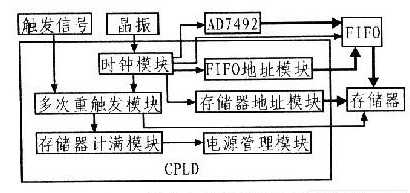

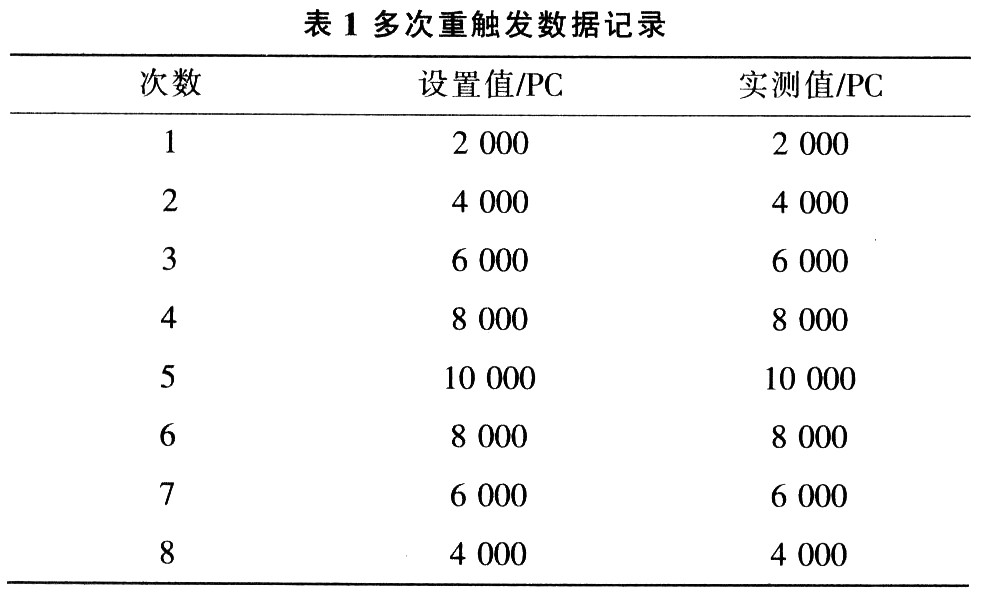

基于CPLD的多次重觸發存儲測試系統主要由A/D轉換器、存儲器、FIFO和控制器CPLD等組成,其中CPLD控制電路由時鐘、多次重觸發、FIFO地址發生、存儲器地址發生、存儲器計滿,電源管理和計算機通信等模塊組成,如圖2所示。

3.1 控制電路各模塊功能

(1)電源管理模塊 該模塊主要控制系統功耗。當系統處于休眠狀態時,只有Vcc對CPLD供電;當系統進入正常工作狀態時,Vcc,VDD和VEE同時供電,晶振工作,當采樣結束,系統關閉VEE,模擬部分進入休眠狀態,晶振停止工作。該模塊能夠滿足系統低功耗要求。

(2)時鐘模塊 晶振提供的4 MHz信號經4個二分頻器,分別得到2 MHz、1 MHz、500 kHz和250 kHz的時鐘信號,由這些信號組合得到A/D轉換器的采樣信號convst、FIFO的寫信號、A/D轉換器的讀信號ffwr_adread以及FIFO的推地址信號ff_dz,均為250 kHz。

(3)多次重觸發模塊 當外界多次重觸發信號m_tri到來后。經D觸發器產生的open信號變為高電平,計數器開始計數時鐘信號ff_dz,每計8 KB后停止計數,并產生清零信號clr對open信號清零,等待下次觸發信號。由時鐘信號ff_dz和open信號控制產生的時鐘信號clkl作為寫存儲器時的推地址信號和寫信號,open信號取反后接至存儲器使能端。

(4)FIFO地址發生模塊CPLD對FIFO的地址控制由時鐘模塊ff_dz信號產生,在時鐘信號ff_dz的下降沿開始推FIFO地址。

(5)存儲器地址發生模塊 多次重觸發模塊產生clkl信號作為存儲器的推地址信號m_dz推地址,將轉換數據寫入存儲器,寫滿8 KB后停止寫操作,等待下次觸發信號。存儲器存滿512。KB后停止推地址和寫操作,等待計算機讀數。讀數時,計算機每向CPLD發送1個讀數脈沖,地址信號向前推進1位,CPLD就從存儲器中對應的地址單元讀取1個數據。

(6)存儲器計滿模塊 當多次重觸發信號m_tri到來后,open信號變為高電平,計滿8 KB后變為低電平,等待下次觸發信號。因此用計數器計數open信號下降沿,計滿64個后存儲器滿信號tc變為高電平。

3.2 CPLD總體控制電路仿真及分析

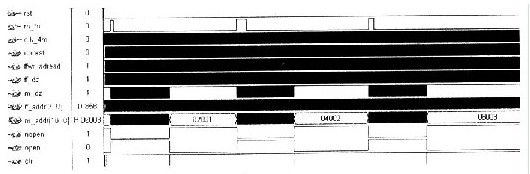

圖3為CPLD總體控制電路仿真圖。圖3中觸發信號m_tri產生3次,由nopen信號看出存儲器選通3次,由存儲器地址信號m_addr的變化可看出存儲器記錄每個觸發信號8 KB,并不斷更新FIFO的數據。第1個觸發信號m_tri到來后,nopen信號變為低電平即選通存儲器。這時產生存儲器的推地址信號和寫信號m_dz信號,并且在下降沿時將推地址給存儲器,存儲器在低電平期間進行寫操作。觸發信號m_tri到來后計滿8 KB,nopen信號產生高電平不選通存儲器,且存儲器的推地址信號和寫信號m_dz變為高電平。

4 實驗驗證

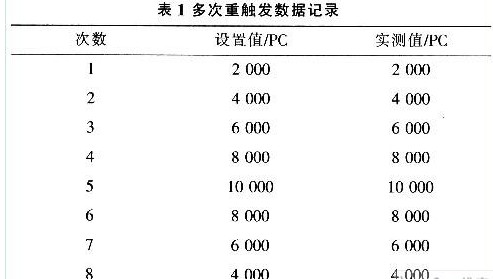

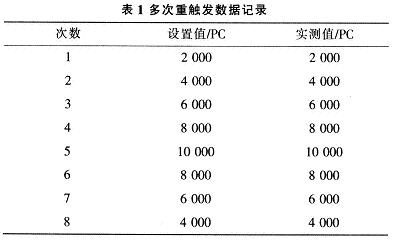

通過實驗驗證該測試系統功能。實驗中給測試系統加載8次觸發信號,連續采集8次。由于該系統設計最多可以采樣64次,如果重觸發信號次數未達到64次,需手動給測試儀一個強制讀數信號使得儀器采樣結束。多次重觸發信號8次有效后,手動強制讀數信號使得儀器結束采樣,通過上位機軟件判斷采集到的波形幅值和手動調節的幅值是否對應。若對應,表明系統采樣正常。

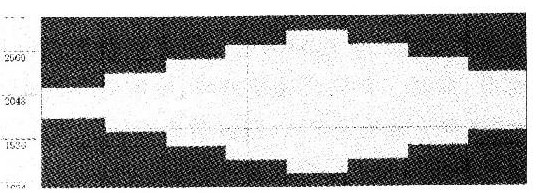

實驗步驟:測試儀接通電源,此時測試儀采樣狀態指示燈的紅燈亮,和計算機接上編程讀數線,打開編程界面,設置多次重觸發的采樣頻率,其他選項均采用默認設置,編程完成后,拔掉編程讀數線,測試儀上電(ON=0),紅燈開始閃爍,將電荷校準儀的輸出接到測試儀面板上的通道端,設置電荷校準儀的輸出波形為正弦波,電荷量為2 000 PC,輸出信號,給系統一個觸發信號(M_TRI=1),紅燈閃爍一段時間后停止閃爍,表明系統第一次采樣完成,這時調節電荷校準儀的輸出電荷量為4 000 PC。再給系統一個觸發信號,重復前面過程,每次采樣完成后改變電荷量,直到綠燈亮,和計算機連上編程讀數線,通過上位機軟件讀取數據,待數據讀取完畢,測試儀掉電(OFF=0),斷開測試儀電源。圖4為多次重觸發波形。對圖4中的數據進行轉換和處理得到實測的電荷量值如表1所示,從表1看出,采集到的波形幅值與調節的順序一致,系統設計符合要求。

5 結論

本文設計的基于CPLD的多次重觸發存儲測試系統性能較穩定,測量精度較高,能在高沖擊等惡劣環境下正常工作,并且滿足系統的低功耗、微型化要求,實現不失真采樣存儲信號。此系統能夠實時記錄多次重觸發信號,每次信號的記錄均有負延遲,讀取數據時,無需程序調整,即可準確復現記錄波形,因此存儲測試技術在多個瞬態信號的測量中具有廣闊前景。

-

轉換器

+關注

關注

27文章

8724瀏覽量

147414 -

cpld

+關注

關注

32文章

1248瀏覽量

169432 -

存儲器

+關注

關注

38文章

7513瀏覽量

163987 -

測試系統

+關注

關注

6文章

824瀏覽量

62160

發布評論請先 登錄

相關推薦

采用復雜可編程邏輯器件實現多次重觸發存儲測試系統的應用方案

請問AD7492噪聲怎么解決

AD7492中文資料 (12位并行輸出AD轉換器)

AD7492,pdf datasheet (12Bit Pa

12位并行輸出AD轉換器AD7492

1.25MSPS的16毫瓦的內部參考和時鐘12位并行模數轉換器AD7492數據表

逐次逼近式AD轉換器AD7492的性能特點和應用電路分析

EVAD7492 AD7492 評估板

采用AD7492型A/D轉換器實現多次重觸發存儲測試系統的設計

采用AD7492型A/D轉換器實現多次重觸發存儲測試系統的設計

評論