引言

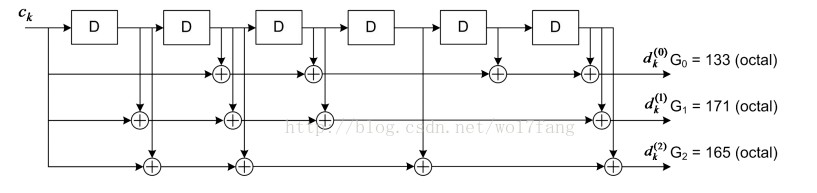

自1955年Elias發明卷積碼以來,卷積碼作為一種高效的信道編碼已被用在許多現代通信系統中。卷積碼分為零比特卷積碼(Zero Tail CC,簡稱ZTCC)和咬尾卷積碼(Tail Biting CC,簡稱TBCC)兩種。ZTCC是指在編碼的時候,碼字后面要另外加上K(K為約束長度)個0將編碼寄存器的最后狀態打出,而TBCC則是直接用碼字的最后K個比特將編碼寄存器初始化,從而提高編碼率。現在的3G和4G通信標準中(比如WiMAX或LTE)都采用了TBCC信道編碼。關于TBCC的譯碼算法很多,其中比較經典的譯碼算法有循環維特比算法(CVA)和BCJR算法。但上述算法由于解碼時延不固定和復雜度的原因,均不便于硬件實現。為此,本文提出了一種便于硬件實現的次優解碼算法。

1 TBCC譯碼算法

1.1 最優譯碼算法

TBCC的理論最優譯碼算法是,對于每一個可能的初始狀態(3k)用維特比譯碼算法對所有可能的狀態進行搜索,最后再根據最好的狀態進行解碼。但是,這種算法的復雜度太高,不利于硬件實現。

1.2 次最優譯碼算法

次最優譯碼算法的經典代表是CVA算法,此外還有其改進的算法比如環繞維特比算法(WAVA)和雙向維特比算法(BVA)。它們的主要思路是利用圓形buffer將碼字擴展成多個相同碼塊首尾相接的長碼塊進行譯碼。當檢測到首尾狀態相等或者滿足自適應迭代的停止條件時,即完成譯碼;否則繼續進行迭代。但該算法或其改進的WAVA和BVA算法都存在這樣一個問題。那就是解碼的延遲不是固定的,而這非常不便于硬件實現。

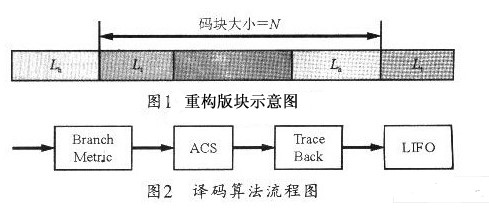

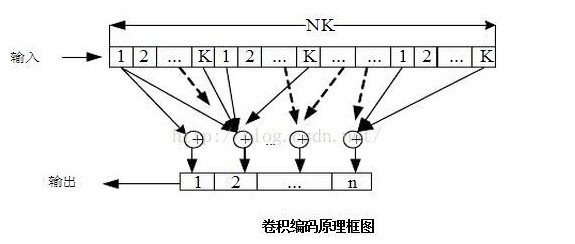

所以,本文中提出固定延遲的譯碼算法,其基本思路是在碼塊的前Lt個符號補在符號的后面,將碼塊的后Lh個符號補在碼字的前面,這樣就構成一個長度為Lt+N+Lh的新碼塊(假設原碼字長度為N),圖1所示是重構的碼塊示意圖。該新碼塊可以按照ZTCC解碼一樣去解碼,然后從具有最小路徑度量(path metric)的狀態進行回溯。

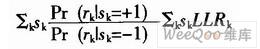

圖2所示是其譯碼算法流程圖。其中Lt和Lh參數的選擇應根據仿真來確定。這里采用典型值:Lt=72,Lh=96。

2 TBCC譯碼算法的實現

2.1 分支度量(branch metric)的計算

維特比譯碼算法采用ML準則,其分支度量可通過下式計算:

2.2 加-比較-選擇器(ACS)

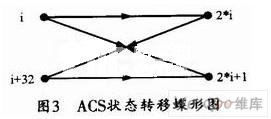

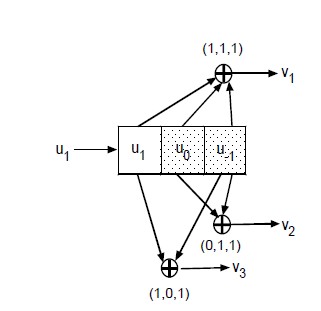

圖3所示是ACS的狀態轉移蝶形圖。實際上,卷積碼的Trellis圖具有如下性質(LTE中TBCC編碼約束長度為7):

對于每一個狀態,其前面的狀態為i<<1和(i<<1)+32;而對于每一個狀態,其后面的狀態為(i>>1)%64和(i>>1+1)%64。

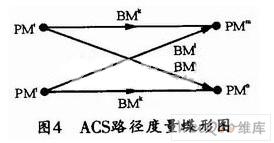

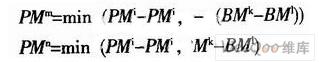

上述性質在硬件實現時非常好用。由上述性質可以給出路徑度量的計算式:

從上面的公式可以看出。計算一個蝶形圖需要4次加法和2次比較。圖4所示是ACS路徑度量蝶形圖。此外,操作時還可采用Andries的簡化方法來減小硬件開銷,其公式如下:

計算出需要2次加法。對于LTE中約束長度為7的TBCC來說,總共有64個狀態,可以分別在兩個蝶形圖里面使用(符號會有所變化),這樣,加法器就減小為32,加上每個路徑度量更新還需要一個加法器,這樣共需要的加法器為32+64=96,比之前未簡化的算法少用了32個加法器。

2.3 回溯

回溯的深度(Trace back Depth)必須大于編碼深度(Coding Depth),這是因為,經過回溯CD的長度,所有的幸存路徑均會收斂。每次回溯時,所有幸存路徑都需要從內存里面讀出TD個狀態,同時將有TD-CD個判斷之后的比特送入LIFO。回溯之后,會有TD-CD的內存空間可寫,另外在回溯時,還需要TD-CD個內存空間來保存進來的數據,這樣,內存空間就共需TD+(TD-CD)=2TD-CD。在此可取典型值TD=96,CD=72。

2.4 FPGA的實現

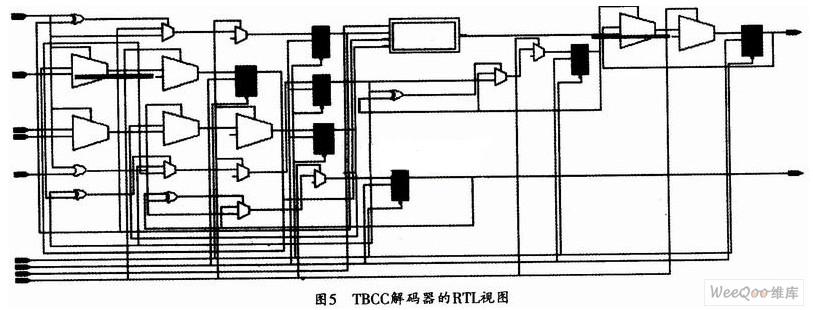

本設計采用的FPGA芯片為Altera的StratixIIIEP3SL340系列器件,其在QuartusII9.0下綜合出來的RTL視圖如圖5所示。其布線后所占用的資源如表l所列。

3 仿真驗證

本文采用的開發流程是先在matlab下仿真出浮點算法的性能,然后根據系統要求用C實現定點模型,在和浮點的版本比較后,再采用Ver-ilog實現。由于用verilog做性能仿真比較慢,本文采用的仿真和驗證方法是在定點C下做性能仿真,然后將C版本的輸入輸出作為黃金參考數據,再用modelsim仿出vetilog版本的數據和參考數據做對比,如果數據完全一樣,則驗證通過,否則調試verilog語言并追蹤錯誤。

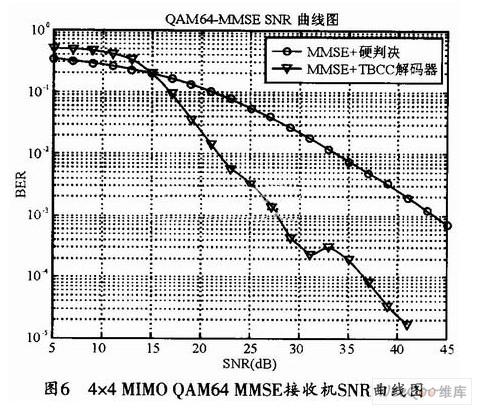

驗證選擇的碼長為1080,將TBCC解碼器放在4×4 MIMO接收機里,可得到如圖6所示的SNR曲線。

由圖6可知,在SNR很小的時候,TBCC解碼器的性能反而較硬判決會下降,這是由于SNR太小,TBCC已經無法從很少的已知信息中糾正其他的錯誤信息。而當SNR較大時,TBCC解碼器就可以從相對多的已知信息中糾正錯誤信息。由圖6可見,在誤碼率為10-3以下時,TBCC能夠獲得約2l dB的增益。

4 結束語

該解碼器已經用在MIMO接收機的FPGA版本中。并且經過實驗室測試,能夠成功的解碼出咬尾卷積編碼,并具有較好的性能。另外,該解碼器在實現上用的硬件資源很少,這可為整個系統的集成奠定基礎。

-

FPGA

+關注

關注

1629文章

21729瀏覽量

603008 -

解碼器

+關注

關注

9文章

1143瀏覽量

40718 -

寄存器

+關注

關注

31文章

5336瀏覽量

120231

發布評論請先 登錄

相關推薦

什么是卷積碼? 什么是卷積碼的約束長度?

卷積碼的Viterbi高速譯碼方案

卷積碼/Viterbi譯碼,卷積碼/Viterbi譯碼是什么

LTE中Tail-biting卷積碼的譯碼器設計

基于FPGA的卷積碼譯碼器的方案

基于Viterbi算法的卷積碼性能分析

在FPGA上實現咬尾卷積碼的最優算法設計

在FPGA上實現咬尾卷積碼的最優算法設計

評論