1 引言

信號源作為一種電子測量和計量設(shè)備,通常可產(chǎn)生大量的標(biāo)準(zhǔn)信號和用戶定義信號。由于它具有高精度、高穩(wěn)定性、可重復(fù)性和易操作性等特點(diǎn),而被廣泛用于自動控制系統(tǒng)、震動激勵、通訊和儀器儀表領(lǐng)域。它不僅可以模擬各種復(fù)雜信號,還可對頻率、幅值、相移、波形進(jìn)行動態(tài)、及時的控制,并能與其它儀器進(jìn)行通訊,組成自動測試系統(tǒng)。在各種實驗應(yīng)用和實驗測試處理中,既可根據(jù)使用者的要求,作為激勵源來仿真各種測試信號,并提供給被測電路,以滿足測量或各種實際需要,也可作為一種測量儀器來完成一定的測試功能。然而,由于應(yīng)用背景的不同和對測試、測量技術(shù)要求的提高,對信號源的頻率精度、幅值精度、信號形式等要求也越來越高,因此開發(fā)高精度信號源具有重大的意義。

所設(shè)計的高精度信號源可對存儲測試系統(tǒng)、數(shù)據(jù)采集系統(tǒng)及導(dǎo)彈匹配裝置進(jìn)行測試,并可檢測目標(biāo)設(shè)備的工作狀態(tài)和各項性能指標(biāo),為及時查找被測物體在運(yùn)作中可能發(fā)生故障的原因,提供有效的測試手段,為產(chǎn)品設(shè)計與問題故障分析提供依據(jù)。

2 系統(tǒng)總體方案設(shè)計

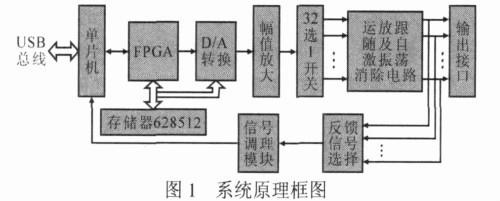

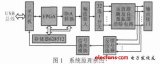

測試系統(tǒng)通過USB 接口與計算機(jī)相連,由計算機(jī)軟件生成數(shù)據(jù)并完成下載,實現(xiàn)波形實時可控輸出。系統(tǒng)原理框圖如圖1 所示。

信號源的工作過程如下:計算機(jī)發(fā)出命令和波形數(shù)據(jù),通過USB 總線傳送給USB 接口芯片,經(jīng)高速串行總線下傳到單片機(jī)C8051F060,單片機(jī)對其接收到的指令和波形數(shù)據(jù)詮釋后下傳給FPGA,由FPGA 完成數(shù)據(jù)存儲、D/A 轉(zhuǎn)換、功能指示及其他邏輯控制。D/A 轉(zhuǎn)換后的模擬信號經(jīng)調(diào)理電路后輸入到32 選1 開關(guān)電路進(jìn)行選通,再經(jīng)運(yùn)放跟隨和自激振蕩消除電路處理后即可輸出。信號輸出的同時再輸入到反饋信號選擇電路,由C8051F060 自帶的16 位AD 采集反饋信號,與理論值進(jìn)行比較并動態(tài)調(diào)整,組成閉環(huán)控制系統(tǒng),以提高輸出信號的精度。

3 系統(tǒng)實現(xiàn)

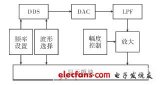

硬件實現(xiàn)主要包括元器件的選擇、波形重構(gòu)電路設(shè)計、信號調(diào)理技術(shù)、降噪技術(shù)等多種硬件處理技術(shù)。根據(jù)上述方案,主控制芯片選用全集成混合信號在片系統(tǒng)單片機(jī)C8051F060,FLASH 存儲器還具有重新編程能力,可在線調(diào)試。C8051F060 自帶16 位ADC,可采集反饋信號,符合信號源的需要,組成閉環(huán)控制系統(tǒng),大大提高了系統(tǒng)的精度。設(shè)計中選用AD768 型D/A 轉(zhuǎn)換器,它具有16 位的分辨率,理論精度為1/216=0.002%,滿足該信號源0.01%的精度要求。該器件具有良好的直流和交流特性,最大數(shù)據(jù)更新速率為30MSPS,片上集成2.5 V 帶隙參考電壓,可保證輸出電壓的精度和穩(wěn)定性。AD768 特殊的內(nèi)部結(jié)構(gòu)使其具有優(yōu)越的動態(tài)精確度,并且單線控制,操作方便。

軟件設(shè)計主要是指計算機(jī)產(chǎn)生各種控制命令和波形數(shù)據(jù),制定相關(guān)通信協(xié)議,按照既定協(xié)議把命令和數(shù)據(jù)實時下傳給單片機(jī),保證計算機(jī)與單片機(jī)之間的正確通信。USB 串行總線每次下傳8 位數(shù)據(jù),但要求信號源精度為0.01%,用8 位數(shù)據(jù)不能達(dá)到要求,故選用了AD768.首先由計算機(jī)產(chǎn)生16 位的波形數(shù)據(jù),并把每個16 位數(shù)據(jù)分離成3 個8 位數(shù)據(jù),其他空余位用來標(biāo)識高低位。在D/A 轉(zhuǎn)換前,控制模塊單片機(jī)C8051F060 和FPGA 的工作之一就是要把它們還原成原來的16 位數(shù)據(jù),也就是數(shù)據(jù)的二次編碼,這樣AD768 收到的就是二次編碼后完整的16 位數(shù)據(jù)。

4 閉環(huán)控制系統(tǒng)的實現(xiàn)

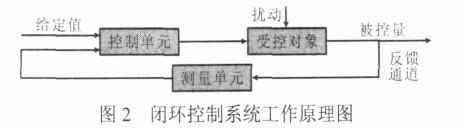

閉環(huán)控制系統(tǒng)是指從輸出端到輸入端帶有反饋通道的控制系統(tǒng),亦稱為反饋控制系統(tǒng),如圖2 所示。該系統(tǒng)能對輸出量與參考輸入量進(jìn)行比較,并將它們的偏差作為控制手段,以保持兩者之間的預(yù)定關(guān)系。在該系統(tǒng)中,控制單元與受控對象之間不僅有順向作用,而且還有逆向聯(lián)系。作為輸入信號與反饋信號之差的誤差信號被傳送到控制單元,以便減小誤差,并使系統(tǒng)的輸出達(dá)到期望值。

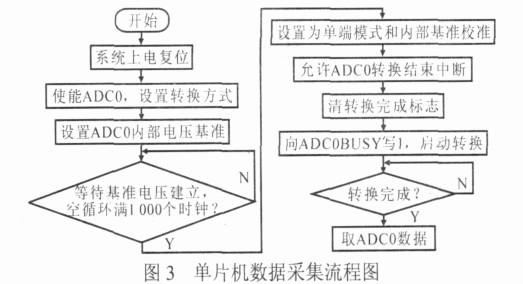

采用反饋可使系統(tǒng)的響應(yīng)對外部干擾和系統(tǒng)內(nèi)部的參數(shù)變化不敏感,系統(tǒng)可達(dá)到較高的控制精度和較強(qiáng)的抗干擾能力。對于給定的被控對象,就有可能采用不太精密且成本較低的元件來構(gòu)成比較精確的控制系統(tǒng),這在開環(huán)情況下,是不可能做到的。閉環(huán)控制主要通過對反饋信號進(jìn)行回采校正實現(xiàn)。在模擬信號的輸出端增設(shè)反饋、校正模塊,可任意選擇某一路信號進(jìn)行反饋,由C8051F060 集成ADC 采集。反饋采集命令和反饋通道都是由計算機(jī)發(fā)出。在此使用SAR ADC0,其初始化和采集流程圖見圖3。

將反饋電壓采集回來的電壓通過單片機(jī)的串口上傳到計算機(jī),與給定值比較,進(jìn)行輸入校正,直至其輸出精度達(dá)到0.01%.反饋閉環(huán)控制使該信號源的響應(yīng)對外部干擾和系統(tǒng)內(nèi)部的參數(shù)變化不敏感,達(dá)到了較高的控制精度和較強(qiáng)的抗干擾能力。

5 測試結(jié)果及分析

對信號源的輸出測量主要包括幅值精度測量和通道干擾測量。前者主要測量信號輸出的線性度及硬件輸出的重復(fù)性,即利用單片機(jī)生成波形數(shù)據(jù),在FPGA 控制下,啟動D/A 轉(zhuǎn)換并穩(wěn)定后保持10 s,利用高精度萬用表對信號輸出的幅值進(jìn)行測量。

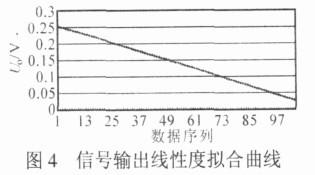

5.1 線性度測量

當(dāng)為波形重構(gòu)電路提供的波形數(shù)據(jù)按線性規(guī)律變化時,在理論上波形輸出應(yīng)為一條直線。在波形重構(gòu)電路中,采用的AD768 理論步長為65 536.當(dāng)波形數(shù)據(jù)在從0~65 535 變化時,最終的信號幅值將在- 12.5~+12.5 V 之間變化。對波形數(shù)據(jù)從0 開始以6 為公差進(jìn)行自加,其中的一次典型測量所獲得的數(shù)據(jù)擬合后見圖4.經(jīng)計算,當(dāng)以6 個理論步長自加時,信號輸出幅值的平均變化為2.28 mV,則輸出精度為2.58mV/25 V≈0.009 12%.對應(yīng)于圖4 可算得信號輸出幅值的平均變化為2.32 mV,則輸出精度為2.32mV/25 V≈0.009 28%,實際精度接近理論精度,滿足了設(shè)計要求。

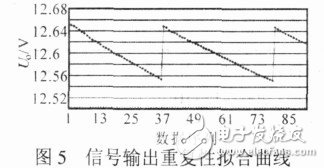

5.2 重復(fù)性測量

重復(fù)性測量旨在測試信號源輸出的重復(fù)性,通過為波形重構(gòu)電路提供循環(huán)的波形數(shù)據(jù)來考察信號源的輸出能力。其典型數(shù)據(jù)擬合波形見圖5.由該圖可見,該信號源有較好的一致性輸出能力。

6 結(jié)束語

所設(shè)計的高精度信號源將單片機(jī)、FPGA、信號調(diào)理等技術(shù)進(jìn)行了有機(jī)的結(jié)合,構(gòu)建了一個閉環(huán)控制自檢系統(tǒng),能提供正弦、方波、三角、鋸齒及不規(guī)則信號。利用USB 總線技術(shù),可實現(xiàn)計算機(jī)數(shù)據(jù)和命令的實時下載,信號源功能均通過計算機(jī)發(fā)出命令下傳給硬件實現(xiàn),具有實時可編程的優(yōu)點(diǎn)。經(jīng)實驗測量,信號源輸出信號精度可達(dá)0.01%,且信號線形度和輸出重復(fù)性較好,滿足設(shè)計要求,運(yùn)行良好,性能穩(wěn)定。

-

FPGA

+關(guān)注

關(guān)注

1629文章

21748瀏覽量

603989 -

單片機(jī)

+關(guān)注

關(guān)注

6037文章

44568瀏覽量

636049 -

信號源

+關(guān)注

關(guān)注

5文章

478瀏覽量

44438

發(fā)布評論請先 登錄

相關(guān)推薦

單片機(jī)簡易信號源

高精度智能信號源設(shè)計

基于FPGA的DDS信號源設(shè)計與實現(xiàn)

智能多路信號源的設(shè)計與實現(xiàn)

高精度DDFS信號源FPGA實現(xiàn)

基于8051F單片機(jī)的數(shù)字音頻信號源的幅度控制

單片機(jī)脈沖信號源的CPLD實現(xiàn)方案

基于CycloneII系列FPGA的DDFS信號源實現(xiàn)

基于FPGA的高精度信號源的設(shè)計

FPGA+DDS實現(xiàn)數(shù)控信號源的設(shè)計

基于FPGA的實時可編程高精度信號源設(shè)計

基于AD9959的高精度多通道雷達(dá)信號源設(shè)計

基于DDS技術(shù)的多路同步信號源的設(shè)計

基于PIC單片機(jī)的測井系統(tǒng)激勵信號源研制

將單片機(jī)和FPGA組合實現(xiàn)高精度信號源的設(shè)計

將單片機(jī)和FPGA組合實現(xiàn)高精度信號源的設(shè)計

評論