引言

隨著HDTV 的普及,以LCD-TV 為主的高清數字電視逐漸進入蓬勃發展時期。與傳統CRT 電視不同的是,這些高清數字電視需要較復雜的視頻處理電路來驅動,比如:模數轉換(A/D Converter)、去隔行(De-interlacer)、視頻縮放(Scaler)和視頻圖像增強(Video Enhancement)等等。由于HDTV 的帶寬較高,720p 信號(1280×720?Hz)的像素速率達到74MHz,因此針對HDTV 的視頻處理算法需要更高性能的器件。采用大規模高工藝的ASIC 芯片是目前這個問題的主要解決方案,Pixelworks、Genesis 等公司均推出了基于大規模ASIC 的解決方案。但是,隨著FPGA 工藝的不斷改善,其性價比與日俱增,尤其是Xilinx、Altera 等廠商紛紛采用90nm 工藝量產后,其價格不斷降低,Xilinx 最新推出的Spartan-3E系列FPGA 120 萬門的售價只有 9 美元,已經在小量產品的IC 設計中開始替代結構化ASIC,在數字高清電視這類價格敏感型消費類電子產品中也開始大量采用。

本文介紹了如何在FPGA 中利用Block RAM 的特殊結構實現HDTV視頻增強算法中灰度直方圖統計。

灰度直方圖統計

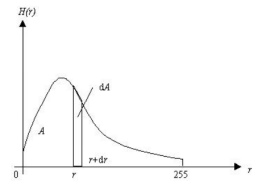

灰度直方圖統計是圖像處理過程中很常用的一個步驟,簡單來講,就是對一幅圖像各個灰度的像素進行計數,得到一張灰度分布表。例如,8 位量化的灰度圖像統計結果就是256個值,分別代表0-255 每個灰度像素的數量,如圖1 所示為Lena 圖像的灰度直方圖統計結果。直方圖是分析一幅圖像亮度分布特性有力的工具,根據它的結果可以進行諸如灰度拉伸、自動對比度、動態伽馬調整等操作。

圖1 Lena 圖像的灰度直方圖統計

FPGA算法統計

在計算機或者DSP 上實現直方圖統計時,我們通常會使用數組結構,即在內存中開辟一個整數數組來進行計數,但是在FPGA 中定義數組是非常消耗資源的,尤其是當數組成員的位寬很大時。例如用觸發器來統計256 灰度的720p 圖像的直方圖,將消耗4000 個邏輯單元(每個邏輯單元是一個四輸入查找表),這幾乎消耗了一個Spartan-3E 25 萬門器件(XC3S250E)80%的邏輯資源。

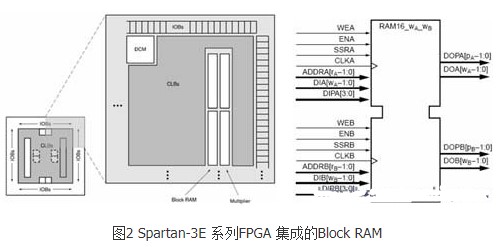

幸運的是,FPGA 器件提供了一個很好的結構可以處理這類問題,這就是Block RAM。在Altera 和Xilinx 的各型號FPGA 器件上都集成了一種稱為Block RAM 的片上內存,它們以若干Kbits 為一塊,不同型號集成不同數量的塊,例如在Spartan-3E 系列中以18Kbits 為一塊,在規模最小的型號XC3S100E 上集成了4 塊這樣的內存,如圖2 所示:

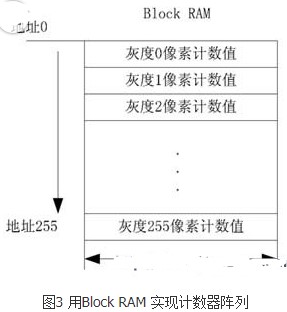

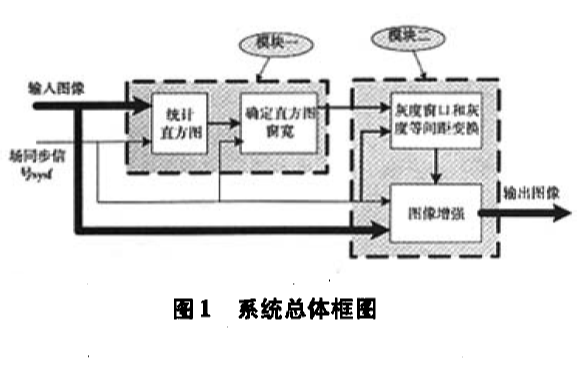

這種內存很容易實現數組類型的結構,而且這種內存被設計成雙端口方式,即可以用兩組獨立的地址數據總線來讀寫,因此可以用不到一塊的Block RAM 就實現256×24 這樣的高位寬計數器陣列來進行HDTV 視頻圖像的直方圖統計,如圖3 所示:

以Block RAM 的結構為核心,按照以下幾點來設計直方圖統計算法:

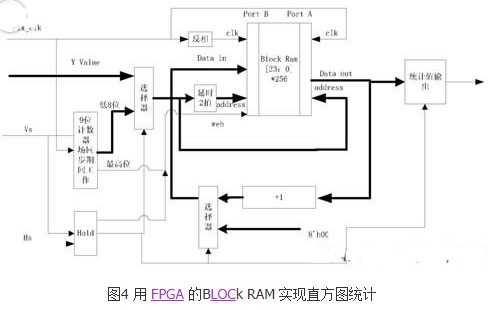

1. Block RAM 使用雙端口方式,端口A 用來將內存單元計數值讀出,端口B 將計數值加一后寫回該內存單元。

2. 內存的地址在像素有效時由像素灰度值選擇,在行同步期間不計數,在場同步期間使用一個遞增計數器在前256 個時鐘將統計結果輸出,在之后的256 個時鐘將RAM 塊清零。

3. 雙端口讀寫時鐘相位相差180 度,以避免雙端口讀寫沖突。

4. 數據的讀出、加一和寫入采用了流水線結構以提高性能,所以在地址控制上要進行適當暫存以保證數據同步。 圖4 為256 級灰度720p 視頻圖像直方圖統計的算法實現功能框圖:

結語

該算法借助FPGA 片上的高性能Block RAM(讀寫速度可以到200 兆以上),可以實現SMPTE 定義的從720p 到1080p 的各種HDTV 視頻圖像的實時直方圖統計,僅占用FPGA不到一百個邏輯單元和一塊Block RAM,是一種性價比較高的FPGA 實現直方圖統計的算法,而且該算法具有很好的通用性,可以應用到各種需要大量高位寬計數器的高速FPGA設計中。

-

FPGA

+關注

關注

1629文章

21729瀏覽量

603010 -

ARM

+關注

關注

134文章

9084瀏覽量

367390 -

數字電視

+關注

關注

3文章

321瀏覽量

45247

發布評論請先 登錄

相關推薦

FPGA圖像處理 直方圖統計并灰度拉伸 然后VGA顯示的問題

【干貨】基于FPGA的圖像處理(圖像增強)之直方圖均衡

基于FPGA的視頻圖像灰度信號直方圖均衡算法實現設計

MATLAB如何實現圖像增強灰度變換直方圖均衡匹配

如何使用FPGA實現實時圖像增強算法

剖析FPGA灰度直方圖線性拉伸

如何用FPGA的Block RAM性能實現HDTV視頻增強算法中灰度直方圖統計

如何用FPGA的Block RAM性能實現HDTV視頻增強算法中灰度直方圖統計

評論