Xilinx(賽靈思)是全球領先的可編程邏輯完整解決方案的供應商。Xilinx研發、制造并銷售范圍廣泛的高級集成電路、軟件設計工具以及作為預定義系統級功能的IP(Intellectual Property)核。客戶使用Xilinx及其合作伙伴的自動化軟件工具和IP核對器件進行編程,從而完成特定的邏輯操作。Xilinx公司成立于 1984年,Xilinx首創了現場可編程邏輯陣列(FPGA)這一創新性的技術,并于1985年首次推出商業化產品。目前Xilinx滿足了全世界對FPGA產品一半以上的需求。

自從Xilinx推出FPGA二十多年來,研發工作大大提高了FPGA的速度和面積效率,縮小了FPGA與ASIC(Application Specific Integrated Circuit的英文縮寫,在集成電路界被認為是一種為專門目的而設計的集成電路)之間的差距,使FPGA成為實現數字電路的優選平臺。現如今FPGA在各種電路設計中廣泛應用,如何對FPGA系統進行低功耗優化成為一個重要的現實問題。從最早的FPGA功耗模型的建,到較完善的FPGA功耗估算模型,再到現在功耗估算工具的出現,FPGA設計時對功耗的預估已經越來越準確,節約功耗的方法也越來越多樣降低 FPGA 功耗是縮減封裝和散熱成本、提高器件可靠性以及打開移動電子設備等新興市場之門的關鍵。Xilinx在提供低功耗 FPGA 解決方案方面一馬當先。本文說明如何應用計算機輔助設計(CAD,CAD-Computer Aided Design)利用計算機及其圖形設備幫助設計人員進行設計工作) 技術,如 Xilinx? ISE? 9.2i 軟件中采納的技術,來有效降低功耗。

ISE是使用XILINX的FPGA的必備的設計工具,它可以完成FPGA開發的全部流程,包括設計輸入、仿真、綜合、布局布線、生成BIT文件、配置以及在線調試等,功能非常強大。ISE除了我們功能完整,使用方便外,它的設計性能也非常好,拿ISE 9.x來說,其設計性能比其他解決方案平均快30%,它集成的時序收斂流程整合了增強性物理綜合優化,提供最佳的時鐘布局、更好的封裝和時序收斂映射,從而獲得更高的設計性能。先進的綜合和實現算法將動態功耗降低了10%。

CMOS(Complementary Metal Oxide Semiconductor,互補金屬氧化物半導體,電壓控制的一種放大器件。是組成CMOS數字集成電路的基本單元) 電路中的功耗由靜態(漏電)功耗和動態功耗兩部分組成。靜態功耗主要由晶體管的泄漏電流和FPGA偏置電流引起,它與工藝技術、晶體管特性、晶體管個數、采用的絕緣介質等因素有關,這些是由FPGA本身決定的,與電路活動無關。晶體管的泄漏電流主要由三部分組成:亞閾值漏電流、柵極漏電流和源漏極反偏漏電流動態功耗是指電容充放電功耗和短路功耗,是由電路的翻轉造成的,符合以下公式:

其中,Ci 表示信號 i 的電容;fi 稱為“開關活動率”,表示信號 i 上的躍遷速率;V 是電源電壓。

靜態功耗是指漏電流功耗,是電路狀態穩定時的功耗,其數量級很小,主要是亞閾值漏電流和柵極氧化層漏電流。截止 MOS 晶體管屬不完全絕緣體,允許其漏極與源極之間有亞閥值漏電流。柵極氧化層漏電流是由通過晶體管柵極流向其管體、漏極和源極的隧道電流所致。

工藝尺寸縮小(如近期采納 65 納米工藝的趨勢)意味著更低的電源電壓和更小的晶體管尺寸,致使導線長度縮短、電容量減小以及總體動態功耗降低。較小的工藝幾何尺寸還意味著較短的晶體管溝道和較薄的柵極氧化層,致使靜態功耗隨著工藝尺寸縮小而增加。

FPGA工作原理

FPGA采用了邏輯單元陣列LCA(Logic Cell Array)這樣一個概念,內部包括可配置邏輯模塊CLB(Configurable Logic Block)、輸出輸入模塊IOB(Input Output Block)和內部連線(Interconnect)三個部分。 現場可編程門陣列(FPGA)是可編程器件。與傳統邏輯電路和門陣列(如PAL,GAL及CPLD器件)相比,FPGA具有不同的結構,FPGA利用小型查找表(16×1RAM)來實現組合邏輯,每個查找表連接到一個D觸發器的輸入端,觸發器再來驅動其他邏輯電路或驅動I/O,由此構成了即可實現組合邏輯功能又可實現時序邏輯功能的基本邏輯單元模塊,這些模塊間利用金屬連線互相連接或連接到I/O模塊。FPGA的邏輯是通過向內部靜態存儲單元加載編程數據來實現的,存儲在存儲器單元中的值決定了邏輯單元的邏輯功能以及個模塊之間或模塊與I/O間的連接方式,并最終決定了邏輯單元的邏輯功能以及各模塊之間或模塊與I/O間的聯接方式,并最終決定了FPGA所能實現的功能,FPGA允許無限次的編程。

FPGA中的功耗

對于實現給定的邏輯電路而言,FPGA的可編程性和靈活性使其功耗效率比定制ASIC要低。目前,在集成電路界ASIC被認為是一種為專門目的而設計的集成電路。是指應特定用戶要求和特定電子系統的需要而設計、制造的集成電路。ASIC的特點是面向特定用戶的需求,ASIC在批量生產時與通用集成電路相比具有體積更小、功耗更低、可靠性提高、性能提高、保密性增強、成本降低等優點。FPGA的配置電路和配置存儲器占用硅片面積,致使導線延長和互連電容增加。在FPGA中,預制金屬導線段上附加的可編程布線開關產生互連,從而加重了信號產生的電容性負載。

雖然靜態電流與動態電流相比可以忽略不計,然而對電池供電的手持設備就顯得十分重要,在設備通電而不工作時更是如此。靜態電流的因素眾多,包括處于沒有完全關斷或接通的狀態下的I/O以及內部晶體管的工作電流、內部連線的電阻、輸入與三態電驅動器的上拉或下拉電阻。在易失性技術中,保持編程信息也需一定的靜態功率。抗熔斷是一種非易失性技術,因此信息存儲不消耗靜態電流。動態功耗是在時鐘工作且輸入正在開關時的功耗。對CMOS電路,動態功耗基本上確定了總功耗。動態功耗包括幾個成分,主要是電容負載充電與放電(內部與I/O)以及短路電流。如果器件驅動多個I/O負載,大量的動態電流構成總功耗的主要部分。

FPGA中的動態功耗大部分消耗在可編程布線架構中。同理,靜態功耗與晶體管總寬度成正比。FPGA的晶體管有相當一部分是互連架構,這是造成漏電流的主要因素。因此,互連架構應該是FPGA功耗優化的主要攻關目標。

當然,可以通過工藝技術、硬件架構或電路級修改來解決功耗問題。例如,Virtex?-5 FPGA 含有“對角線”互連資源,允許用較少的布線導體構成連接,從而減少互連電容。在晶體管級,Virtex-4 和 Virtex-5 兩種 FPGA 都是采用三柵極氧化層工藝技術來抑制漏電流。根據其速度、功耗和可靠性要求,可以為每個晶體管使用三倍氧化層厚度。與在標準 FPGA 架構中實現同樣功能相比,DSP 和處理器等硬 IP 模塊的數量激增和推廣使用也可以降低功耗。

也有可能,不必耗費巨資更改硬件,就可以降低功耗。可以通過功耗驅動的新型CAD算法和設計流程(如 ISE 9.2i 軟件中采納的算法和設計流程)來解決功耗問題。

ISE 9.2i 設計工具中的功耗優化

ISE 9.2i 軟件在布局布線中體現了功耗優化,并且通過一種后期布線技術來降低邏輯塊的內部功耗。

布局

Xilinx布局器中的核心算法采用了解析(數學)技術。這種算法以有重疊的初始設計布局開始,然后使用強行抽象法從高度擁擠區去除邏輯塊,最終形成可行的無重疊布局。一旦完成解析布局,便在已布局的設計上運行交換式局部優化,以進一步細化布局。本布局器中使用的傳統成本函數按以下公式考慮導線長度和時間:

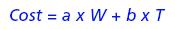

其中,W 和 T 分別是導線長度成本和時間成本,a和b是標量加權系數。a和b的值可以根據時間對導線長度的相對優先級設定。布局器的成本核算方案如圖1所示。

因為進行布局時還沒有實際線路,所以導線長度成本是依據導線長度估算。同理,時間成本是依據用戶提供的限制條件和連接延遲的估算值。為了優化功耗,我們用為成本函數增加功耗成分的方法擴展了解析布局和局部優化,如圖 1 右側所示。修改后的成本函數如下:

其中,Pdynamic是估算的動態功耗(如前述定義),c是標量加權系數。可以從仿真中提取信號開關活動率數據,然后將其提供給工具。反之,如果不提供任何開關活動率數據,則工具根據邏輯功能為初始輸入和后續輸出假定一個默認的開關活動率,并且將活動率推廣到其余信號。要獲得最佳結果,需要有用戶提供的開關活動率數據。

本文討論的布局和布線優化旨在降低互連架構中的功耗。

在布局過程中,信號的電容是未知的,因此必須估算。根據布局過程中已有的信號參數,我們建立了一個電容估算經驗模型:

其中,f表示普通數學函數;Ci是信號i的電容;FOi 是信號i的扇出數;XSi和YSi分別是布局中信號i的X跨度和Y跨度。這些參數獨立于架構,并且在布局過程中已經具備。

為建立此模型,我們提取了從Xilinx的客戶那里收集的一組設計中每個信號的電容、扇出數、X跨度和Y跨度。

然后,我們用最小平方回歸分析法將電容整理成模型參數的一個二次函數。就各種設計平均而言,該解析公式的誤差為30%。

布線

布線意思是元器件間導線連接的布置,先布好線,將導線穿過有電氣連接的引腳所在的孔,這樣可以在焊接元件的同時,實現元件間的連接。

一旦將邏輯塊分配到FPGA上的物理位置,我們就必須為各塊之間的連接進行布線。布線器采用一種協商擁塞布線算法,該算法在初始迭代中允許信號間短路。在后續迭代中,對短路的產生逐漸加大處罰,直到僅剩一個信號使用布線導體。對時間關鍵型連接布線的方式,應盡量縮短其延遲,這涉及到計算密集型RC延時計算。不過,大多數連接并非時間關鍵型。

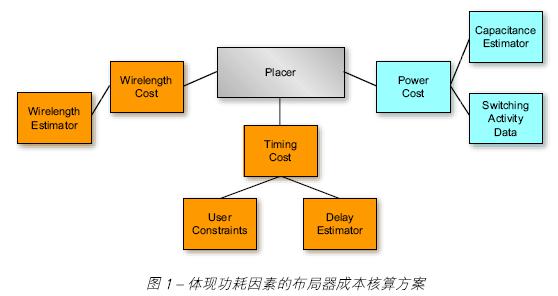

在功耗監控型布線器中,我們選擇優化這類非關鍵型連接的電容。為達到這一目的,我們針對非時間關鍵型連接修改了布線器的成本函數,以便考慮電容,這與上述根據其他因素(如估算的延遲或不足)的方法截然相反。為了解這種算法,請看圖2中的布線圖。

該布線圖中的每個節點表示一個布線導體或邏輯塊引腳,每條邊線表示一個可編程布線開關。布線器必須在源引腳和目標引腳之間選擇一條路徑。圖中各節點內部所示為該節點的原始成本和電容成本。若要盡量降低原始成本,源引腳和目標引腳之間的布線就應采納藍色路徑。然而,在功耗監控型流程中,布線器會使用綠色路徑,因為這條路徑的總體電容較低。

功耗監控型布局與布線的結果

我們使用傳統布局布線流程和上述功耗型流程兩種方法對一組工業設計進行了布局布線。這些設計的初始輸入附加一個基于線性反饋移位寄存器(LFSR-based)的偽隨機矢量生成器,從而增加了內置的自動輸入矢量生成功能。這樣,我們無需大量使用外部波形就能完成動態功耗的板級測量。

我們把這些工業設計映射到了Spartan-3、Virtex-4和Virtex-5器件中。結果顯示,動態功耗降低率對于Spartan-3 FPGA達14%,對于Virtex-4 FPGA達11%,對于Virtex-5 FPGA達12%。就所有設計平均而言,動態功耗降低率對于Spartan-3 FPGA為12%,對于Virtex-4 FPGA為5%,對于Virtex-5 FPGA為7%。就所有系列平均而言,速度性能下降在3%和4%之間,我們認為這樣小的性能損失在注重功耗的設計中是可以接受的。考慮到這些僅僅是軟件修改的初始結果,我們認為所取得的功耗效益是令人振奮的。

降低邏輯塊內部功耗

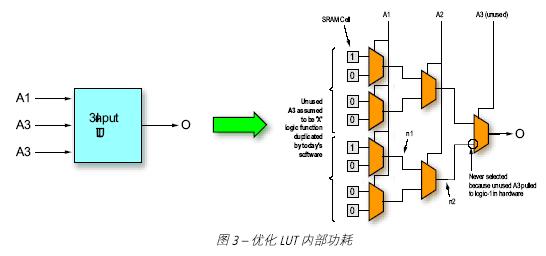

本文討論的布局和布線優化旨在降低互連架構中的功耗。我們還設計了一種降低邏輯塊內部功耗的方法,尤其是在未使用全部查找表(LUT)時,降低LUT中的功耗(圖3)。K輸入LUT是一種小存儲器,用區區幾K輸入即可實現任意邏輯功能。圖3所示為用一個假設的三輸入LUT(具有輸入A1、A2和A3)實現二輸入邏輯“與”功能的過程。多路復用器樹左側的LUT SRAM所示內容為邏輯“與”的真值表。

請注意,圖3中的輸入A3未使用。通常,未使用的輸入作為“無關項”處理,假設為0或1。所以,為了在圖3所示的情況下說明這一點,Xilinx 軟件在LUT SRAM存儲器內容的上下兩半部分中“重復”了該邏輯功能。客戶設計中經常出現未使用的LUT輸入,特別是Virtex-5設計,其中的LUT有六個輸入。

在Virtex-5硬件中,把未使用的LUT提升為邏輯 1;這一特性是我們優化的根本。如果把A3提升為邏輯1,那么對樹中最深層二輸入多路復用器的下半部輸入就永遠不會被選中。不過,因為邏輯功能在LUT存儲器內容的上下兩半部分重復,所以內部多路復用器節點n1和n2會根據信號輸入A1和A2的變化發生翻轉。這種翻轉白白耗費動態功率,因為n1和 n2上的躍遷永遠不會傳輸到LUT的輸出端。

這種優化需要在后期布線階段檢測未使用的LUT輸入,并且將LUT存儲器內容設置為邏輯0,從而在不破壞邏輯功能的情況下排除不必要的內部翻轉。回到圖3的例子,LUT存儲器內容的下半部分將設置為邏輯0。內部節點n1和n2上不會發生翻轉,因此不會由于對n1和n2充放電而消耗動態功耗。

為了評價在工業設計上進行的這一優化,我們進行了板級功耗測量,發現動態功耗節省了若干個百分點。這些結果說明大有前途,因為可以在布線后進行優化,不會造成面積或性能損失,從這種意義上講,這種優化是“免費”的。

結論

在用設計工具進一步降低功耗方面,存在著多種發展趨勢。在前端HDL(Hardware Description Language,是硬件描述語言。顧名思義,硬件描述語言就是指對硬件電路進行行為描述、寄存器傳輸描述或者結構化描述的一種新興語言)綜合中,FPGA可以借鑒ASIC領域中成熟的優化方法,如時鐘門控法和運算元隔離法。也可以使用針對FPGA的功耗優化方法,例如,將邏輯映射到可用的Block RAM(可以用作大型ROM)中,以此取代使用 LUT(顯示查找表(Look-Up-Table)簡稱為LUT,LUT本質上就是一個RAM。它把數據事先寫入RAM后,每當輸入一個信號就等于輸入一個地址進行查表,找出地址對應的內容,然后輸出) 和普通架構的方法。

將功耗監控型邏輯綜合和活動率驅動的工藝映射到 LUT 的方法在文獻中已有充分報道,這些方法將使Xilinx FPGA 大大降低功耗。在布局方面,電容估算精度的提高會更大幅度地降低功耗。

我們感覺特別有潛力的兩個方面是偽信號優化和漏電流優化。偽信號是由電路中路徑延遲不均衡所致在信號上發生的偽躍遷。這種躍遷是不必要的,但在動態功耗中卻占據著重要位置。抑制偽信號的CAD技術包括均衡路徑延遲或者沿偽信號最多的路徑插入寄存器。數字CMOS電路中的漏電路在很大程度上取決于電路使用的輸入狀態。因此,在CAD中減少漏電流的一種方法是自動修改電路,使其信號值在漏電流狀態下保持較長時間。

結果顯示,在通過ISE設計工具降低功耗方面已經取得長足的進步。對電子系統來說,減少功耗可以帶來很多好處,除了簡化系統的散熱處理及系統集成方面的工序、節約成本外,還能提高系統可靠性、降低熱噪聲干擾等。對便攜式儀器、野外工作儀器等電池供電的系統來說,還能延長電池壽命,減少更換電池的麻煩。在用軟件進一步降低功耗方面,我們認為前景一片光明。注重功耗的解決方案由功耗監控型CAD算法和功耗優化器件(如 Virtex-5 FPGA)組成,這一成功故事本身就頗為耐人尋味。低功耗軟硬件的不斷進步將為Xilinx FPGA打開進入新興功耗敏感型市場的大門。

-

FPGA

+關注

關注

1629文章

21729瀏覽量

603049 -

CAD

+關注

關注

17文章

1090瀏覽量

72452 -

可編程邏輯

+關注

關注

7文章

515瀏覽量

44083

發布評論請先 登錄

相關推薦

使用這些設計技巧降低FPGA功耗

《FPGACPLD設計工具──Xilinx+ISE使用詳解》

FPGA開發工具----ISE 開發工具、簡介、作用

ISE 12設計套件對FPGA生產力有什么影響?

ISE 12設計套件對FPGA有哪些影響?

通過動態開啟/關閉負載來降低功耗的參考設計

FPGA CPLD設計工具——Xilinx ISE使用

動態電壓與頻率調節在降低功耗中的作用

ISE設計工具實現算法將動態功耗降低10%

ISE設計工具實現算法將動態功耗降低10%

評論